# 1604 COMPUTER

Volume 2: PRINCIPLES OF OPERATION

INSTRUCTION BOOK

CONTROL DATA CORPORATION

MINNEAPOLIS, MINNESOTA

### 1604 COMPUTER

## Volume 2: PRINCIPLES OF OPERATION

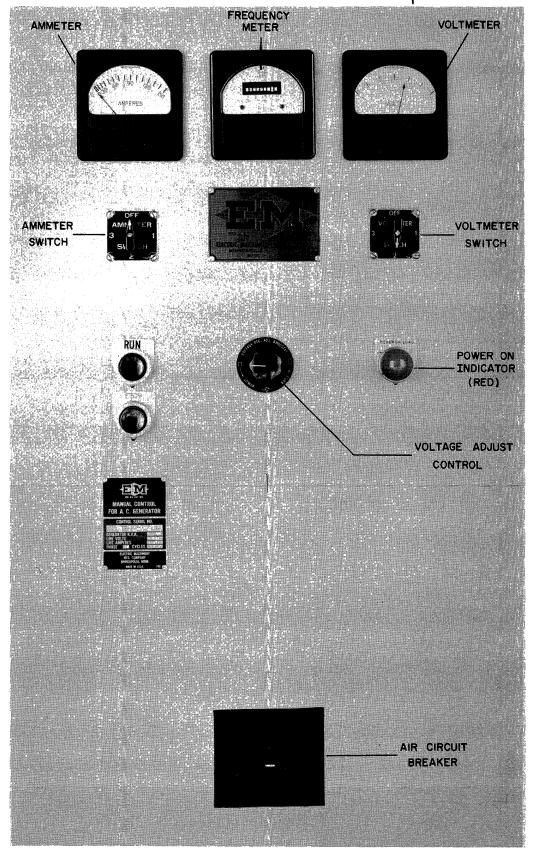

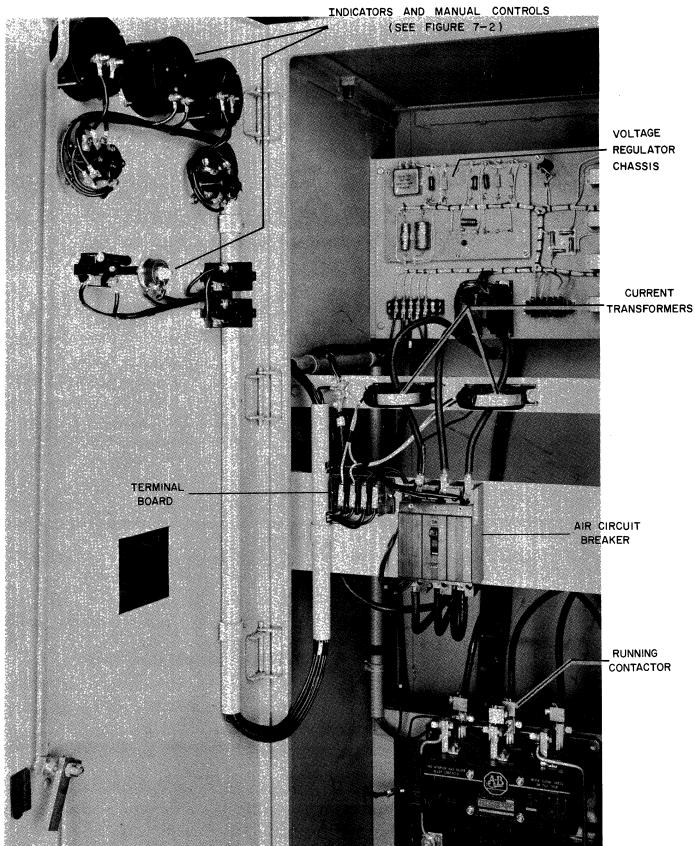

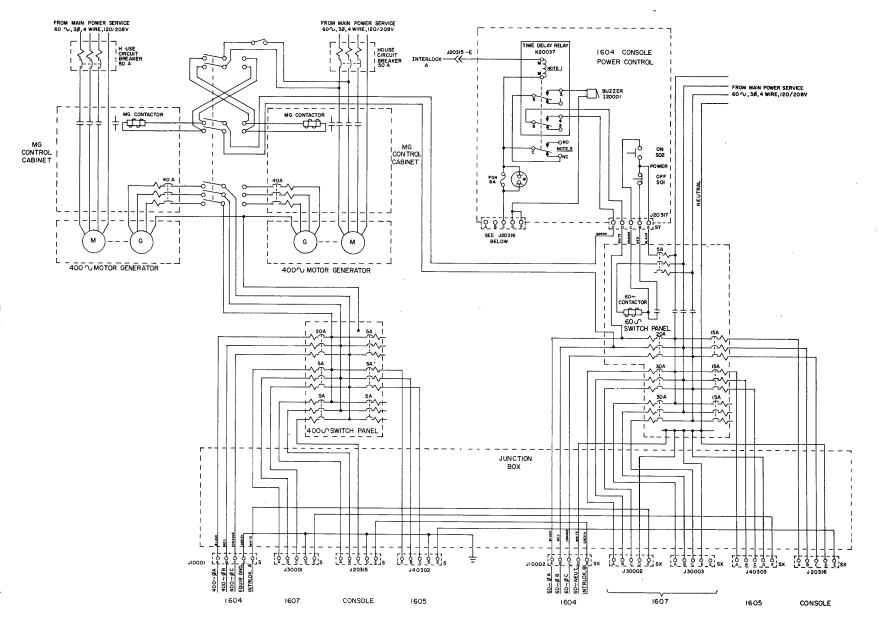

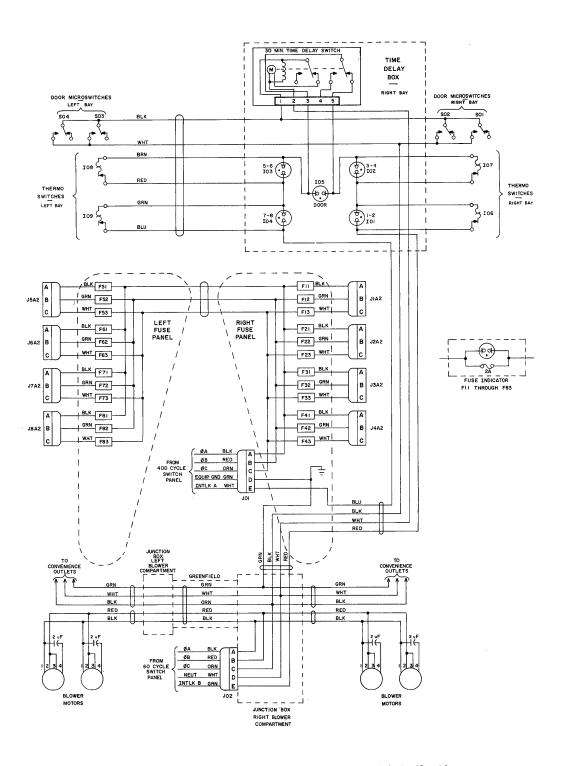

### **INSTRUCTION BOOK**

PUBLICATION 032a

#### **FOREWORD**

The instruction book treats only the basic units in a 1604 system (main computer and console). This volume takes up the logical principles of operation for the basic units. Other volumes in the instruction book are:

Vol. 1 Description and Operation

Vol. 3 Maintenance

Vol. 4 File of Equations

Vol. 5 Diagrams

Instruction books for other equipments in a 1604 system are:

1607 Magnetic Tape System (two volume)

1605 Adaptor

Information included herein is subject to correction and change.

For additional copies or other information write to:

Control Data Corporation Minneapolis 15, Minnesota

#### TABLE OF CONTENTS

| Chapter 1 Introduction                                                                                                                                                                | 1-1                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Physical Divisions of the Computer Over-all Analysis of Computer Number Systems Building Block Logical Equations Logic Diagram Symbols Typical Uses of Building Block Boolean Algebra | 1-2<br>1-2<br>1-9<br>1-13<br>1-22<br>1-24<br>1-27                         |

| Chapter 2 Control Section                                                                                                                                                             | 2-1                                                                       |

| Program Control Register Index Registers Address Buffer Register Program Address Register Control Sequences Static Control Main Computer Operating Controls Master Clock              | 2-3 2-11 2-12 2-17 2-17 2-20 2-72 2-83 2-90                               |

| Chapter 3 Arithmetic Section                                                                                                                                                          | 3-1                                                                       |

| Arithmetic Registers Basic Operations Addition Subtraction Shifting Multiplication Division Floating-Point Logical Product Register Sensing Pyramids Arithmetic Faults                | 3-1<br>3-6<br>3-9<br>3-13<br>3-15<br>3-15<br>3-26<br>3-31<br>3-42<br>3-45 |

| Chapter 4 Storage Section                                                                                                                                                             | 4-1                                                                       |

| Principles of Magnetic Core Storage Address Selection Bit Plane Circuits Storage Sequence Control Electronic Theory of Memory Circuits                                                | 4-3<br>4-13<br>4-23<br>4-30                                               |

### TABLE OF CONTENTS (CONT'D.)

| Chapter 5 Input-Output Section                                                                                                                                                                          |           |   | 5-1                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---|-----------------------------------------------------------|

| Communication Cable Groups Equipment Selection Computer Input Computer Output Input-Output Control Input-Output Instructions External Function Sequence Auxiliary Sequence Search and Transfer Sequence |           |   | 5-3<br>5-7<br>5-9<br>5-10<br>5-13<br>5-25<br>5-30<br>5-35 |

| Chapter 6 Console Input-Output E                                                                                                                                                                        | Equipment | • | <br>6-1                                                   |

| Modes for Handling Data External Functions Input Distributor Output Distributor Paper Tape Reader Paper Tape Punch Typewriter                                                                           |           |   | 6-2<br>6-3<br>6-8<br>6-10<br>6-12<br>6-17                 |

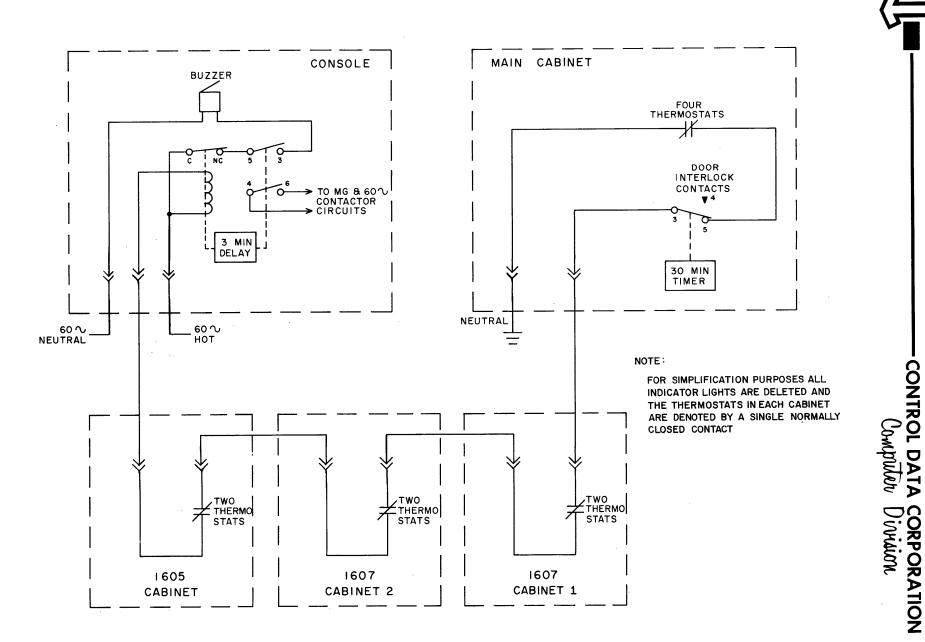

| Chapter 7 Power and Cooling                                                                                                                                                                             |           |   | 7-1                                                       |

| Motor Generator Main Power Distribution Main Cabinet Distribution Console Power Distribution Cooling System Protective Interlock System                                                                 |           |   | 7-1<br>7-6<br>7-6<br>7-9<br>7-11<br>7-12                  |

| Appendices                                                                                                                                                                                              |           |   |                                                           |

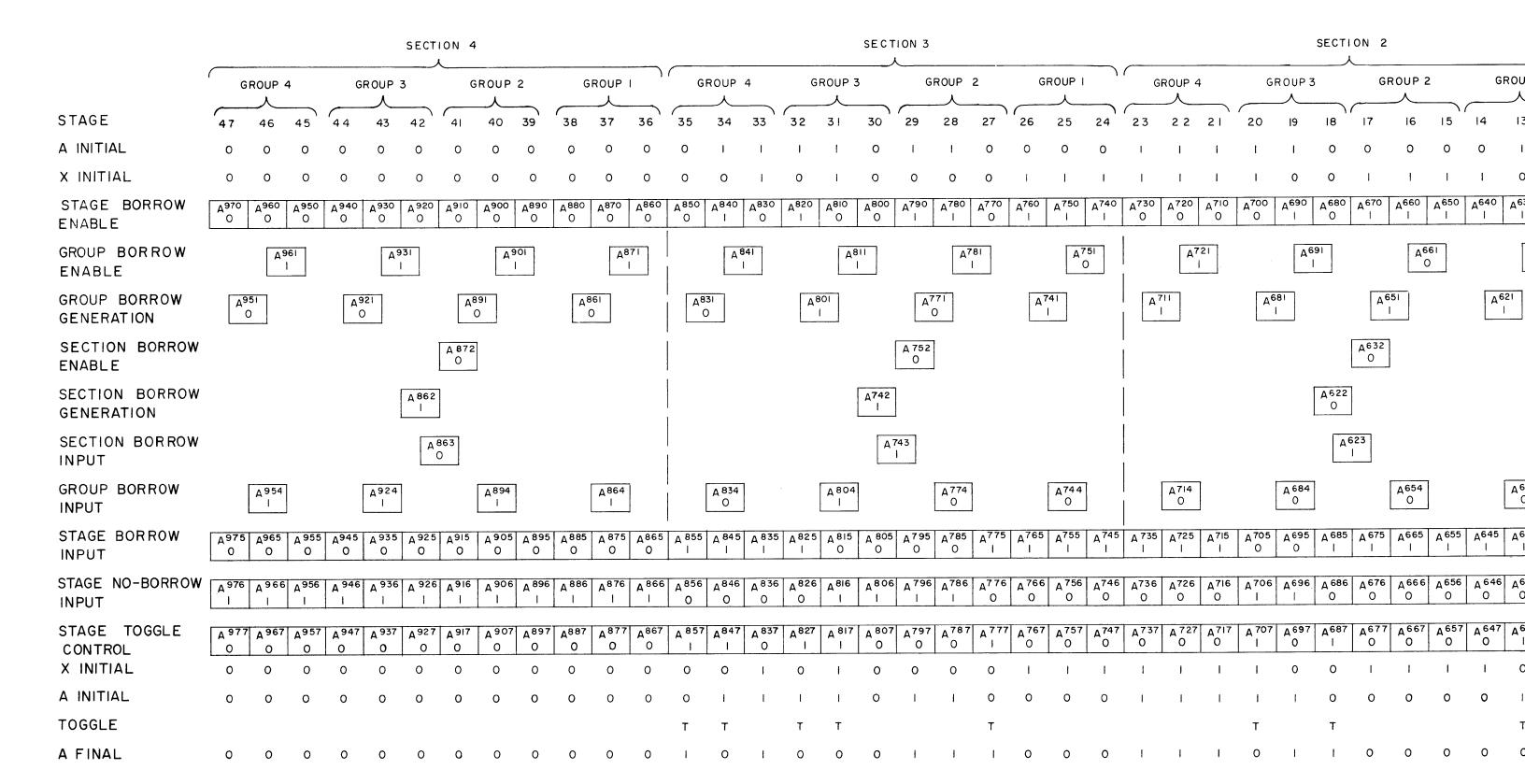

| <ul><li>A. Borrow Pyramid</li><li>B. Glossary of Terms</li><li>C. List of Instructions</li></ul>                                                                                                        |           |   | A-1<br>B-1<br>C-1                                         |

| List of Figures<br>List of Tables                                                                                                                                                                       |           |   | $\begin{array}{c} 1 \\ 4 \end{array}$                     |

#### CHAPTER 1

#### INTRODUCTION

The Principles of Operation volume of the 1604 instruction book describes the operation of the central computer and the external equipment at the console. Chapter 1 presents background material and acquaints the reader with the overall logical operation and structure of the computer. The next four chapters give a detailed analysis of the major sections of the computer: control, arithmetic, storage and input-output. The final two chapters deal with the console-mounted external equipment and the power system. Principles of operation of the 1605 Adaptor and the 1607 Magnetic Tape System are presented in separate volumes.

Principles of Operation emphasizes what circuits do logically rather than how they operate electrically in performing a function. The logical function of a type of circuit varies from instance to instance, but since the computer is constructed from a great number of electrically similar circuits and stages, a single examination of the electronics of the basic circuit will be sufficient. The small number of unique circuits are treated at the point where their logical use is discussed.

Reference material supplementing descriptions of computer operations is located in several sections of the instruction book:

- 1) File of Equations (volume 4) the complete and ultimate source of all information concerning the logic of the computer

- 2) Logic diagrams (volume 5) a graphic representation of the logical relationship given in the File of Equations; may be used as a detailed supplement to the logic discussed in this volume

- 3) Command timing charts (volume 3) for each instruction, a sequential list of the commands performed in the execution of the instruction

- 4) Octal operation code(appendix C) octal designation for each instruction

In addition, a glossary of abbreviations and terms is located at the back of this volume.

Abbreviations and terms that are employed with a special or unusual significance are defined there.

#### PHYSICAL DIVISIONS OF THE COMPUTER

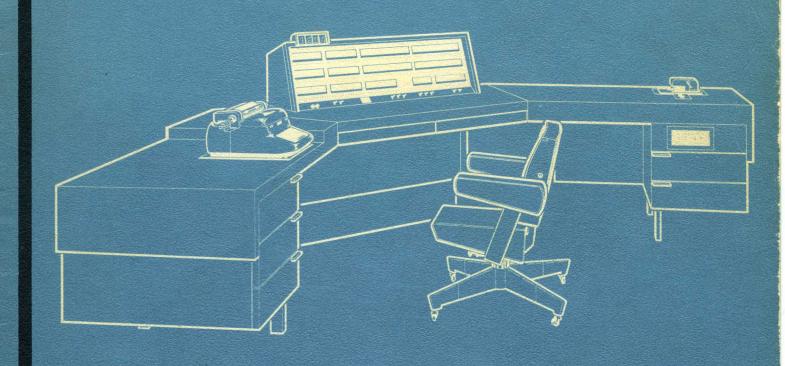

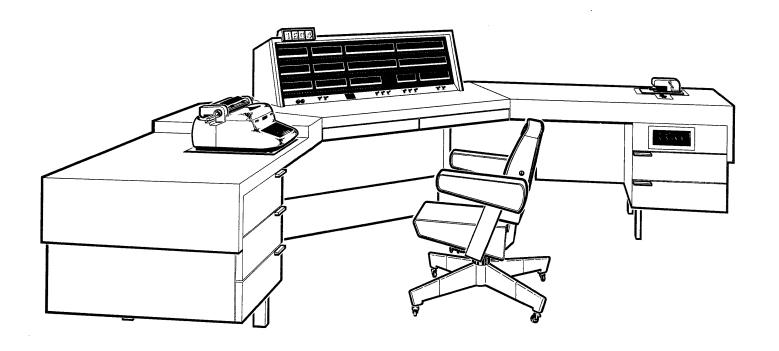

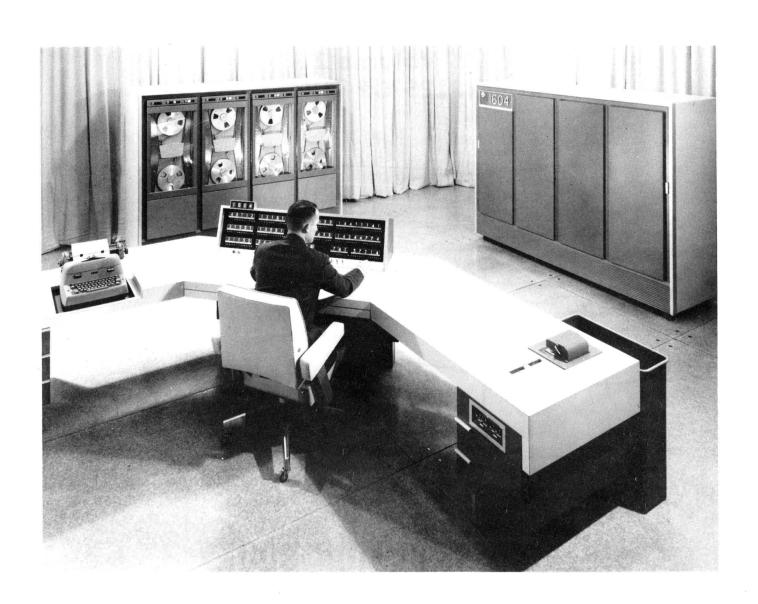

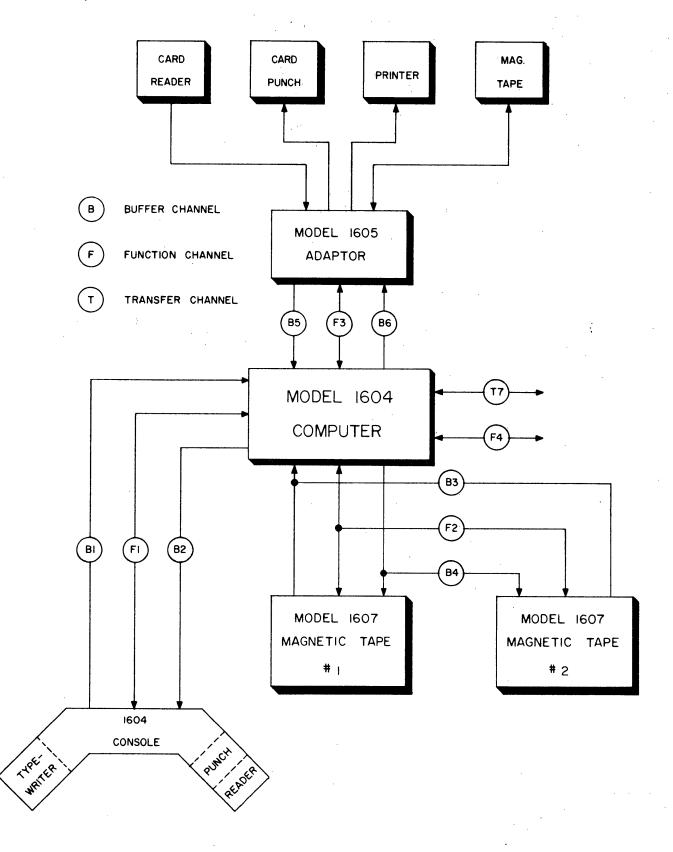

The 1604 Computer consists of the main computer cabinet, the console and the 1607 magnetic tape cabinet. A 1604 system (figure 1-1) may also have the 1605 Adaptor cabinet and the several IBM external equipments which are connected to the computer by means of the 1605. The latter provides data buffers and control circuitry for the IBM card reader and punch, line printer and tape units.

The main computer cabinet contains the computer proper and the control circuitry for the external equipment at the console. The console holds the operator's panel which provides indicators and operating controls; it also contains the monitoring typewriter, paper tape punch and paper tape reader. The 1607 magnetic tape cabinet houses four tape units and the associated control circuitry.

#### OVERALL ANALYSIS OF COMPUTER

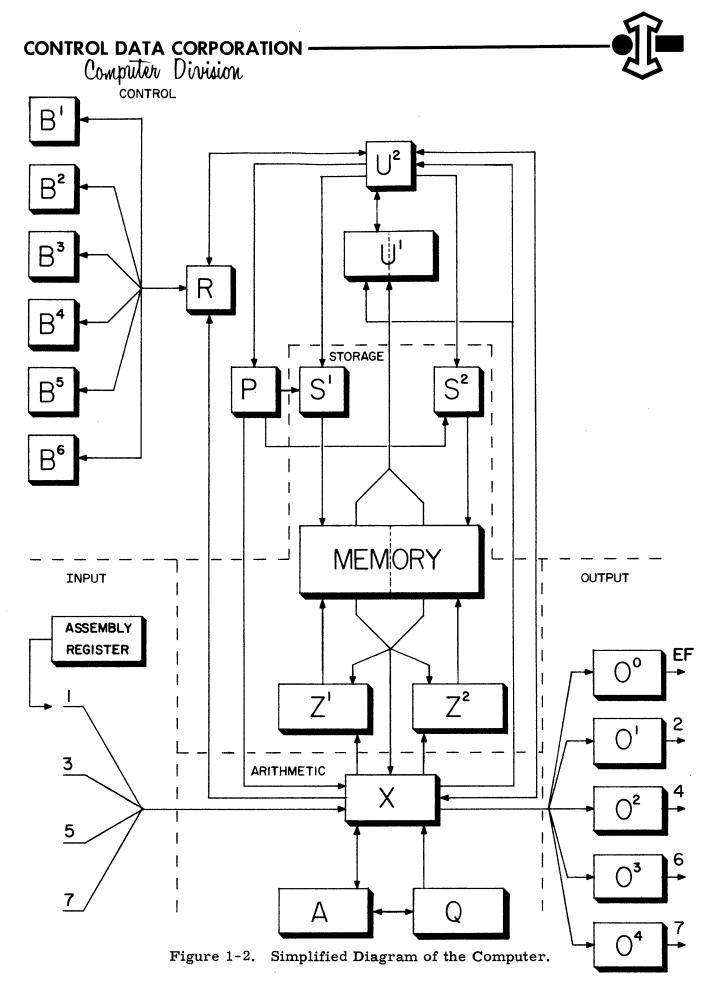

The computer can be divided functionally into four major sections: (1) input-output, which provides the means of communication between the computer and the various external equipments; (2) arithmetic, which performs the arithmetic and logical operations required for the execution of instructions; (3) storage, which provides internal storage for both data and instructions; and (4) control, which coordinates and sequences all the operations which

Figure 1-1. Typical 1604 System.

carry out the execution of an instruction.

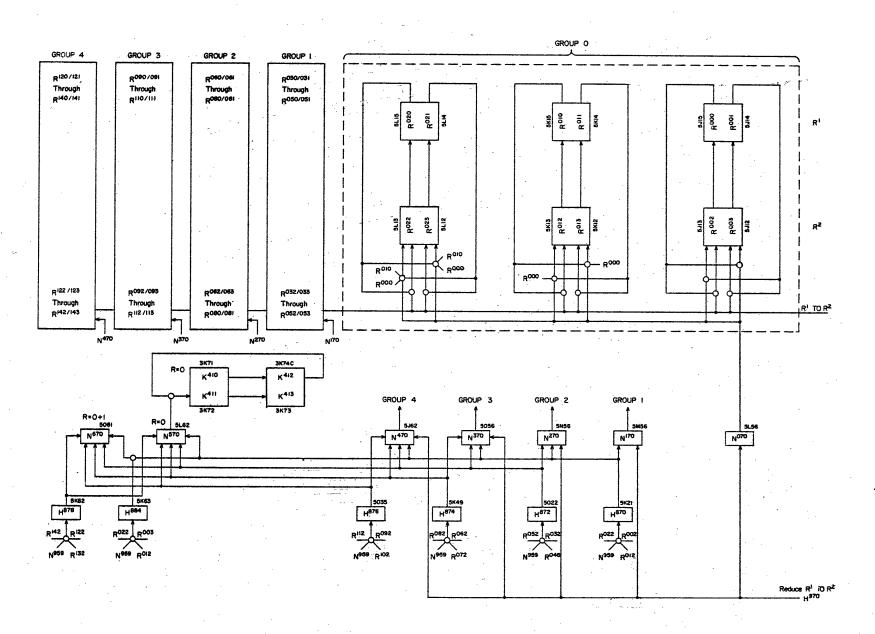

Figure 1-2 is a simplified diagram of the main computer. All the registers of the computer appear in this diagram; however, the control circuits such as sequences and individual control flip-flops are not shown. The following paragraphs describe each register briefly; next, the basic operations performed in the execution of a pair of typical instructions are discussed.

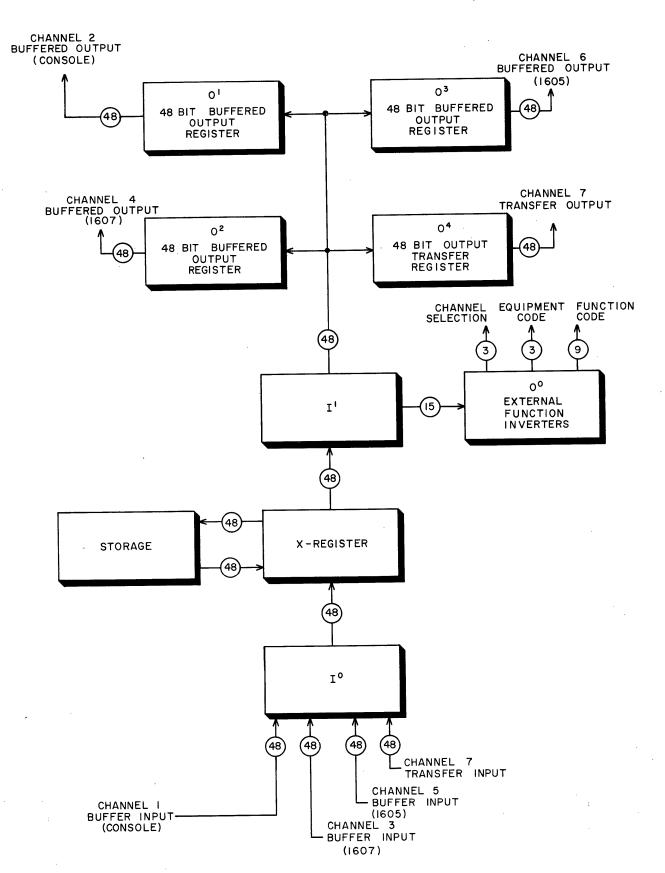

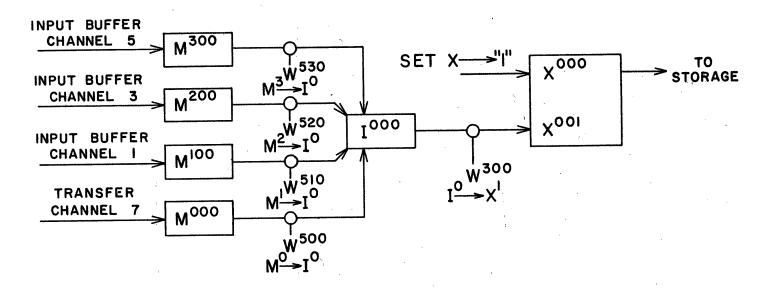

#### INPUT-OUTPUT SECTION

There are four input channels (1, 3, 5 and 7) which bring information into the computer. The X register receives the information from these channels. Channels 1, 3 and 5 are used for buffer communications; channel 7 is used in transfer type communication, a very high-speed method of exchanging data. Information from the input equipment on the 1604 console is always received via channel 1. Typically, channel 3 is connected to a 1607 Magnetic Tape System. Channel 5 provides another means of input which may be used by the 1605 Adaptor, a second 1607 or another equipment.

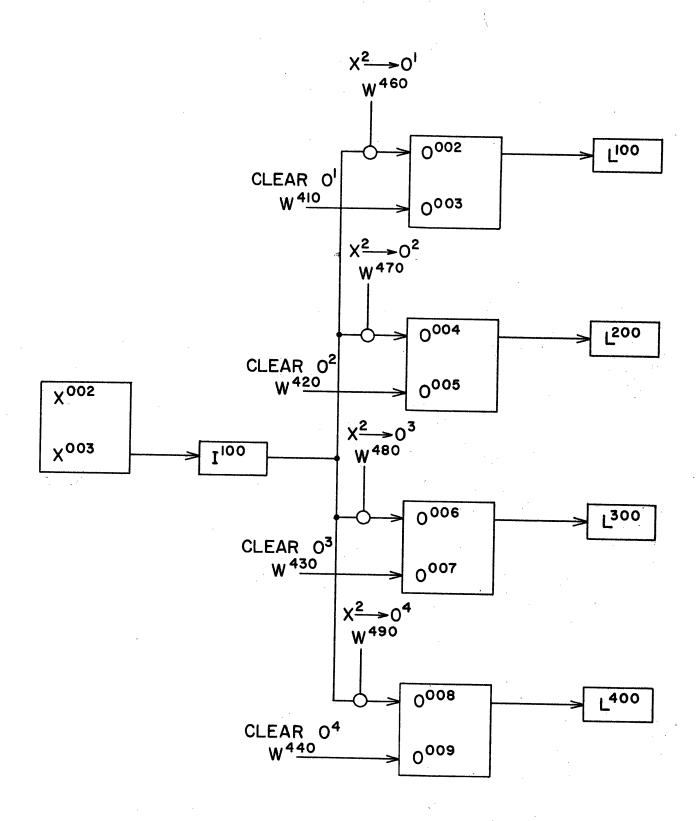

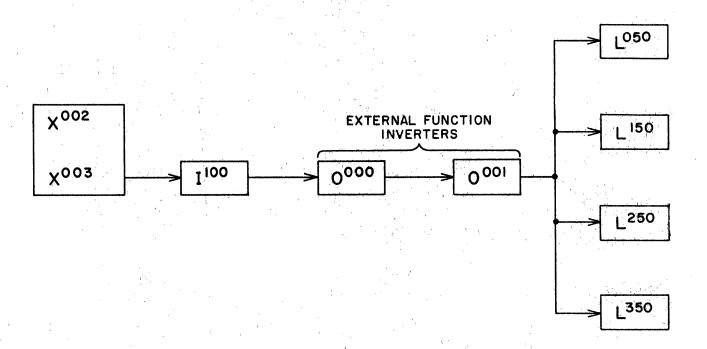

Output registers  $0^1$ ,  $0^2$ ,  $0^3$  and  $0^4$  are used to send information from the computer via output channels 2, 4, 6 and 7, respectively. Function inverters  $0^0$  are used to transmit control information to the various external equipments.

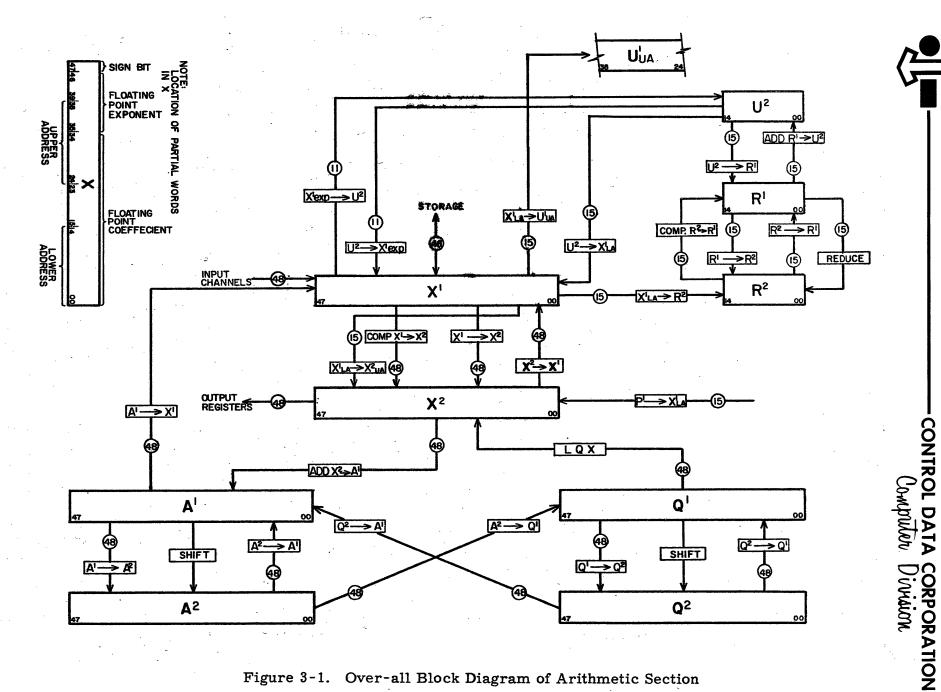

#### ARITHMETIC SECTION

The accumulator or A register is the principal arithmetic register since nearly all arithmetic and logical operations make use of A. This register has provisions for the parallel addition of X to its content, and can be shifted either separately or in conjunction with the Q register.

The Q register is an auxiliary arithmetic register; it assists the accumulator in the performance of the more complicated arithmetic operations. It is used in combination with the X register in the formation of logical products and can be shifted either separately or in conjunction with A.

The X, or exchange, register is used in arithmetic operations as well as in most data transmission between various sections of the computer.

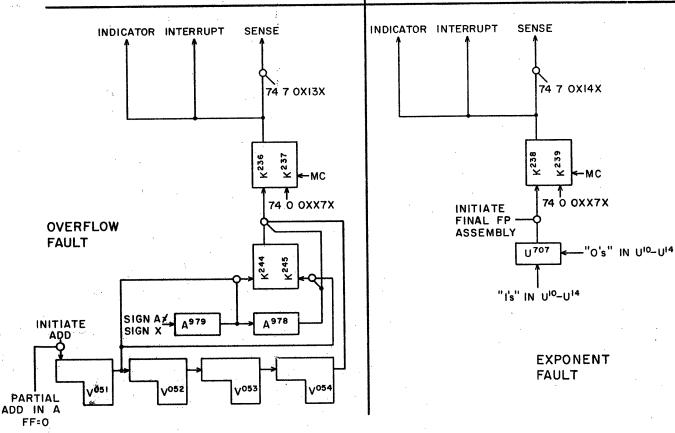

#### STORAGE SECTION

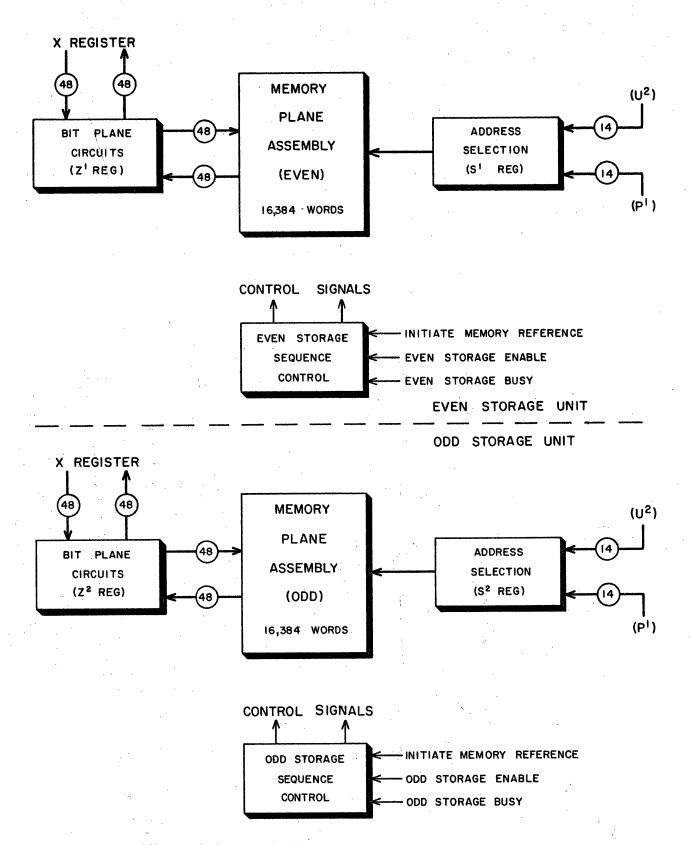

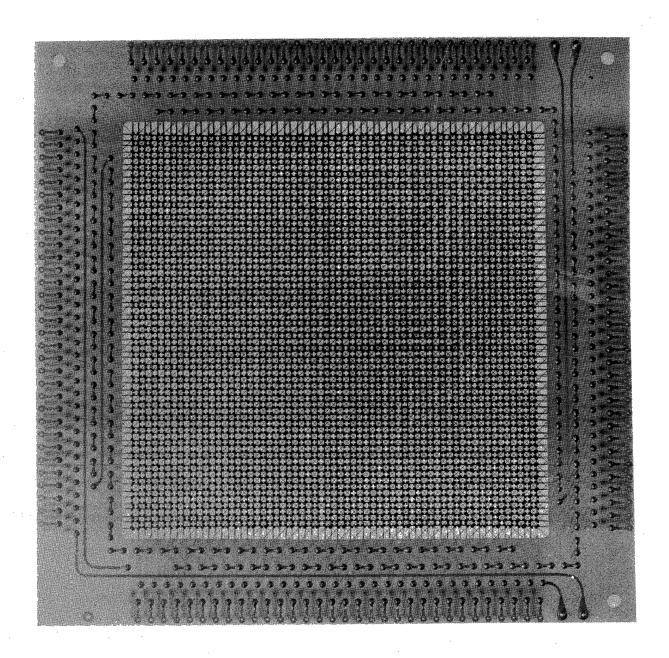

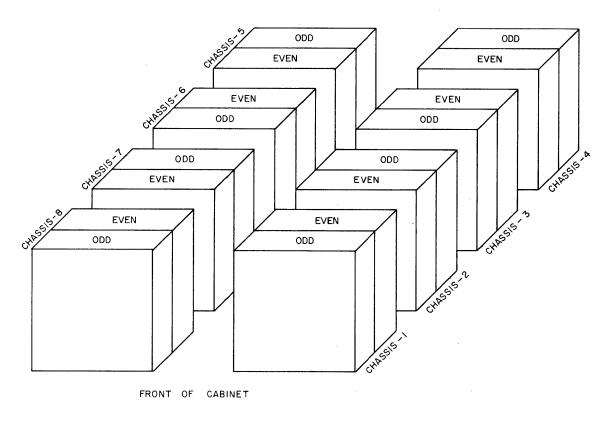

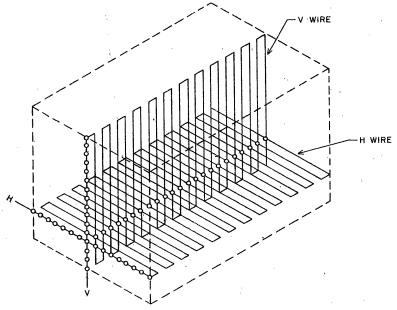

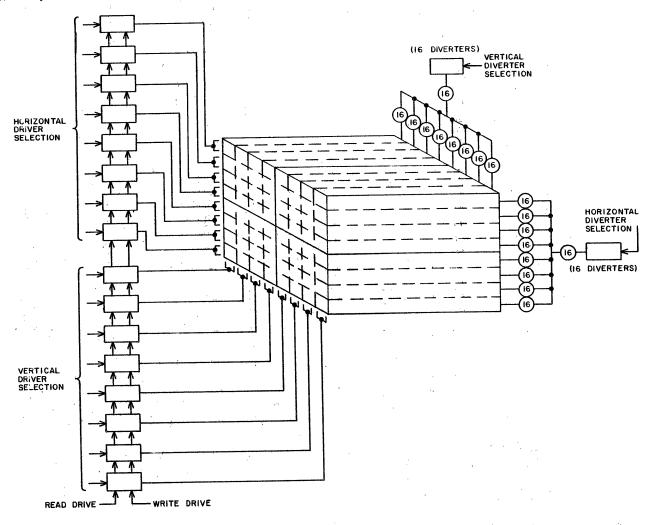

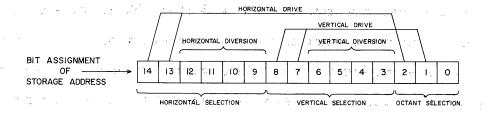

Two magnetic core storage units form the heart of the storage section. Each unit contains 16,384 locations or addresses for 48-bit words; thus, the total storage capacity is 32,768 words. One unit is called even because all locations denoted by even address words are contained in it; the other unit is called odd for similar reasons. Since the two units are independent, references to them can overlap considerably. Each unit has a storage address register into which is entered the address of the location from which a 48-bit word is to be taken or into which it is to be entered. The address register for the even storage unit is  $s^1$ , while  $s^2$  is the address register for the odd storage unit. In addition, each unit has a storage restoration register ( $s^2$  and  $s^2$ ) which holds the word to be written into a given storage location.

Words to be read out of either storage unit are entered into the X register, from which they are transmitted to the appropriate register. Words to be entered or written into a storage unit are transmitted from X to the appropriate Z register, which is then sampled to determine what is to be entered in the location.

#### CONTROL SECTION

The control section acquires an instruction from storage, then interprets it and sends the required commands to other sections. A 24-bit instruction is composed of three parts or codes, designated by the letters f, b and m. The upper six bits are the operation code (f), which specifies the operation to be performed. The operation code is designated by two octal digits; for example, 01 refers to the operation A Right Shift.

The next three bits are the designator (b), which ordinarily refers to the index (B) register whose content is to be added to the base execution address, the remaining 15 bits of the instruction. In most cases the base execution address (m) is used in specifying the storage location of the operand used in execution of the instruction. The content of the B register denoted by b, that is,  $B^b$ , is added to m to give the actual address of the operand. When b = 0, no addition takes place and m itself specifies the operand address. When b = 7, indirect addressing is used (see chapter 2). The sum of  $B^b$  and m is denoted by M.

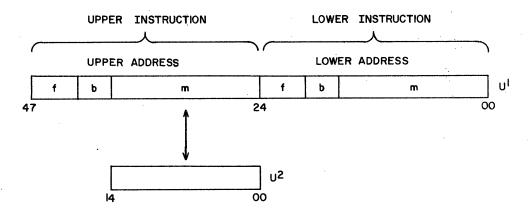

A program step is a pair of 24-bit instructions, which together occupy one storage location as a 48-bit word. The higher-order 24 bits of such a word are called the upper instruction and the remaining 24 bits are called the lower instruction.

The P register, the program address counter, provides continuity by generating in sequence the storage addresses at which the individual steps of the program are contained. At the completion of each step the count in P is advanced by one to specify the address of the next step. Jump instructions enter a new address in P to begin a new series of program steps.

The program control register,  $U^1$ , holds a program step while the two instructions contained in it are executed. The 48-bit instruction word is taken from the storage location specified by P and entered into  $U^1$ . The upper instruction is always executed first. Execution of the lower instruction follows, except when the upper instruction is a jump or provides

for the conditional skipping of the lower one.

The auxiliary program control register,  $U^2$ , is an accumulator used primarily in the modification of the base execution address by the addition to it of  $B^b$ .  $B^1$  through  $B^6$ , the six index registers, hold quantities used to modify the execution address of instructions.

The address buffer register, R, is used in transmissions to and from the B register. For instance, in the modification of the execution address,  $B^b$  is transmitted to R; R is then added to  $U^2$ , which holds the base execution address. The R register is also a counter used during the execution of several instructions.

#### EXECUTION OF TYPICAL PAIR OF INSTRUCTIONS

Address 00500 contains the following pair of instructions: upper instruction 14 Add and lower instruction 50 Enter Index; this pair is the next step to be performed in the program. The P register holds the address 00500. Because the lower bit is even, the address is in the even storage unit. The upper 14 bits of P are sent to  $S^1$ . The storage reference is initiated and the 48-bit word, the pair of instructions, is read from address 00500. The word is entered into  $U^1$ .

From this point on the operations of the computer are conditioned directly or indirectly by the 24-bit instruction in the upper half of  $U^1$ . This instruction, 14 Add, has as its purpose the addition of the quantity in the storage location specified by the execution address to the contents of A. The index code, b, and operation code, f, are now translated. Next,  $B^b$  is transmitted to R. At the same time the 15-bit base execution address is transmitted from  $U^1$  to  $U^2$ . The content of R is added to  $U^2$  to yield the execution address, M, which specifies the location of the operand.

Depending on whether the lowest bit of  $U^2$  is a "O" or a "1", the remaining 14 bits are transmitted to  $S^1$  or  $S^2$  in preparation for reading the operand which is to be added to A. The storage reference is initiated, and somewhat later the operand is entered into X.

The chief operation of the instruction adding X to A now occurs. All of the commands pertinent to the performance of this operation are conditioned by the operation code, f, which has the value 14. After the addition (the sum remains in A), the execution of the instruction is completed.

The computer is ready to execute the next instruction, which is presently contained in the lower 24 bits of U<sup>1</sup>. The upper half of U<sup>1</sup> is cleared and the lower half transmitted to the upper half, so that U<sup>1</sup> upper holds instruction 50 Enter Index. The purpose of this instruction is to place the 15-bit base execution address in index register b. Following translation of f and b, the base execution address is transmitted from U<sup>1</sup> to U<sup>2</sup>. Now U<sup>2</sup> is transmitted to R, and R in turn is transmitted to the B register specified by b. With this the execution of 50 is complete, and the next pair of instructions is read from storage in the manner described previously.

#### NUMBER SYSTEMS

The basic number system used throughout the 1604 is binary. In this system the only digits (commonly called bits) are "0" and "1". All numbers, regardless of magnitude, are expressed by means of these digits. Information to be entered into the computer is in binary notation; similarly, data sent out from the computer are in binary. All operations within the computer use the principles of binary arithmetic.

#### ONE'S COMPLEMENT NOTATION

One's complement notation is used to express negative numbers. To generate the one's complement expression of negative five, for example, each bit of the binary expression of positive five, 0101, is complemented. The result is 1010. The fact that the leftmost digit is 1 indicates that the quantity is negative; if the leftmost digit is 0, the quantity is positive.

One's complement notation is used for expressing negative numbers because of the ease with which complementing can be accomplished. The use of this notation requires that the accumulators (registers with provisions for addition of a quantity to their content) be the closed type. A closed accumulator provides for an end-around carry in the addition of a quantity (or borrow, if the accumulator is subtractive). An end-around carry (or borrow) is one which is generated in the highest stage and sent to the lowest.

#### TWO'S COMPLEMENT ARITHMETIC

The counters in the computer employ the principles of two's complement arithmetic. A counter is a register with provisions for increasing its content (if it is additive) or decreasing its content (if it is subtractive). A two's complement counter is <u>open-ended</u>; that is, there is no end-around carry or borrow. To illustrate the use of two's complement arithmetic in a counter, suppose that the content of a subtractive counter (such as R) is positive seven (0111) in binary and that this quantity is to be reduced by one. This is accomplished, in effect, by adding the two's complement expression of negative one, namely, 1111, to 0111 as shown below. The result is six.

0111 1111 0110

#### OCTAL NUMBER SYSTEM

Operation of the computer is described by the octal number system because three binary digits may be expressed by one octal digit, thus reducing the total digits involved by a factor of 3. The octal system is selected as a basis for obtaining shortened expressions for numbers because of the ease with which numbers can be converted from binary to octal and from octal to binary notation. Such conversions can be performed much more easily than conversions between binary and decimal numbers.

The following example shows how these conversions between binary and octal numbers are performed. The binary expression for thirty-eight decimal is 100110. To convert this expression to octal, separate it into groups of three digits each as follows: 100 110. Each group of binary digits is converted individually to the corresponding octal digit. Performing this conversion, 46 is obtained as the octal expression.

The conversion of a number in octal notation to binary is simply the reverse. To convert the octal expression 513 to its binary equivalent, each octal digit is converted individually to its binary equivalent, as shown below:

The binary expression for an octal digit must be filled out with 0's to make it three digits in length.

Octal notation is used to refer to the content of a register, the value of a control designator, addresses in storage and to the codes for instructions. The octal number system is not actually used in the operation of the computer.

#### ARITHMETIC PROPERTIES OF REGISTERS

Arithmetic operations are performed in five registers of the computer. Their arithmetic properties are listed in table 1-1.

TABLE 1-1. ARITHMETIC PROPERTIES OF REGISTERS

| Register                   | No. of<br>Stages | Modulus            | Complement<br>Notation | Sub. or<br>Add | Closed or open ended | Result:<br>Signed or<br>Unsigned |

|----------------------------|------------------|--------------------|------------------------|----------------|----------------------|----------------------------------|

| A accumulator              | 48               | 2 <sup>48</sup> -1 | one's                  | subtractive    | closed               | signed*                          |

| Q                          | 48               | 2 <sup>48</sup> -1 | one's                  |                |                      | signed                           |

| U <sup>2</sup> accumulator | 15               | 2 <sup>15</sup> -1 | one's                  | subtractive    | closed               | signed**                         |

| P                          | 15               | 2 <sup>15</sup>    | two's                  | additive       | open                 | unsigned                         |

| R                          | 15               | 2 <sup>15</sup>    | two's                  | subtractive    | open                 | unsigned                         |

<sup>\*</sup> The result of an arithmetic operation in A satisfies  $A \le 2^{47}$ -1 since A always is treated as a signed quantity. When the result in A is zero, it is always represented by 000...00 except when 111...11 is added to 111...11. In this case, the result is 111...11, which is commonly called "negative zero".

<sup>\*\*</sup>When  $U^2$  is used as an operand for an instruction, it is regarded as a signed quantity, and  $U^2 \le 2^{14}$ -1. When it is used to specify the address of an operand, it is regarded as an unsigned quantity, and  $U^2 \le 2^{15}$ -1.

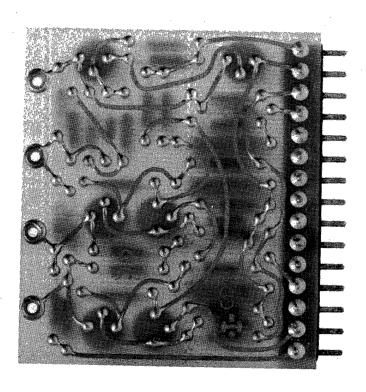

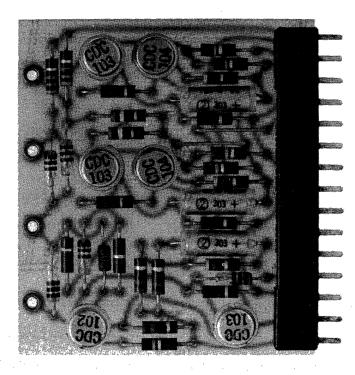

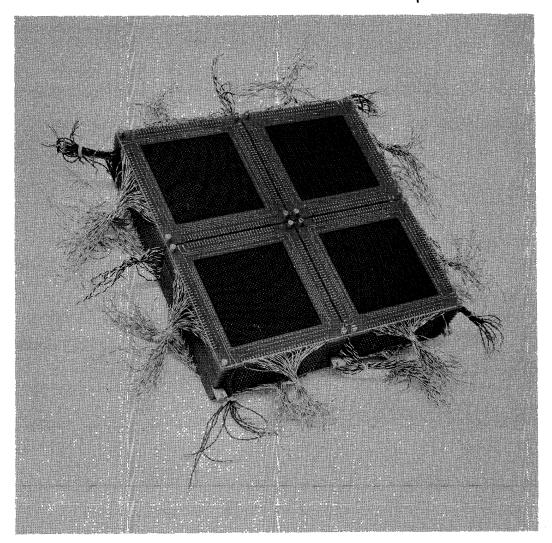

#### BUILDING BLOCK

The basic building block of the computer is a transistorized single inverter circuit. This circuit is used: (1) alone, as a single inverter; (2) in a pair to form a flip flop; and (3) in configuration of three to form a control delay. The major portion of the computer is constructed by interconnecting these circuits, which are packaged on 2 1/2 inch by 2 1/8 inch printed circuit cards (figure 1-3). Each card is equipped with a 15-pin male connector for plugging into the major equipment chassis.

In the following paragraphs the single inverter circuit, the flip-flop (FF) and the control delay are described. After a treatment of logical equations and logic diagram symbols (the two methods showing the connections between building blocks), some typical uses of the block in registers and counters are discussed.

#### ANALYSIS OF SINGLE INVERTER

Within the computer two signal levels are used, namely, -3.0 volts and -0.5 volts. The former represents the logical "1" and the latter represents the logical "0". The logical function of the single inverter is to invert one of these signal levels into the other. A -3.0 volt input to an inverter causes a -0.5 volt output, and vice versa. The inverter circuit permits the use of varying numbers of inputs and outputs.

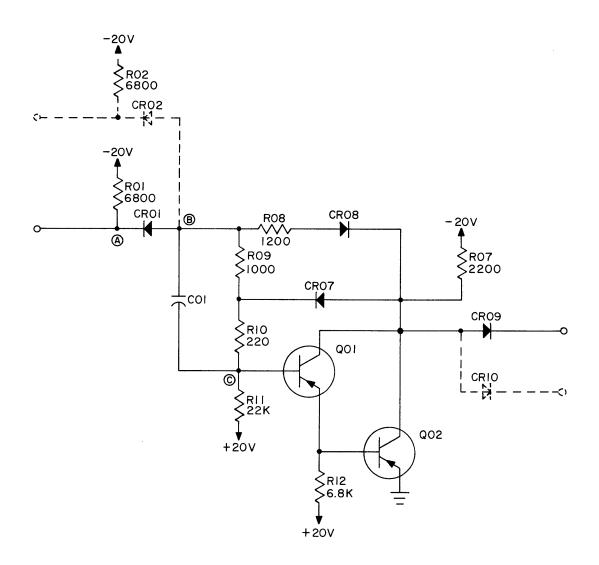

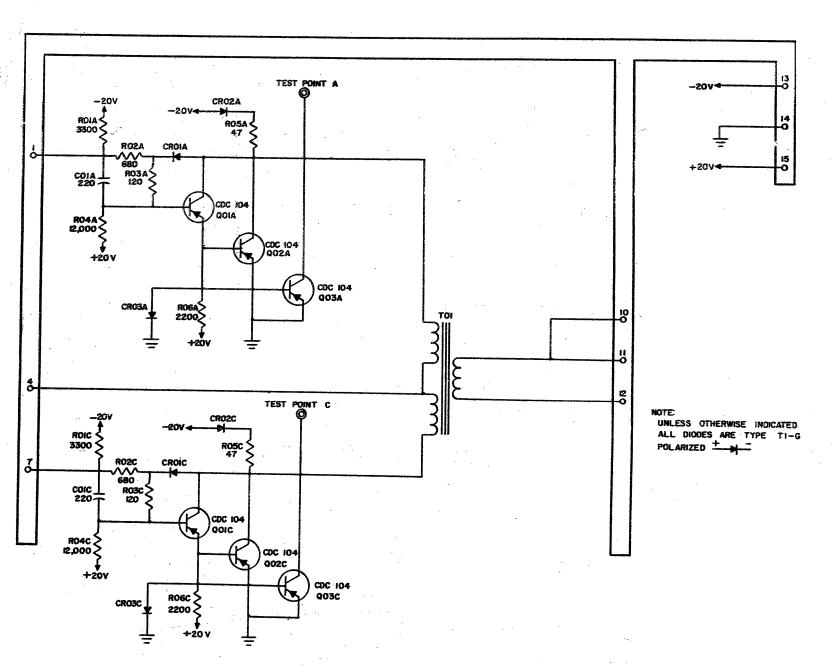

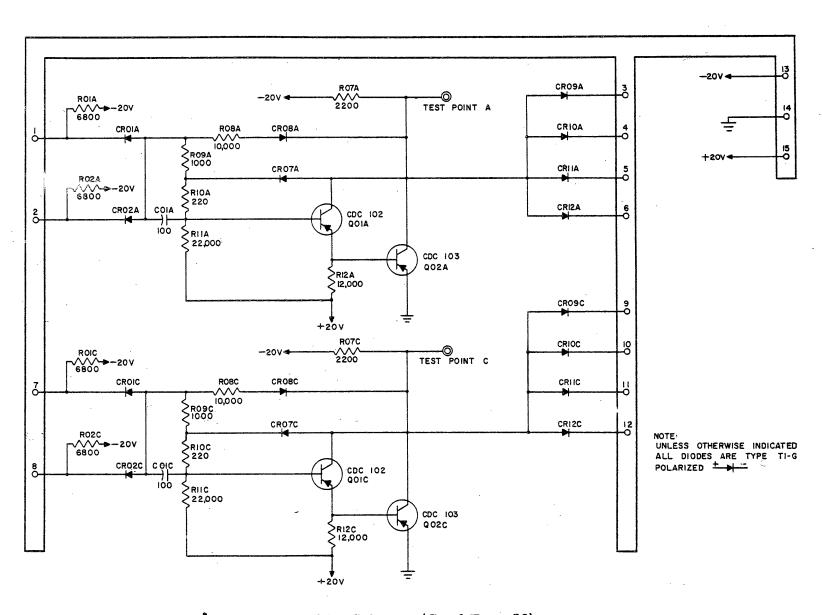

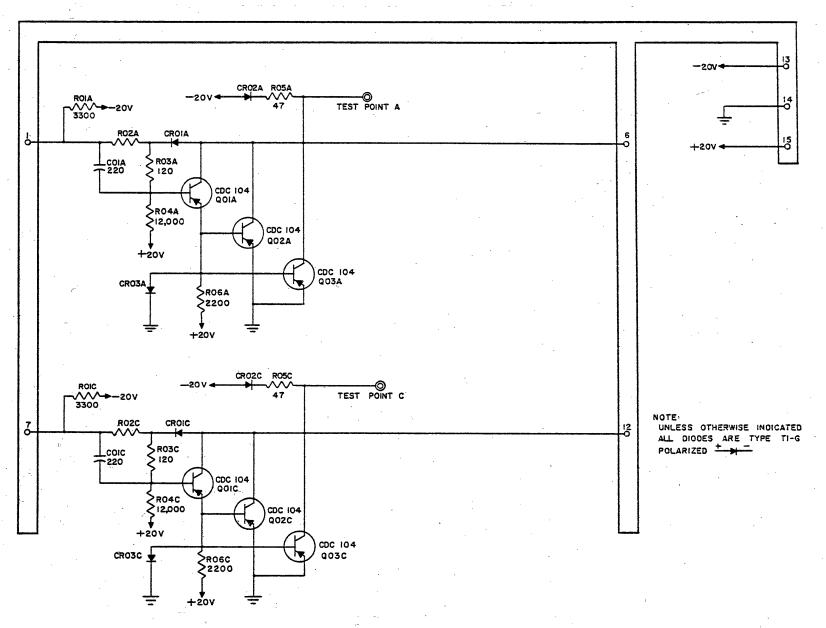

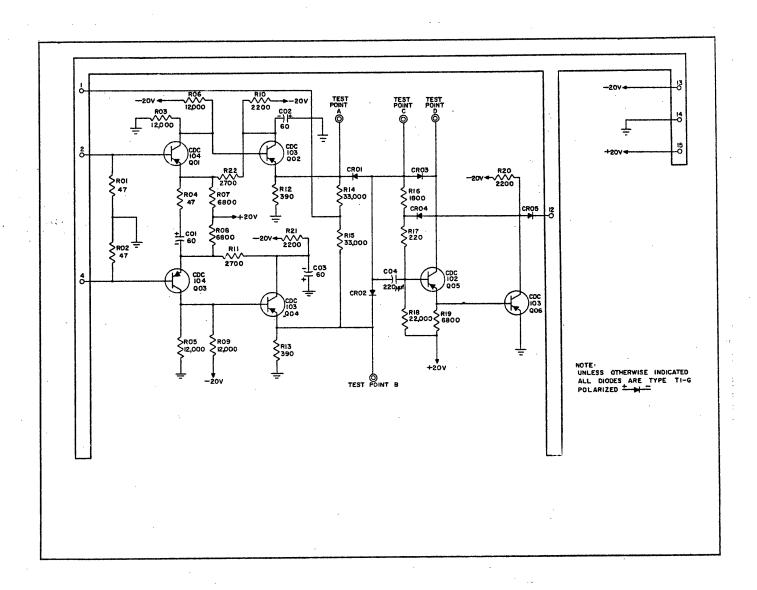

The standard inverter circuit is shown in figure 1-4. Transistor Q01 is connected as an emitter follower; Q02, as an amplifier. The collector circuits of the transistors are provided with two feedback loops which prevent the transistors from being driven to cutoff or saturation. As a result, switching from one state of conduction to the other is accomplished in a minimum time of 50 millimicroseconds and a maximum time of 100 millimicroseconds.

Figure 1-3. Typical Printed Circuit Card.

The input and output signal levels of the inverter circuit are -3.0 volts and -0.5 volts. An input signal is applied via isolation diodes CR01 or CR02 to a voltage divider network composed of resistors R07, R08, R09, R10 and R11. An input signal of -0.5 volts (point A) results in -1.5 volts at point B and 0.8 volts at the base of Q01 (point C). CR01 is thus biased 1 volt in the backward direction, which provides for noise suppression at the input of the inverter.

Capacitor C01, connected between CR01 and the base of Q01, provides rapid coupling of input signal changes to Q01, improving the switching time of the circuit.

Figure 1-4. Schematic Diagram of Standard Inverter Circuit.

Transistors Q01 and Q02 each provide beta current gains of approximately 100. Thus, loop gain of the two transistors is on the order of  $10^4$ . The collector current of  $Q^{01}$  and  $Q^{02}$  develops the output voltage across resistor R07. Output diode CR09 isolates the output line from the other output line connected to CR10.

The feedback loops which prevent transistors Q01 and Q02 from being driven to cutoff or saturation consist of diodes CR07 and CR08. The two feedback loops establish positive-going and negative-going limits for the base voltage swings of Q01. The positive-going limit allows a maximum transistor conduction that is less than saturation. Similarly, the negative-going limit fixes a minimum conduction for the transistors. When the transistors approach cutoff, their collectors approach -3 volts. The collector potential is coupled back to the base of Q01 through CR08, R08, R09 and R19. As a consequence the base of Q01 always is held at a sufficiently negative voltage to permit some minimum conduction of Q01 and thus Q02.

When the transistors approach saturation, the collectors approach 0 volts. The collector potential is coupled back to the base of Q01 through CR07 and R10. The base of Q01 is thus prevented from becoming so negative that saturation occurs.

#### FLIP-FLOP

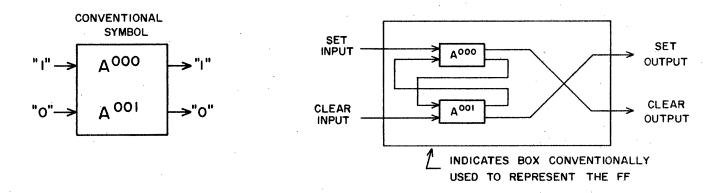

All short-term storage of information in the computer is accomplished by flip-flops (FFs); thus, the various registers such as A, X, Q, etc., consist of flip-flops. A FF is composed of two single inverter circuits interconnected as shown in figure 1-5 (each rectangle represents a single inverter). One of the inverters constitutes the set side of the FF; the other, the clear side. The FF is placed in the "1" state, i. e., set, by a set input that is "1". Conversely, it is placed in the "0" state, i. e., cleared, by a clear input that is "1". (Set and clear inputs are never "1" at the same time).

<sup>\*</sup> The beta current gain is the ratio of collector current to base current.

The storage capability of a FF means simply that it remains in a state that is indicative of the last "1" input received. Specifically, if a "1" pulse is present at the set input, then the output of inverter  $A^{000}$  (figure 1-5) becomes "0". This output is applied as an input to  $A^{001}$ , whose output then becomes "1". The output of  $A^{001}$  is fed back to  $A^{000}$ . Thus, when the set input returns to "0", the feedback connection between  $A^{000}$  and  $A^{001}$  permits the storage of the state to which the "1" pulse on the set input forced the FF. Should the clear input later receive a "1" pulse, the output of  $A^{001}$  becomes "0", and hence the feedback input to  $A^{000}$  is "0". Consequently,  $A^{000}$  furnishes a "1" output which is returned to  $A^{001}$  to replace the "1" pulse at the clear input.

When the FF is set,  $A^{001}$  has a "1" output, and  $A^{000}$  has a "0" output. Conversely, when the FF is cleared,  $A^{001}$  has a "0" output, and  $A^{000}$  has a "1" output.

The conventional square or box symbol for a FF is given in figure 1-5 to show the relationship between it and the inverter configuration which forms the FF. The square used on diagrams to represent the FF encompasses the crossover of outputs shown at the right of Figure 1-5.

Figure 1-5. Interconnection of Inverters to Form a Flip-flop.

#### CONTROL DELAY

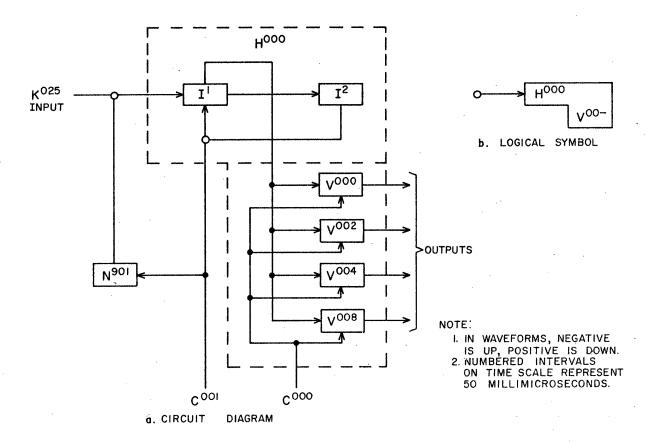

The single inverter and the FF described above are static, unclocked devices; that is, the output of the inverter is a steady-state inversion of its inputs. Likewise, once a FF is set, it provides a steady "1" from the set output and "0" from the clear output until it is cleared. However, an essential part of the internal operation of the computer is the occurrence of timed and properly shaped pulses. The function of control delays is to reshape signals and resynchronize them to furnish timed output signals. As its name indicates, the control delay inserts a controlled interval between the occurrence of its input and the occurrence of its output. This interval, or delay, is a single phase time of the master clock, namely, 0.2 microseconds. Furthermore, the minimum duration of the output pulse is 0.2 microseconds.

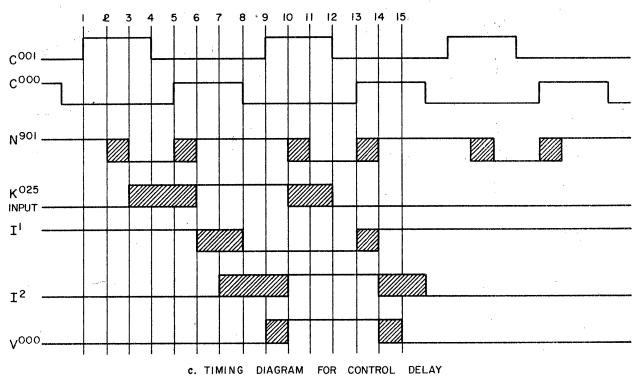

The two-phase master clock is essential in the operation of control delays. The outputs of the clock are two sine waves  $180^{\circ}$  out of phase. However, for the analysis of the control delay, which is the major application of the master clock, it is sufficient to understand that the clock furnishes rectangular waves of two phases, odd and even, as shown in figure 1-6c, where they are labeled  $C^{001}$  and  $C^{000}$ , respectively. The designations "odd" and "even" are given the clock phases because in the equation symbols (see page 23) for clocked circuits, the odd and even character of the third digit indicates the clock phase during which outputs from the circuit occur.

The control delay consists of a special FF (represented by an H equation symbol) and one or more inverters (represented by V or N symbols) connected to the "0" output of the FF (figure 1-6a and b). The special flip-flop has set inputs only, namely, those going to  $I^1$ . The logic inputs are always signals formed from other building blocks, one of which must be clocked. Feedback from  $I^2$  to  $I^1$  is gated by one of the clock phases, which is opposite to that applied to the output inverters. Thus, in figure 1-6a the odd phase ( $C^{001}$ )

Figure 1-6. Control Delay

gates the feedback as well as clocking the input from  $K^{025}$ . The even phase  $(C^{000})$  is fed to inverters  $V^{00-}$ .

During the odd clock phase ( $C^{001}$ ) the input signal is allowed to set the special FF ( $H^{000}$ ). The internal feedback also is gated during this clock phase so that the FF action extends or delays the original input signal. The even clock phase ( $C^{000}$ ) acts as a gate for the FF output. The duration of the output from inverter  $V^{000}$  is established by the even clock phase.

Waveforms for the various elements in the control delay are shown in figure 1-6c. For these waveforms it has been assumed that the internal switching time of each inverter is the minimum value of 50 millimicroseconds. Shaded areas indicate the variations in the occurrence of pulses due to external wiring delays. If, for example, these wiring delays were reduced to zero, then the output of N<sup>901</sup> would go to "0" at time 2 and remain so until time 5. On the other extreme, the delays could amount to a maximum of 50 millimicroseconds. In this case the output of N<sup>901</sup> would go to "0" at time 3 and remain so until time 6.

The time at which the output of I<sup>1</sup> may go to "0" varies over a 100 millimicrosecond period. Half of this period is due to the fact that delays introduced at N<sup>901</sup> are felt at I<sup>1</sup> also. Thus, if N<sup>901</sup> had the maximum delay but I<sup>1</sup> had zero delay, then the I<sup>1</sup> output goes to "0" at time 7 and remains there until time 13. If both N<sup>901</sup> and I<sup>1</sup> have the full delay, then the I<sup>1</sup> output is "0" from time 8 to time 14.

Assuming that capacitive wiring delays are zero, the leading edge of the output from  $V^{000}$  occurs at time 9 because the clock input to  $V^{000}$  (from  $C^{000}$ ) does not go to "0" until time 8. The logic input signal goes to "0" at time 10; however,  $C^{001}$  allows this signal to be replaced by gating the feedback from  $I^2$  to  $I^1$  until time 12. As a result, the original input signal is provided as an output from  $I^1$  until at least time 13.

The output of  $I^1$  encompasses the "0" portion of  $C^{000}$  (figure 1-6c). Since the output of  $V^{000}$  is actually the AND function of "not  $C^{000}$ " and "not  $I^1$ ", it is a "1" only while both are "0". Therefore, the time of occurrence and duration of the  $V^{000}$  output is determined by the period that  $C^{000}$  is "0".

The 0.2 microsecond delay produced by the control delay is shown in figure 1-6c by the relationship of the  $K^{025}$  and  $V^{000}$  waveforms. The input from  $K^{025}$  will go to "1" by time 6 regardless of the wiring delays. The result of this "1" input will be felt at the output of  $V^{000}$  by time 10. Thus the signal has been delayed by 0.2 microseconds.

#### AND CIRCUIT

The AND circuit is shown in figure 1-7. The diodes of an AND circuit are the output diodes of inverters. As many as four diodes, each from different inverters, may be connected in an AND. The common cathode connection of the diodes is tied to the input of an inverter, which furnishes the remaining elements of the AND circuit. In order for the output of the AND to be a "1", that is, at -3 volts, inputs A, B and C must all three be at -3 volts. If any of the inputs are at -0.5 volts, a "0", then the cathodes of all three diodes are held at this potential, as is the output at D.

Figure 1-7. AND Circuit.

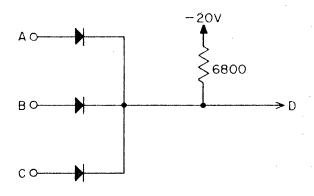

#### OR CIRCUIT

The OR circuit consists of components at the input of an inverter. The inverter shown in figure 1-4 has a two-input OR circuit, which involves R01, CR01, and R02 as well as voltage divider R09, R10 and R11 connected to -20 volts.

The potential at B, the common junction of the anodes of the OR diodes, is -1.5 (indicating a "0" in the circuit) only if both inputs at the cathodes of CR01 and CR02 are at -0.5 volts. If either OR input goes to -3.0 volts (a "i") then the potential at B is forced more negative than -1.5 volts. This more negative potential indicates a "1".

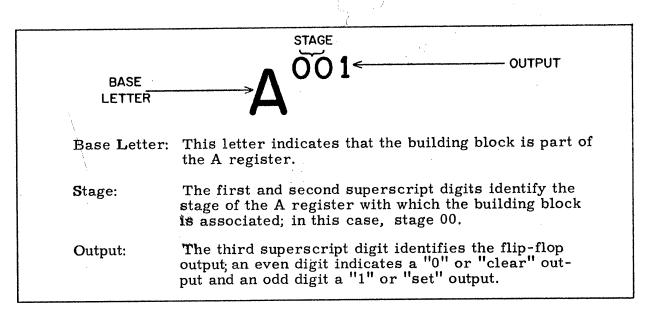

#### LOGICAL EQUATIONS

The logical interconnections of virtually all circuits in the computer are described by means of logical equations found in the File of Equations. As a preliminary step to formulating such equations, every circuit is assigned a unique symbol consisting of a base letter and a 3-digit superscript (figure 1-8).

The base letter of the symbol associates the building block with one of 26 major logical areas, such as the A register, B register, etc. The superscript digits provide a unique identification of the block within the area. In addition, the odd or even character of the third digit may identify the output clock phase of a circuit or set and clear sides of a FF.

These symbols are used in writing the equation, which are actually specialized instances of Boolean algebraic equations. An equation represents a single inverter with the exception of two classes of equations dealing with circuits in the storage section.

Figure 1-8. Typical Designation for a Building Block used in a Register.

From the logical viewpoint a single inverter is simply a circuit which provides as an output the inverted form of its input. Thus if any of the inputs to an inverter is a "1", its output is a "0"; conversely, its output is a "1" only if all of its inputs are "0". An equation is a logical representation of the inverter. For example:

$$K^{310} = K^{311} + V^{220} F^{585} K^{415} + V^{676} F^{940} J^{134}$$

The symbol on the left of the equal sign, called the subject term, denotes the inverter described by the equation. The expression on the right of the equal sign describes the logical configuration of the inputs.

The + sign represents the OR function or logical sum, while the absence of a sign between symbols represents the AND function or logical product. In the context of equations, the word "term" is used to designate a single symbol or group of symbols that is a logical product. The equation given above for inverter  $K^{310}$  has three terms, each representing an input to the inverter. Thus  $K^{310}$  has a "0" output if: (1)  $K^{311}$  is a "1"; (2) the AND function of  $V^{220}$ ,  $F^{585}$  and  $K^{415}$  is satisfied, that is; if each of them is a "1"; or, (3) the AND function of  $V^{676}$ ,  $F^{940}$  and  $J^{134}$  is satisfied, that is, each of them is a "1".

A two-phase master clock times computer operations. Circuits which receive timing signals from the clock are denoted by symbols with base letters H, V and N. The base letter of master clock symbols is C and of clock slaves, N<sup>9--</sup>. In these symbols (those with the base letters H, V, N, C and N<sup>9--</sup>) the even or odd character of the third superscript digit indicates timing relations. A C<sup>---</sup> or N<sup>9--</sup> symbol with an odd third superscript digit represents a circuit furnishing odd phase clock pulses; these symbols with even third superscript digits represent circuits furnishing even clock pulses. The H<sup>---</sup>, V<sup>---</sup> and N<sup>---</sup> circuits with an odd third digit provide output during the odd clock phase and receive input during the even phase. The same circuits with even third digits provide output during the even clock phase and receive input during the odd phase. Certain circuits (those with symbols having base letters of D, G, L, M and Y) are not represented by complete equation entries. In these circuits only inputs or outputs (but not both) are represented by equation symbols. Thus either the inputs or the outputs are missing from the entry.

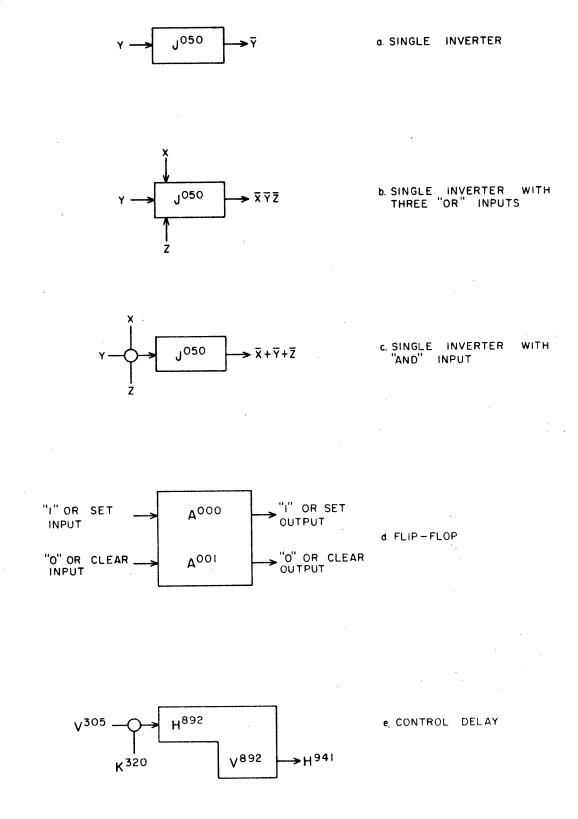

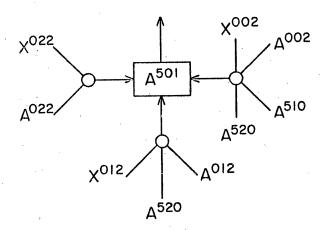

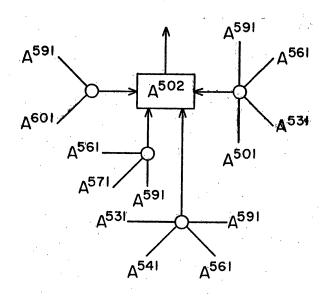

#### LOGIC DIAGRAM SYMBOLS

The logic diagrams use five basic symbols for representing the logical properties of circuit configurations in the computer. The shape of each symbol designates a basic logical function. Equation symbols (such as A<sup>001</sup>) enclosed by the diagram symbol provide a complete identification of the building blocks which are interconnected to perform the logical function. Inputs to the diagram symbol are identified by arrows; outputs, by the absence of arrows.

The symbols used in portraying the equations in diagrammatic form are shown and defined in figure 1-9. Since other logical elements such as the flip-flop and control delay are fundamentally configurations of two or more inverters (figure 1-9a), the diagrammatic symbols for these complex elements are formed from combinations of the inverter symbols. Each inverter rectangle contains the logical designation (such as  $J^{050}$ ) of the inverter.

Figure 1-9. Logic Diagram Symbols.

The diagrammatic form of the OR function is the representation of the inputs (by arrows) to the inverter (figure 1-9b). The AND function is represented by a small circle. An input to the AND is represented by a line; the output from the AND (which is input to a logical element such as an inverter) is represented by an arrow.

The flip-flop (FF) is a storage device with two stable states, designated "1" (or set) and "0" (or clear), and is composed of two inverters. The logical symbol (Figure 1-9d) is a square that is formed from the rectangles which represent the two inverters. The logical designations of the two inverters appear within the square. In a logic diagram, the inverter which receives the set input is at the top and the inverter which receives the clear input is at the bottom. Set outputs are received from the top inverter and clear outputs from the bottom. This diagrammatic convention simplifies the actual interconnection of the inverters, which is shown in figure 1-5.

With the exception of the FFs which form the B registers, the logical designation of the set side of a FF has an even last digit and the clear side of the same FF is designated by the next odd digit; for example, K<sup>942</sup> (set side) and K<sup>943</sup> (clear side).

A control delay (figure 1-9e) consists of an H part, which receives the input, and a V or N part, which provides the output. Control delays are clocked configurations which receive inputs during one clock phase and furnish a resultant output during the opposite clock phase.

#### TYPICAL USES OF BUILDING BLOCK

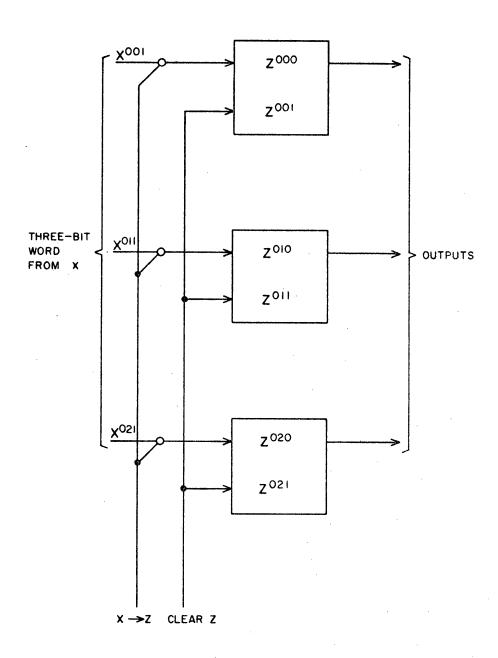

#### REGISTERS

A register is a device capable of storing a quantity or word. The register is made up of stages, each of which stores an individual bit of the word. A stage, therefore, may be considered as a bit register. There are two types of registers in the computer, single-rank and double-rank registers. The single-rank register consists of a single FF per stage and has storage properties only. The double-rank register consists of two FFs per stage and has either shifting, counting or complementing properties in addition to storage properties, depending upon the circuit connections.

A simple, three-stage, single-rank register is shown in figure 1-10. Each stage consists of a flip-flop and one or more input gates which allow the insertion of bits into the flip-flop. As shown in figure 1-10, the input gate of each stage of the Z register is enabled by the "1" output of the corresponding stage of the X register. The signal Clear Z prepares the Z register for receipt of a word by setting each of its stages to "0". The signal  $X \rightarrow Z$ , when applied to the input gates, sets those stages of Z to "1" which receive "1" enables from X.

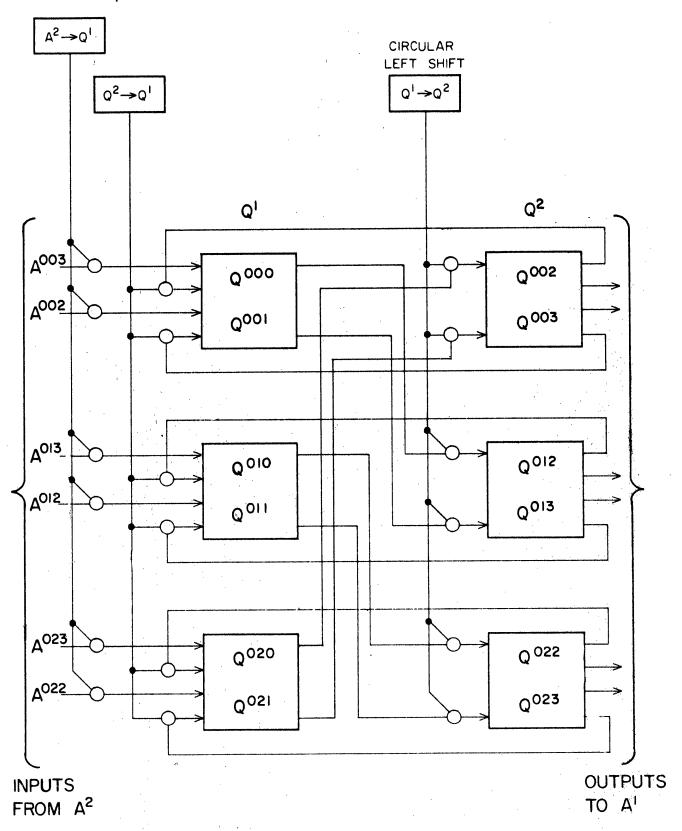

A simple three-stage double-rank register with shifting properties is shown in figure 1-11. The left-hand rank of this register is designated  $Q^1$  and the right-hand  $Q^2$ . The input word, from the  $A^2$  register, is initially entered into  $Q^1$  by the signal  $A^2 \rightarrow Q^1$ . The signal Circular Left Shift  $Q^1 \rightarrow Q^2$  next transfers the word to  $Q^2$  and shifts it left one bit. Thus, the bits in stages "0" and "1" of  $Q^1$  are transferred to stages "1" and "2", respectively, of  $Q^2$ , and the bit in stage "2" of  $Q^1$  is transferred to stage "0" of  $Q^2$ . Following this, the signal  $Q^2 \rightarrow Q^1$  transfers the word from  $Q^2$  to  $Q^1$  in preparation for the next shift. The word in  $Q^2$  is available as an output to the  $A^1$  register whenever the desired number of shifts have been performed.

Figure 1-10. Three Stage Single-Rank Register.

Figure 1-11. Three-Stage, Double-Rank Register with Shifting Properties.

#### COUNTERS

A counter is basically a double-rank register with circuitry which makes it possible to increase or decrease, by an increment, the quantity stored in the register.

#### Basic Three-Stage Counter

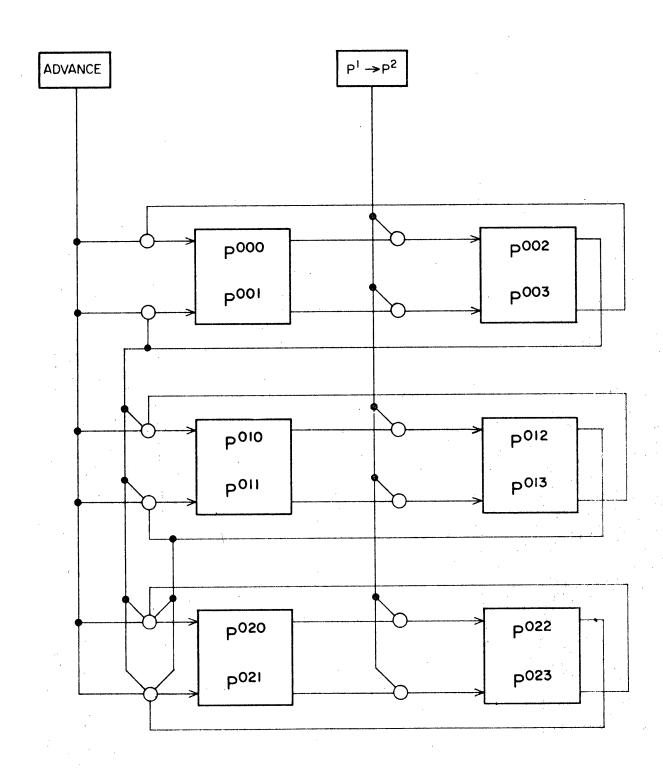

A three-stage counter circuit is shown in figure 1-12. This circuit is capable of additive counting; that is, from binary 000 through 111. Repetitive sequences consisting of the command Advance, followed by the command  $P^1 \rightarrow P^2$ , operate the counter.

The Advance command probes both the set ("1" side) and clear ("0" side) input gates of each FF of  $\mathbf{P}^1$ . These gates provide the additive counting feature of the circuit. Each set input gate is enabled by the "0" output of the corresponding FF of  $\mathbf{P}^2$ , and each clear input gate by the "1" output of the same FF. In addition, the pair of input gates to each FF is enabled by the "1" outputs of the lower-order FFs of  $\mathbf{P}^2$ .

To analyze the operation of the counter, assume that both ranks of each stage initially contain a "0". The counting sequence is listed in table 1-2. The first Advance command finds the input gate to  $P^{000}$  enabled and therefore enters the count 001 into  $P^1$ . The command  $P^1 \rightarrow P^2$  transfers the count to  $P^2$ . The following Advance command finds the input gates to  $P^{001}$  and  $P^{010}$  enabled and therefore enters the count 010 into  $P^1$ . The operation continues in this manner until the count 111 is reached. This is the highest count which the three-stage counter is capable of reaching. This is followed by a command sequence which returns both ranks to the count 000, in preparation for the next counting cycle.

Figure 1-12. Three-Stage Counter.

TABLE 1-2. COUNTING SEQUENCE FOR THREE-STAGE COUNTER.

| ,                                       |                   | $\mathbf{P}^1$    |                   |                 | $\mathbf{P}^2$    |                   |

|-----------------------------------------|-------------------|-------------------|-------------------|-----------------|-------------------|-------------------|

| Command                                 | $\mathbf{p^{02}}$ | $\mathbf{P}^{01}$ | $\mathbf{P}^{00}$ | P <sup>02</sup> | $\mathbf{P}^{01}$ | $\mathbf{P}^{00}$ |

| Initially                               | 0                 | 0                 | 0                 | 0               | 0                 | 0                 |

| Advance                                 | 0                 | 0                 | 1                 | 0               | . 0               | 0                 |

| $P^1 \rightarrow P^2$                   | 0                 | 0                 | 1                 | 0               | 0                 | 1                 |

| Advance                                 | 0                 | 1                 | 0                 | • 0             | 0                 | 1                 |

| $P^1 \rightarrow P^2$                   | 0                 | 1                 | 0                 | 0               | 1                 | <b>O</b> t        |

| Advance                                 | 0                 | 1                 | 1                 | 0               | 1                 | O                 |

| $\mathbf{p}^1 \rightarrow \mathbf{p}^2$ | 0                 | 1                 | 1                 | 0               | 1                 | 1                 |

| Advance                                 | 1                 | 0                 | 0                 | 0               | 1                 | 1                 |

| $P^1 \rightarrow P^2$                   | 1                 | . 0               | 0                 | 1               | 0                 | 0 0               |

| Advance                                 | 1                 | 0                 | 1                 | 1               | 0                 | 0                 |

| $P^1 \rightarrow P^2$                   | 1                 | 0.                | 1                 | 1               | 0                 | 1                 |

| Advance                                 | 1                 | 1                 | 0                 | 1               | ۵                 | 1                 |

| $P^1 \rightarrow P^2$                   | 1                 | 1                 | 0                 | 1               | 1 -               | 0                 |

| Advance                                 | 1                 | 1                 | 1 .               | 1               | 1                 | 0                 |

| $P^1 \rightarrow P^2$                   | 1                 | 1                 | 1                 | 1               | <b>1</b>          | 1                 |

| Advance                                 | 0                 | 0                 | 0                 | 1               | 1                 | 1                 |

| $P^1 \rightarrow P^2$                   | 0                 | 0                 | 0                 | 0               | 0                 | 0                 |

### Multistage Counters

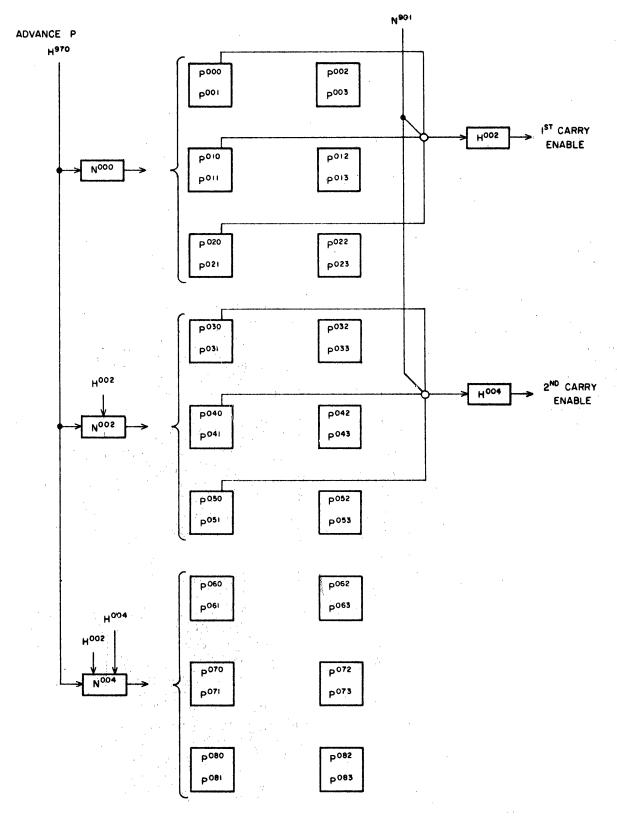

Multistage counters are formed by interconnecting several three-stage counter units, as shown in figure 1-13. A Carry Enable, indicating the count 111, is obtained from each unit. Such enables condition the advancing of the higher-order units. The Advance command is applied to a higher-order unit only if the appropriate enables are obtained from all the lower-order units. Thus the third unit is advanced by one count each time the two lower-order units change from "1's" to all "0's".

The counting sequences for multistage counters are identical to those listed in table 1-2, except for the larger numbers involved.

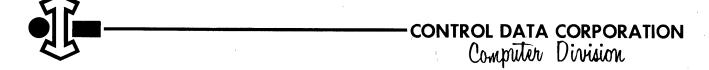

For the sake of convenience in drawing, the H and N parts of the control delay have been shown separately in figure 1-13. A brief analysis of the conditions required for advancing the third group will aid in understanding the operation of the counter. Advancing this group requires a "1" output from  $N^{004}$ ; therefore all four inputs to  $N^{004}$  must be "0". The occurrence of the ADVANCE command causes the output of  $H^{970}$  to be "0". The output of  $H^{002}$  is "0" when the three stages of the first group are each "1". Similarly, the output of  $H^{004}$  is "0" when the three stages of the second group are each "1". (The clock input from  $C^{000}$  is "0" during every odd clock phase.)

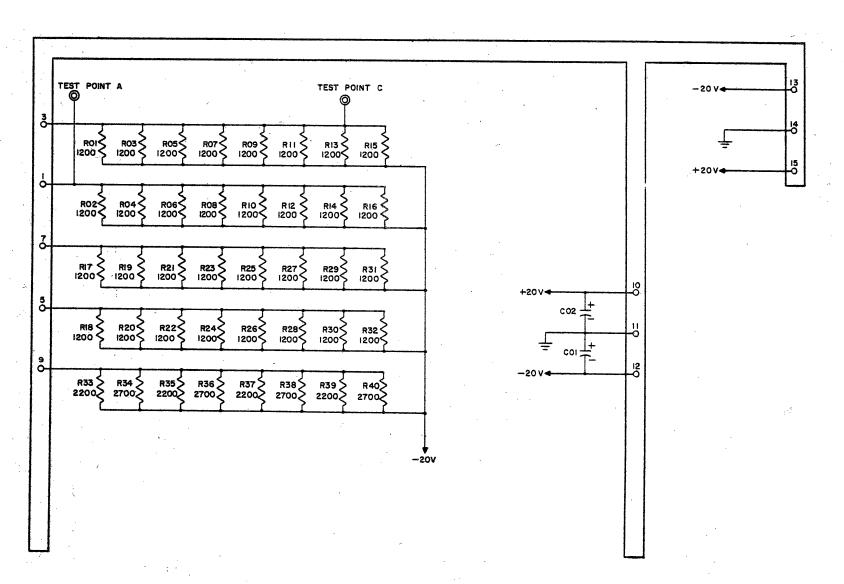

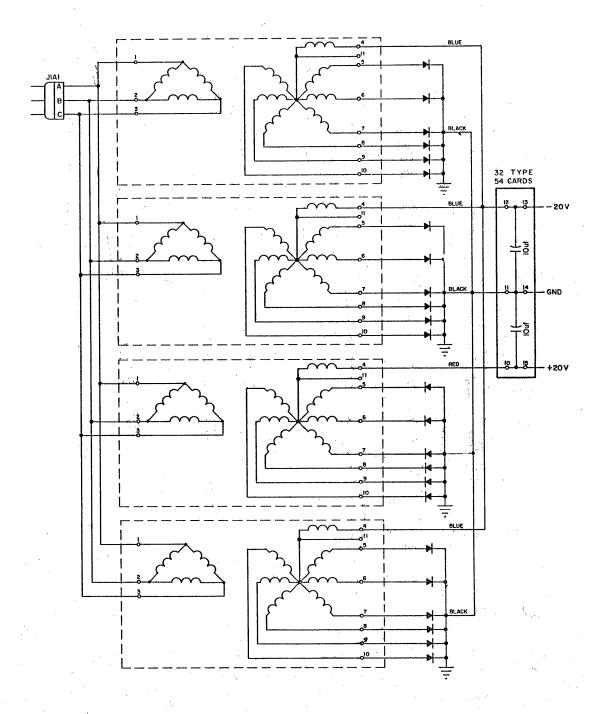

### STANDARD CARD TYPES

The majority of printed circuit cards consist of one or two standard inverters on a single card. The cards differ in the number of inverters on the card, the number of input and output diodes associated with each inverter, and the electrical interconnections, if any. A maximum of six inputs may be applied to an inverter, and a maximum of eight outputs may be taken from it. Since an unused input terminal is sensed as a "1" input, no more than the exact number of input terminals required can be present. Inverter cards, therefore, are

Figure 1-13. Interconnection of Three-Stage Counters to Form Nine-Stage Counters.

provided with varying numbers of input and output terminals to handle the various situations of logic.

The inverter cards are assigned two-digit numbers; the highest-order digit designates the type of card, and the lowest-order digit the number of inputs associated with each inverter on the card. (In the case of the Control Delay cards, only one inverter has external inputs.) The various types of inverter cards, and the pin assignments for each, are listed in table 1-3. The significance of letters is as follows:

I - input

O - output

A - as subscript one of the inverters on a card having two

C - as subscripts other inverter

C - not as subscript, a clock pulse

TABLE 1-3. DESCRIPTION OF STANDARD CARD TYPES

|             |           |      |      |       |                | f outputs             |                           |                           | -                         |                           | 15 FF                     |            | ***            |                              |                           |                           |                  |                  |      | ,  |              |   |

|-------------|-----------|------|------|-------|----------------|-----------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|------------|----------------|------------------------------|---------------------------|---------------------------|------------------|------------------|------|----|--------------|---|

| Designation | Inverters | (per | inve | rter) | (per           | inverter              | ) 1                       | 2                         | 3                         | 4                         | 5                         | 6          | 7              | . 8                          | 9                         | 10                        | 11               | 12               | 13   | 14 | 15           |   |

| 11          | 1         |      | 1    | **    |                | 8                     | I                         |                           |                           |                           | 0                         | 0          | О              | O                            | Ο                         | O                         | 0                | 0.               | -20V | Gd | +20V         |   |

| 12          | 1         |      | 2    |       |                | 8                     | 1                         | 1                         |                           |                           | O                         | 0          | Ó              | О                            | O                         | 0                         | 0                | 0                | -20V | Gd | +20V         |   |

| 13          | 1         |      | 3    | •     | - <del>-</del> | 8                     | 1                         | I                         | I                         |                           | 0                         | O          | Ο              | 0                            | 0                         | O                         | Ο                | <b>O</b> ,       | -20V | Gd | +20V         |   |

| 14          | 1         |      | 4    | *     |                | 8                     | I                         | I                         | 1                         | I                         | O                         | О          | О              | 0                            | О                         | О                         | О                | 0                | -20V | Gd | +20V         |   |

| 15          | 1         |      | 5    |       |                | 7                     | 1                         | 1.                        | I                         | 1                         | I                         | О          | О              | 0                            | 0                         | <b>O</b>                  | О                | 0                | -20V | Gd | +20V         |   |

| 16          | 1         |      | 6    |       |                | 6                     | I                         | I                         | I                         | I                         | I                         | I          | Ο              | Ο                            | Ο                         | 0                         | Ο                | 0                | -20V | Gd | +20V         |   |

| 21          | 2         |      | 1    |       | - •            | 5                     | $\mathbf{I}_{\mathbf{A}}$ | OA                        | $O_A$                     | $O_A$                     | $\mathbf{O}_{\mathbf{A}}$ | OA         | <sup>I</sup> C | $O_{\mathbf{C}}$             | OC                        | OC                        | OC               | OC               | -20V | Gd | +20 <u>V</u> |   |

| 22          | 2         |      | 2    |       |                | 4                     | $I_{A}$                   | $\mathbf{I}_{\mathbf{A}}$ | $O_A$                     | $O_A$                     | $O_A$                     | $O_A$      | I <sub>C</sub> | $^{\mathrm{I}}\mathbf{C}$    | OC                        | $o_{\mathbf{C}}$          | $O_{\mathbf{C}}$ | $O_{\mathbb{C}}$ | -20V | Gd | +20V         |   |

| 23          | 2         |      | 3    |       | -              | 3                     | $I_{\mathbf{A}}$          | $\mathbf{I}_{\mathbf{A}}$ | $\mathbf{I}_{\mathbf{A}}$ | $O_A$                     | $O_A$                     | OA         | IC             | $^{\mathrm{I}}\mathbf{C}$    | $^{\mathbf{I}}\mathbf{C}$ | $O_{\mathbf{C}}$          | $o_{\mathbf{C}}$ | $O_{\mathbb{C}}$ | -20V | Gd | +20V         |   |

| 24          | 2         |      | 4    |       |                | 2                     | $I_{\mathbf{A}}$          | $I_{A}$                   | $I_{A}$                   | $\mathbf{I}_{\mathbf{A}}$ | $O_A$                     | OA         | IC             | IC                           | I <sub>C</sub>            | $\mathbf{I}_{\mathbf{C}}$ | OC               | oc               | -20V | Gd | +20V         |   |

| 31*         | 2         |      | 1    |       |                | <b>5</b> <sup>-</sup> | $I_{\mathbf{A}}$          | $O_A$                     | OA                        | $O_A$                     | $O_A$                     | OA         | I <sub>C</sub> | $o_{\mathbf{C}}$             | $O_{\mathbf{C}}$          | $o_{\mathbf{C}}$          | OC               | OC               | -20V | Gd | +20V         |   |

| 32*         | 2         |      | 2    |       |                | 4                     | $\mathbf{I}_{\mathbf{A}}$ | $I_A$                     | $O_A$                     | $O_A$                     | $O_A$                     | OA         | IC             | $^{\mathrm{I}}\mathrm{C}$    | $O_{\mathbb{C}}$          | $o_{\mathbf{C}}$          | $o_{\mathbf{C}}$ | OC               | -20V | Gd | +20V         |   |

| 33*         | 2         |      | 3    |       | -              | 3                     | $\mathbf{I}_{\mathbf{A}}$ | $\mathbf{I}_{\mathbf{A}}$ | $^{1}A$                   | $O_A$                     | $O_A$                     | OA         | I <sub>C</sub> | $^{\mathrm{I}}\mathrm{_{C}}$ | I <sub>C</sub>            | $O_{\mathbf{C}}$          | $o_{\mathbf{C}}$ | OC               | -20V | Gd | +20V         | 7 |

| 41**        | 2         |      | 1    |       | ÷ .            | 6                     | · I                       |                           |                           |                           |                           | C          | O              | 0                            | О                         | O                         | 0 .              | O                | -20V | Gđ | +20V         |   |

| 42**        | 2         |      | 2    |       | •              | 6                     | 1                         | I                         |                           |                           |                           | C          | О              | О                            | Ο                         | Ο                         | Ο                | 0                | -20V | Gd | +20V         |   |

| 43**        | 2         |      | 3    |       |                | 6                     | I                         | Ι.                        | Į,                        |                           |                           | <b>C</b> . | 0              | O                            | 0                         | Ο                         | O                | О                | -20V | Gd | +20V         |   |

| 44**        | 2         |      | 4    | · .   |                | 6                     | I                         | I                         | 1.                        | , I                       |                           | C          | O              | 0                            | 0                         | O                         | 0                | 0                | -20V | Gd | +20V         | , |

| 45**        | 2         |      | 5    |       | •              | 6                     | I                         | I                         | I                         | Ī                         | I                         | C          | 0              | 0                            | 0                         | o                         | 0                | 0                | -20V | Gd | 1+20V        | • |

<sup>\*</sup> The types 31, 32, and 33 are two-inverter units which have internal feedback or flip-flop connections.

<sup>\*\*</sup> The types 41, 42, 43, 44, and 45 are two-inverter units used in Control Delay circuits; a clock pulse applied to pin 6 controls the internal feedback connection.

### **BOOLEAN ALGEBRA**

Boolean algebra is both similar to and different from ordinary algebra. Because of the differences, it is simpler at first to regard it as unrelated to ordinary algebra. The logical equations (page 22) which describe the connections of building blocks in the computer are a specialized form of Boolean algebra as applied to switching circuits. A brief discussion of this type of algebra will aid in use of the File of Equations.

In Boolean algebra, there are only two values or quantities to be considered, namely, "1" and "0". In a Boolean equation the variables, or literals, are restricted to these values, which can be considered as opposites; one is the negation of the other.

There are three operations used in such equations. The first is the logical product or the AND function of two terms, which is indicated by a dot between the terms, or by the absence of any symbol between them. This function is satisfied only when both terms are "1"; it is not satisfied for all other combinations of values of the terms.

The second operation is the logical sum or the OR function of two terms, which is indicated by a plus sign between the terms. An OR function of two terms is satisfied when one or the other, or both, of the terms are "1"; it is not satisfied only when both terms are "0". Thus, this is the inclusive OR rather than the exclusive.

The third operation is negation, or the NOT function of a term, and is indicated by a bar over the term. If a term is "1", then the negation of that term has the value "0", and vice versa.

The grouping of terms is indicated by parentheses. It is customary in Boolean equations for switching circuits to represent the circuit inputs by literals which appear on the right side of the equal sign. The literal on the left side of the equal sign represents the circuit output,

which is a function of the inputs on the right side of the equation. Table 1-4 is a glossary of the various symbols used in the algebra of switching circuits.

There are two types of Boolean equations: (1) identities; and (2) transfer formulas. An identity consists of two equivalent expressions separated by an equality sign. For example, the equation (A + B)C = AC + BC is an identity, which states that either A or B in combination with C, is equivalent to either A in combination with C, or B in combination with C; while on the other hand, the equation C = A + B is a transfer formula, which states that at some particular instant, a "1" is transferred to element C if a "1" is in either element A or element B.

A Boolean expression may be reduced to its simplest equivalent by applying the basic identities of table 1-5. This procedure not only provides a means of understanding the circuitry, but also of simplifying switching circuits, thus reducing the number of components necessary to perform the operations specified by a particular transfer equation. For example, the transfer equation D = AB + B + C can be reduced to its equivalent D = B + C by applying the theorems of table 1-5 to strike out the redundant expression AB. Because the right side of the reduced transfer equation is simpler than the right side of the unreduced equation, a circuit built by using the simplified equation uses fewer components and yet performs the same logical functions.

The theorems are also applied to convert the final simplified expressions into "standard" forms, that is, forms which are more readily adaptable to a given type of switching circuit. For example, the equation D = (A + C) ( $\overline{B}$ ) can be changed to the formula  $D = A\overline{B} + C\overline{B}$ , which is applicable to the building block used in the computer.

### TABLE 1-4. GLOSSARY OF BOOLEAN SYMBOLS

| A<br>B<br>C<br>D<br>etc.           | Letters used to denote switching elements. When a letter appears in a Boolean expression, it is a literal that denotes an active "1" input when the corresponding switching element is in the "1" state, or a passive "0" input when the corresponding switching element is in the "0" state. |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ā         B         C         etc. | The bar notation denotes negation. When a letter with a bar appears in a Boolean expression, it denotes an input that is active when the corresponding switching element is in the "0" state, and passive when the element is in the "1" state.                                               |

|                                    | Denotes an active ('1") input in a Boolean expression.                                                                                                                                                                                                                                        |

| 0,                                 | Denotes a passive ("0") input in a Boolean expression.                                                                                                                                                                                                                                        |

| +                                  | Denotes the logical sum, or the OR function of two or more literals.                                                                                                                                                                                                                          |

| ()()<br>etc.                       | Denotes the logical product, or the AND function of two or more literals.                                                                                                                                                                                                                     |

| =                                  | Denotes equality. Used to separate equivalent Boolean expressions, or to separate the two halves of a transfer formula.                                                                                                                                                                       |

### TABLE 1-5. BOOLEAN IDENTITIES

### A. COMMUTATIVE LAWS

1.

$$A + B = B + A$$

2.

$$B + A = A + B$$

### B. ASSOCIATIVE LAWS

3.

$$(A + B) + C = A + (B + C)$$

4.

$$(AB) C = A (BC)$$

### C. DISTRIBUTIVE LAWS

5.

$$AB + AC = A(B + C)$$

6.

$$A + BC = (A + B)(A + C)$$

### D. FORMS INVOLVING 1 AND 0

$$7. \quad 0 + 0 = 0$$

$$8.0+1=1$$

9.

$$1+1=1$$

$$10.0 \cdot 0 = 0$$

11.

$$0 \cdot 1 = 0$$

12.

$$1 \cdot 1 = 1$$

13.

$$A + 0 = A$$

14.

$$A + 1 = 1$$

15.

$$A \cdot 1 = A$$

16.

$$A \cdot 0 = 0$$

### E. FORMS WITH REPEATED LITERALS

17.

$$A + A = A$$

18.

$$A \cdot A = A$$

### F. FORMS WITH NEGATION

19.

$$A = A$$

20.

$$A \bar{A} = 0$$

21.

$$A + \overline{A} = 1$$

22.

$$\overline{A \cdot B \cdot C} = \overline{A} + \overline{B} + \overline{C}$$

De Morgan's Theorem

23.

$$\overline{A+B+C} = \overline{A} \cdot \overline{B} \cdot \overline{C}$$

## G. FORMS DERIVED FROM PREVIOUS IDENTITIES

24.

$$A + AB = A$$

25.

$$A(A + B) = A$$

26.

$$(A + \overline{B}) B = AB$$

27.

$$A \bar{B} + B = A + B$$

28.

$$BC = ABC + \overline{A}BC$$

The proofs of these identities are all of a similar nature. A simple proof of Identity 6 is presented below in table 1-6.

TABLE 1-6. PROOF OF IDENTITY 6

| Conditions<br>A B C | Left-Hand<br>Expression<br>A + BC | = | Right-Hand<br>Expression<br>(A + B) (A + C) |

|---------------------|-----------------------------------|---|---------------------------------------------|

| 0 0 0               | 0                                 |   | 0                                           |

| 0 0 1               | 0                                 |   | 0                                           |

| 0 1 0               | 0                                 |   | 0                                           |

| 0 1 1               | 1                                 |   | 1                                           |

| 1 0 0               | . 1                               |   | 1                                           |

| 1 0 1               | 1                                 |   | 1                                           |

| 1 1 0               | 1                                 |   | 1                                           |

| 1 1 1               | . 1                               |   | 1                                           |

Identity 6 contains three literals, each capable of being in either the "0" or the "1" state. The various combinations of "1's" and "0's" for these literals are listed in the Conditions column of table 1-6. In the Left-Hand Expression column, the "logical value" of the left-hand side of the expression for each ABC condition is listed. Similar values are also listed in the Right-Hand Expression column next to each ABC condition to represent values obtained from the right-hand expression of the identity. It is apparent that the left-hand and right-hand values are equivalent for each ABC condition; therefore, the two expressions are identical.

Identities 22 and 23 are worthy of special attention. By application of them, an equation using the AND function can be converted into one using the OR function, and vice versa. For example, the equation Z = ABC is to be converted into an equivalent one in which the OR

function is used in the right side. This is done by first negating both sides of Z = ABC and thereby obtaining  $\overline{Z} = \overline{ABC}$ . Now by applying Identity 22 to the right side, the desired result  $\overline{Z} = \overline{A} + \overline{B} + \overline{C}$  is obtained. This procedure, which is often called inverting the logic, has been employed at various times in the equations for the computer.

### CHAPTER 2

### CONTROL SECTION

The control section of the computer directs the operations required to execute instructions and to exchange data with external equipment. In addition, it establishes the timing relations required to perform the operations in the proper sequence.

This section consists of main or overall control and the specialized control units: storage control, arithmetic control and input-output control. Main control, which performs many operations itself, also initiates action in these specialized units; these units produce the commands to carry out specific operations. This chapter deals primarily with main control and its relationship to these units.

The major elements of main control are the sequences, several networks of FFs and single inverters which sense and store static conditions, and several registers (U, P, R and  $B^1$  through  $B^6$ ).

The execution of instructions and the exchange of data with external equipment are accomplished by many simple unit operations called "commands". A command, which is issued by a sequence, causes one simple action to occur, such as the transmission of the content of a register to another or the setting of a control FF. In the execution of instructions the issuing of commands is controlled directly or indirectly by the instruction word in the program control register. Commands may also be conditioned by the presence or absence of specified conditions in some part of the computer.

The control section senses conditions, determines operations that are required, and issues commands in an order suitable for the performance of such operations.

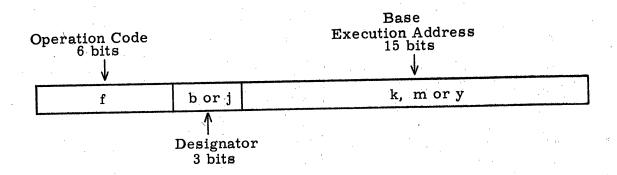

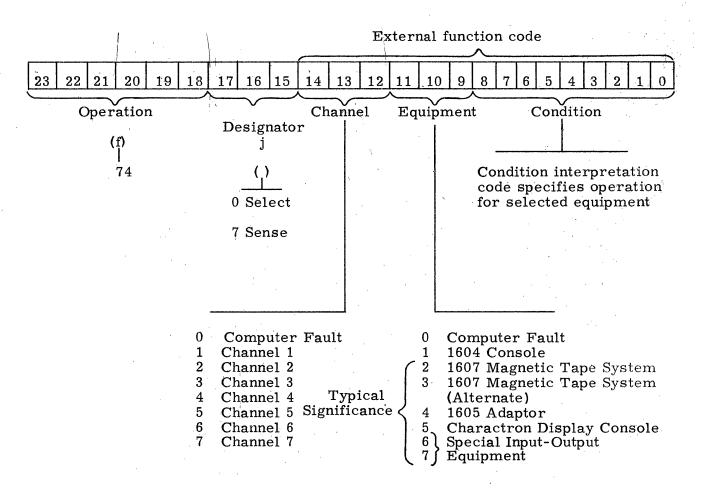

An instruction is a 24-bit quantity consisting of three parts which are arranged as shown below in Figure 2-1:

Figure 2-1. Instruction Format.

Each of the 62 instructions has a unique 6-bit operation code, f, which designates the instruction. The translation of f establishes the condition required within the control section for the execution of the instruction. The 3-bit designator usually specifies the index register, B, whose content is to be added to the base execution address; when so used the designator is denoted by the letter b. For some instructions it serves different purposes (described later). The execution address of an instruction is normally a base address quantity that is modified by the addition of B to yield the actual address of the instruction operand. Some instructions use the execution address in a different manner.

A 48-bit instruction word is read from storage and entered in  $U^1$ . Execution of the upper instruction occurs first. Following this, the lower instruction is transmitted to the upper half of  $U^1$  so that it can be executed. Thus the instruction currently being executed is always located in the upper half of  $U^1$ .

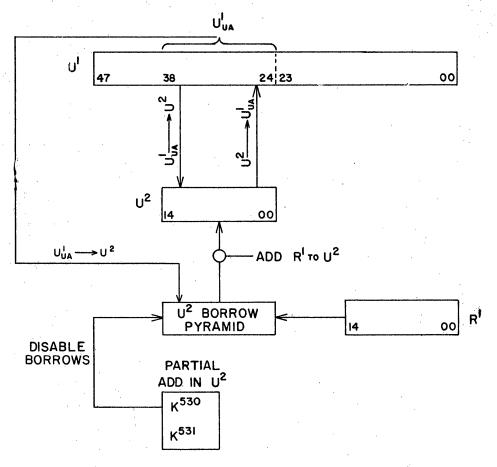

The primary function of U<sup>2</sup> is to modify the execution address, m, of the instruction in the upper half of U<sup>1</sup> by adding B<sup>b</sup> to it. In preparation for modification the designator of the upper instruction is translated. The translation specifies the B register the content of which is to be added in the modification.

### PROGRAM CONTROL REGISTER

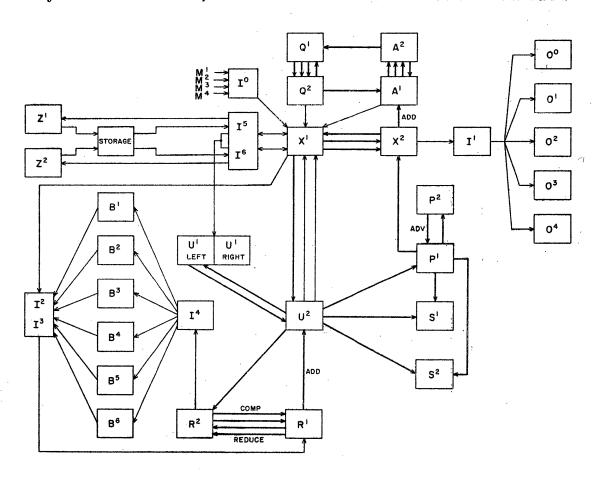

The program control register holds the 48-bit instruction word during the execution of the two 24-bit instructions contained in the word. All operations that are necessary to successfully execute an instruction are governed by the content of this register. Because the letter U is used as the base letter in the logical symbols for the elements making up the program control register, it is often called the U register.

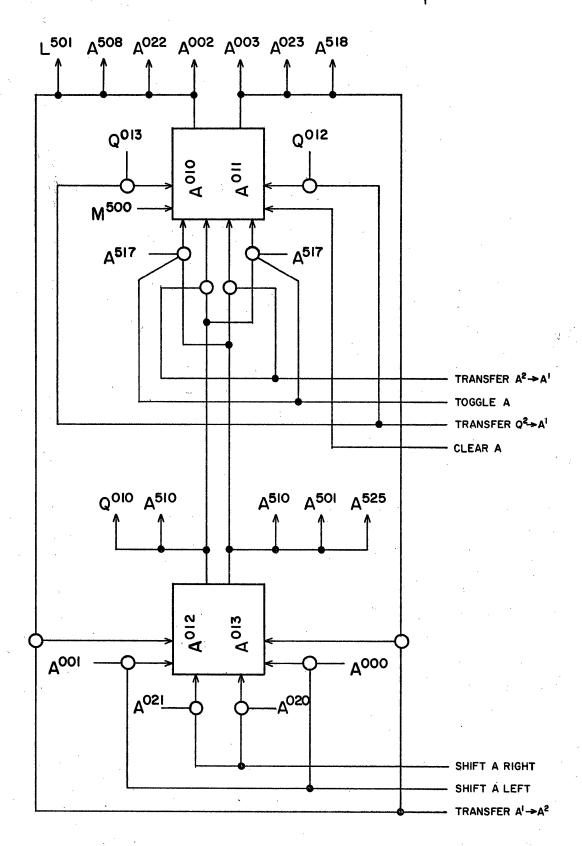

The U register consists of two ranks of FFs. Rank  $U^1$ , which is 48 bits in length, stores an instruction word during the execution of the two instructions contained in it. Rank  $U^2$ , 15 bits in length, has a borrow pyramid and therefore is a small subtractive accumulator. Transmission paths connect  $U^2$  to the m portion of the upper half of  $U^1$  (figure 2-2).

After transmitting m from  $U^1$  to  $U^2$  and adding  $B^b$  to R, R is added to  $U^2$ . The modified execution address in  $U^2$  for most instructions specifies the location of the operand in storage. In such cases  $U^2$  is transmitted to the appropriate S register.

Figure 2-2. Relation of  $U^2$  to  $U^1$ .

### **OPERATION CODE**

This six-bit code specifies an instruction and controls the operation of the computer during the execution of the instruction. Of the 64 possible values of this code, 62 specify instructions; codes 00 and 77 (codes are expressed in octal) represent fault conditions that halt computation.

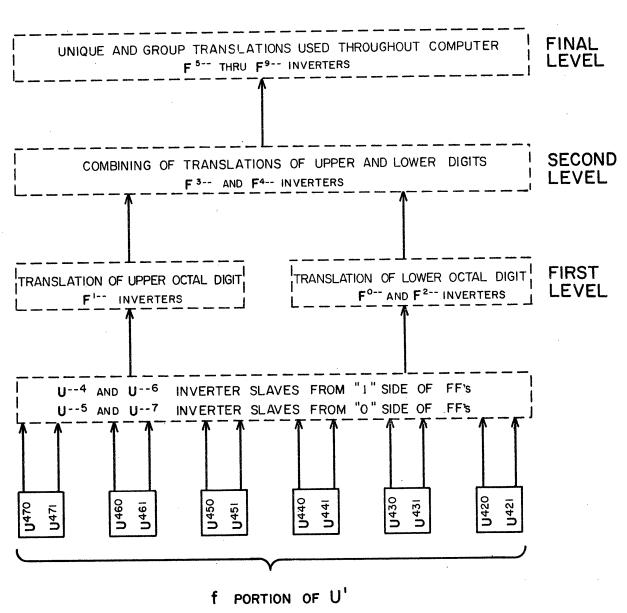

Prior to the actual execution of the instruction designated by the value of f, the operation code is translated by a network of single inverters which samples the upper six bits of U<sup>1</sup>. The results of the translation go to the various sections of the machine to condition the occurrence of the commands which will actually carry out the required operations.

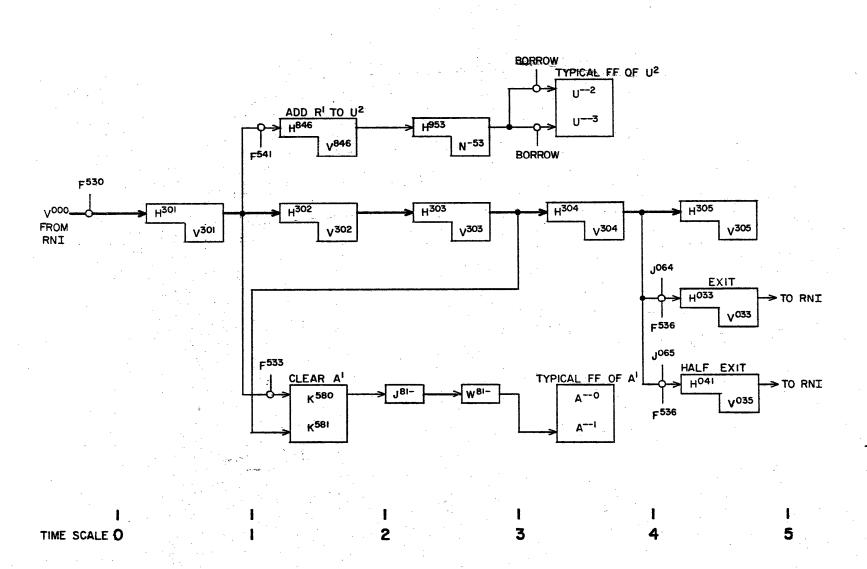

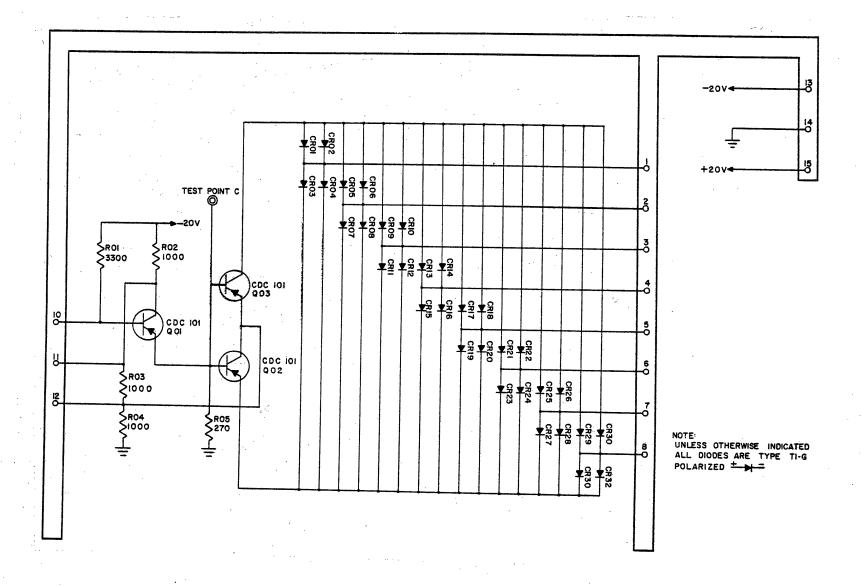

The translator uses several levels of logic in forming the outputs which actually gate commands. Figure 2-3 shows the fundamental structure of the translator. The large number of outputs from the upper six FFs of  $U^1$  are obtained by single inverter slaves. The "1" side of each FF has a  $U^{--4}$  and a  $U^{--6}$  inverter slave, the "O" side of each FF has a  $U^{--5}$  and a  $U^{--7}$  inverter slave.

The first level translation is divided into two parts, one concerned with the lower octal digit of f (that is,  $U_{42}$ ,  $U_{43}$ , and  $U_{44}$ ) and the other with the upper octal digit ( $U_{45}$ ,  $U_{46}$ , and  $U_{47}$ ). All  $F^{0-}$  and  $F^{2-}$  inverters translate the lower octal digit. All  $F^{1-}$  inverters translate the upper octal digit.

Unique (single-valued) translations of the lower octal digit are provided by  $F^{000}$  through  $F^{007}$ . When the output of one of these inverters is "1", then the lower octal digit has the value given in the third superscript digit of the inverter designation; that is, a "1" from  $F^{007}$  indicates that the lower digit is 7.

The  $F^{2-}$  inverters provide partial, or incomplete, translations of the lower octal digit. These translations are duplicated by several slave inverters. The  $F^{1-}$  inverters, which uniquely translate the upper octal digit, use the last digit of the inverter designation to indicate the value translated. Thus  $F^{105}$  indicates that the upper octal digit is 5.

In the second level of the translator, the outputs of first level inverters that translate individually the upper and the lower octal digits are combined to specify either a unique value

Figure 2-3. Structure of Operation Code Translator.

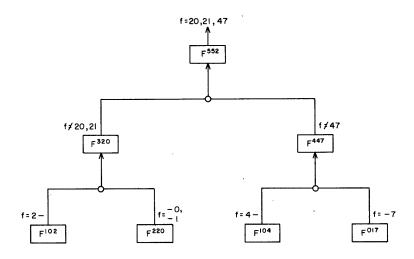

of the operation code or a group of values. The  $F^{3-}$  and  $F^{4-}$  inverters accomplish most of this combining of translations of the upper and lower digits. Outputs of the  $F^{3-}$  and  $F^{4-}$  inverters go to  $F^{5-}$  or  $F^{6-}$  inverters which actually supply the translations throughout the computer. A typical translation of f is shown in figure 2-4.

Figure 2-4. Typical Translation of Operation Code.

### **DESIGNATOR**

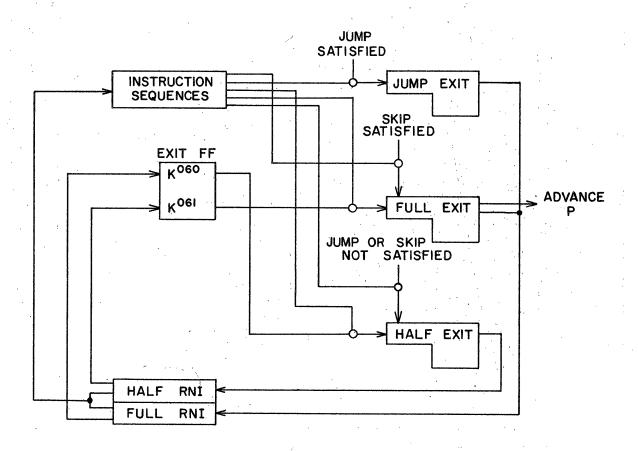

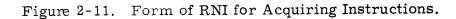

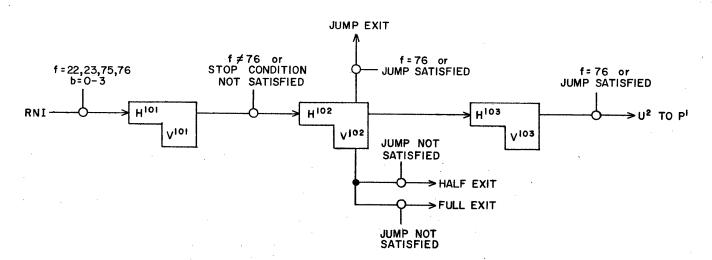

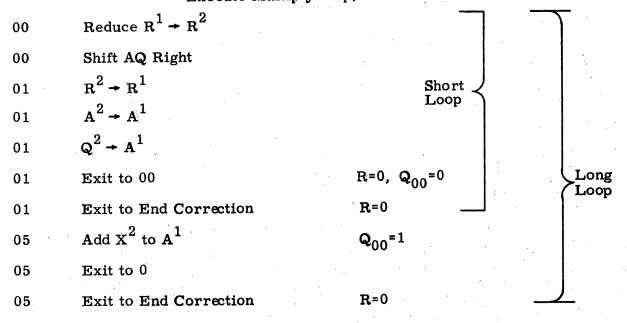

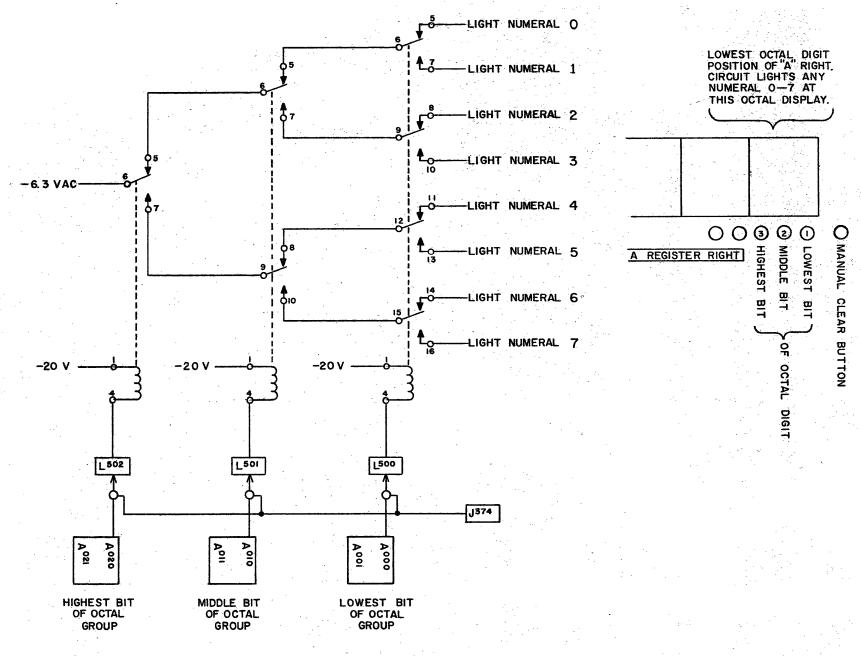

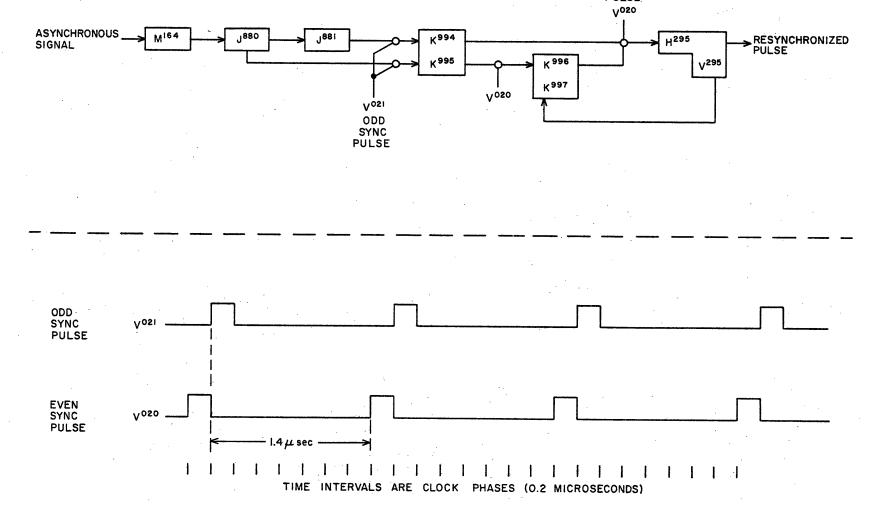

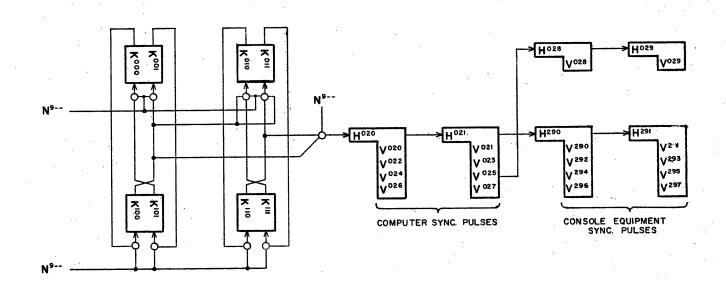

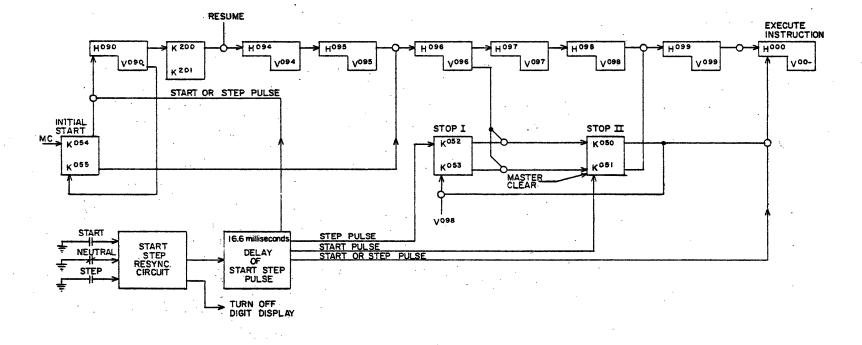

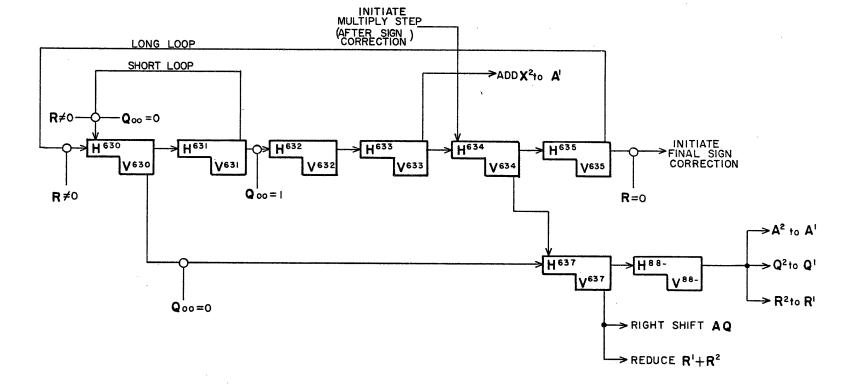

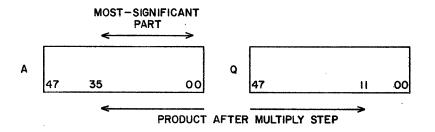

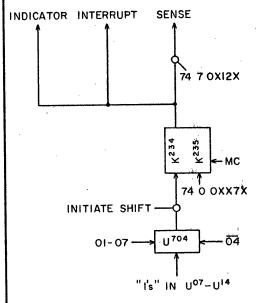

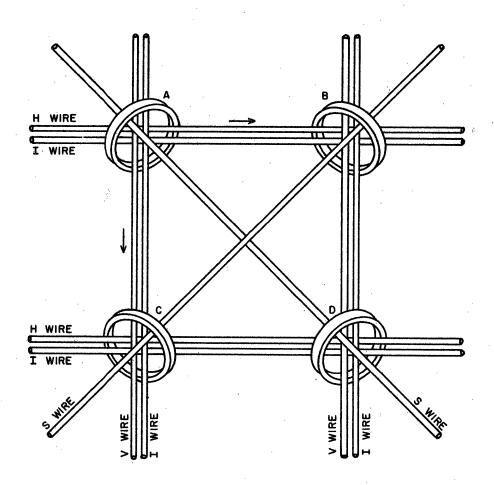

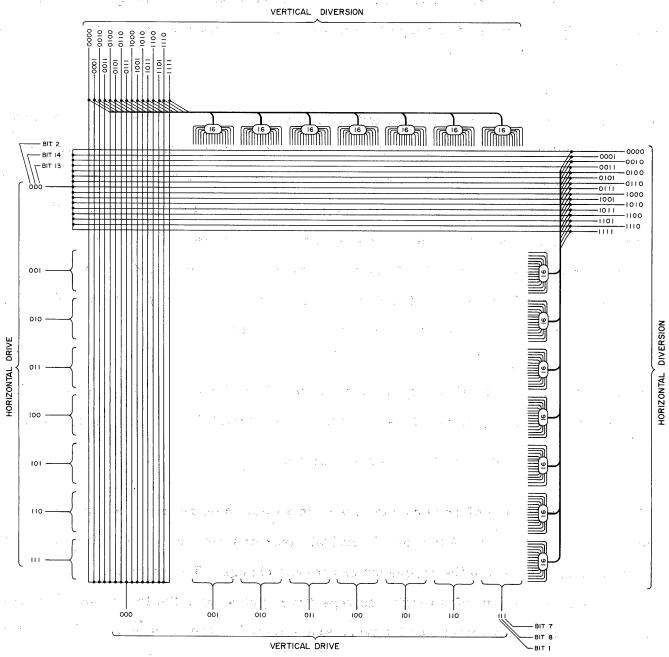

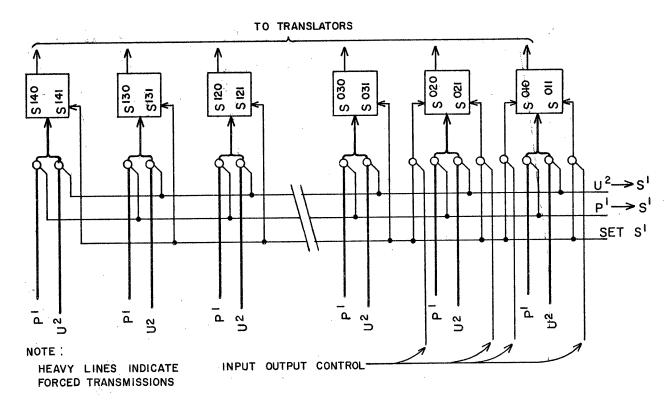

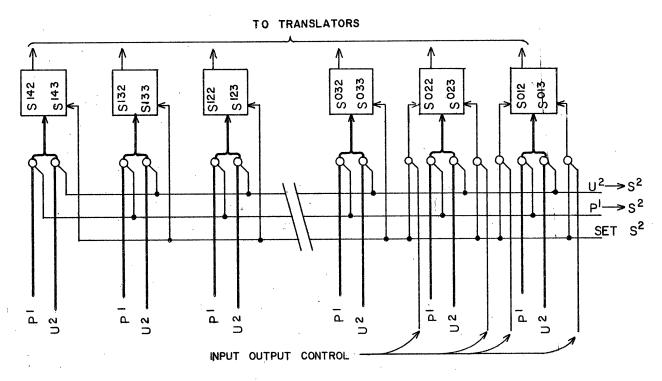

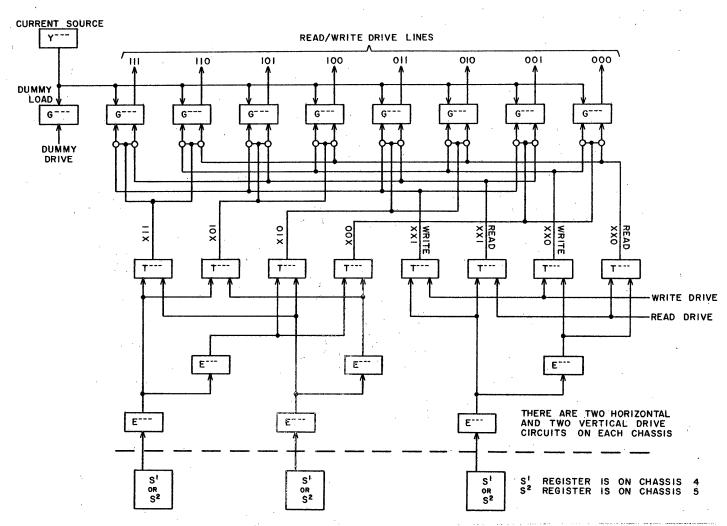

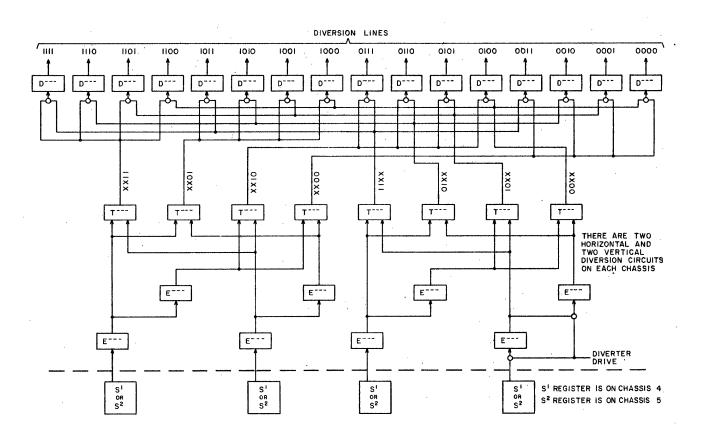

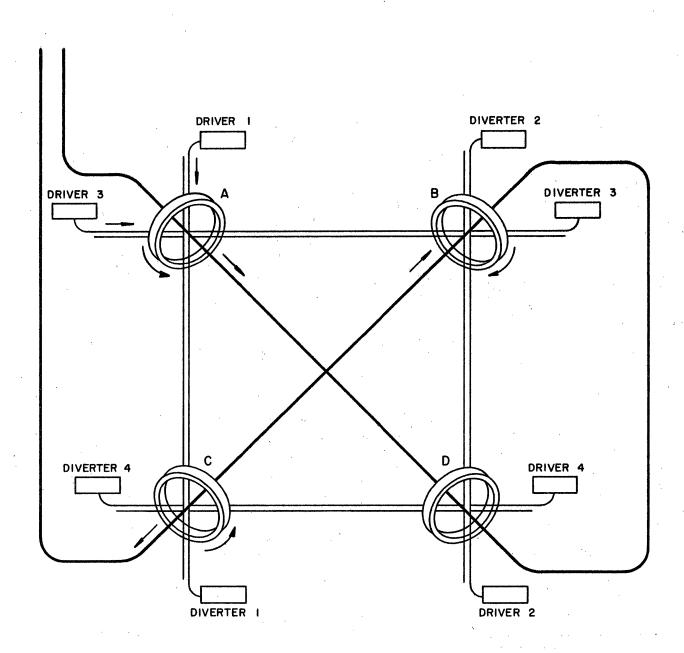

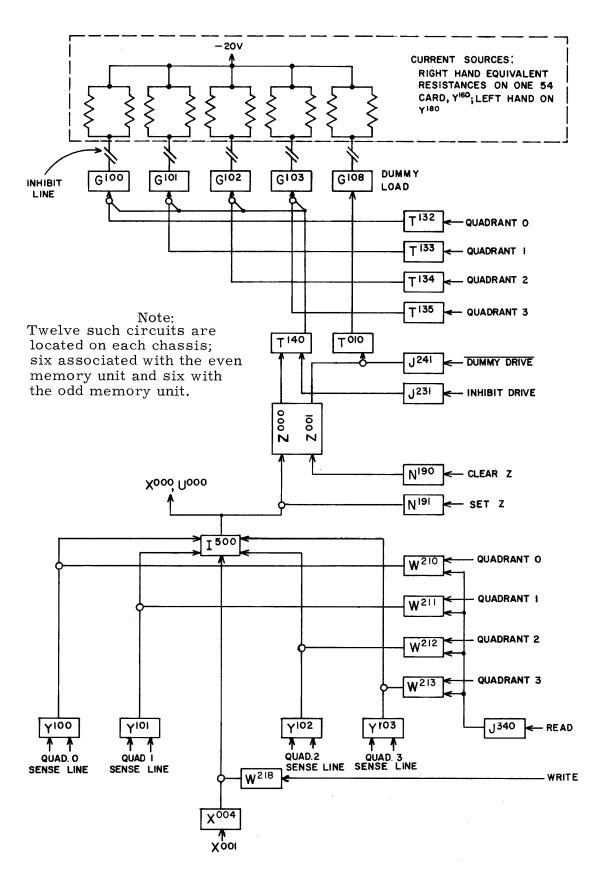

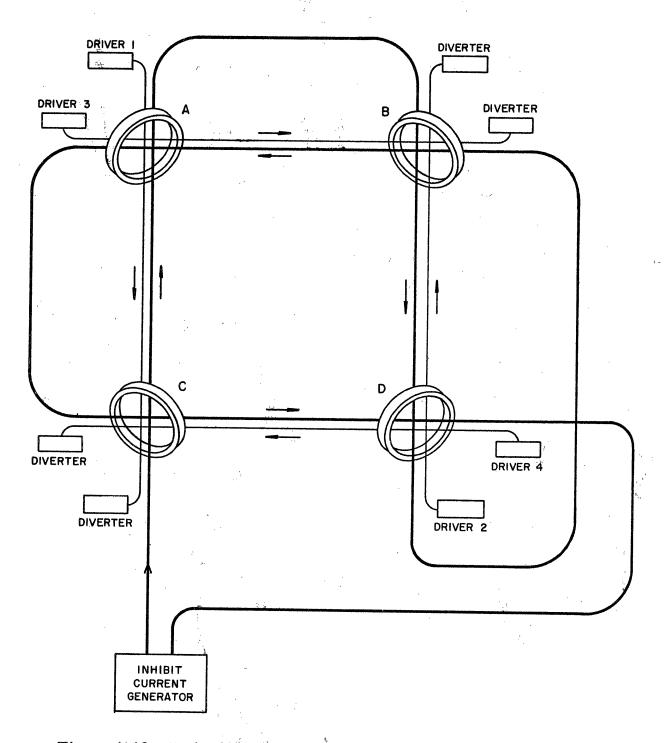

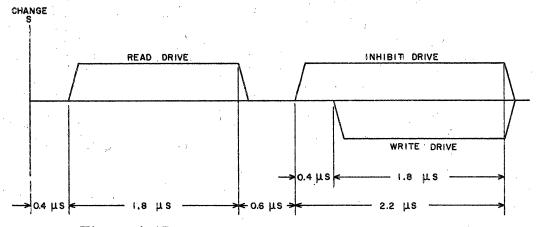

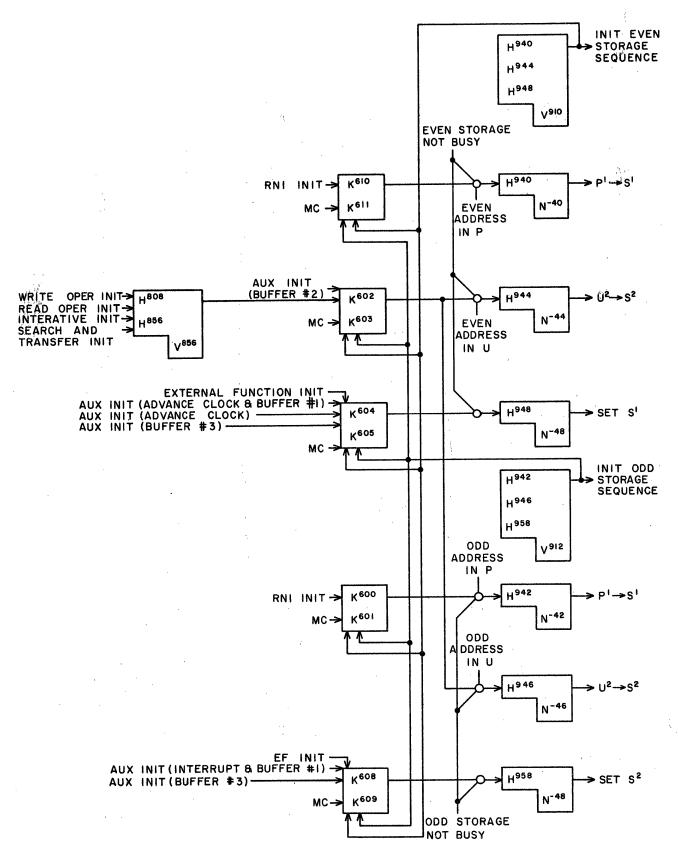

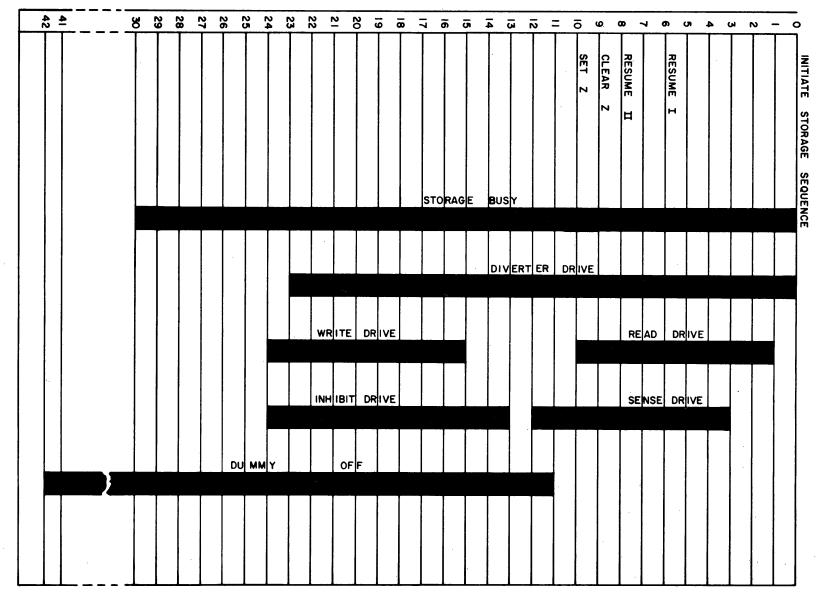

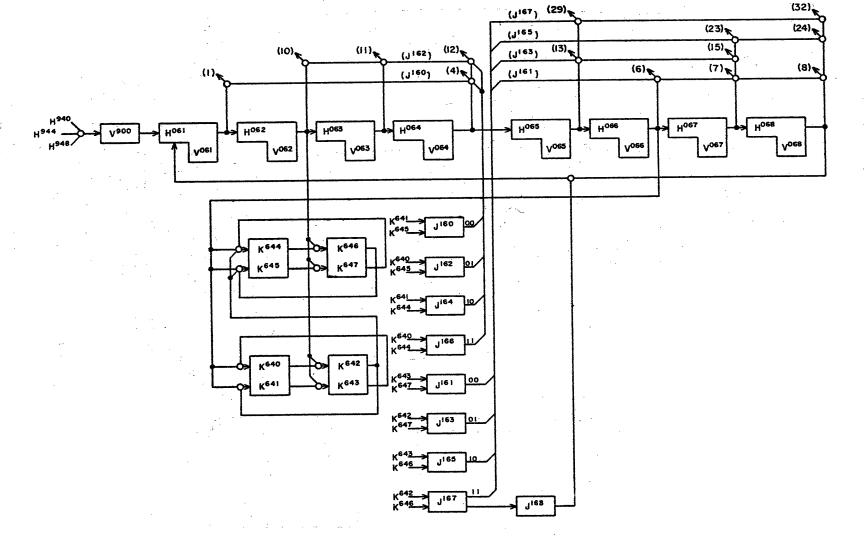

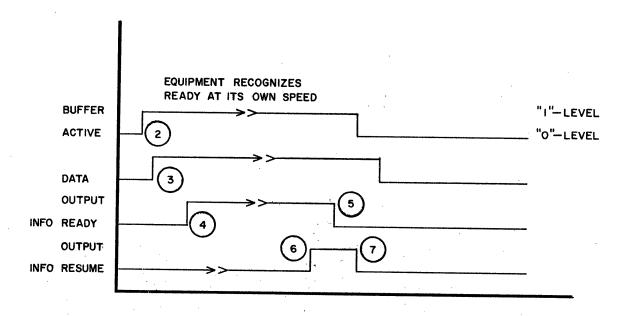

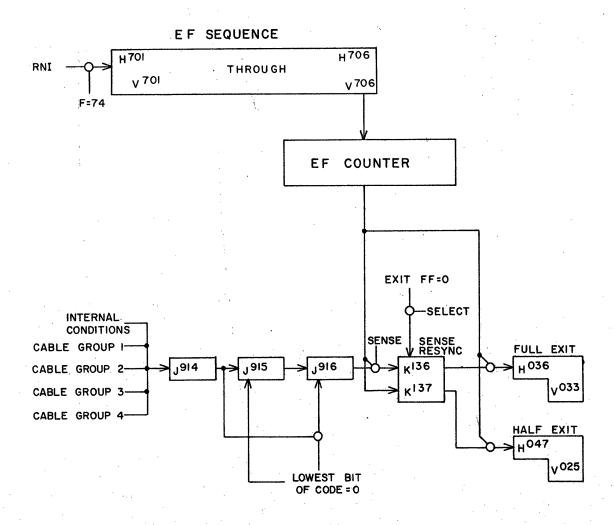

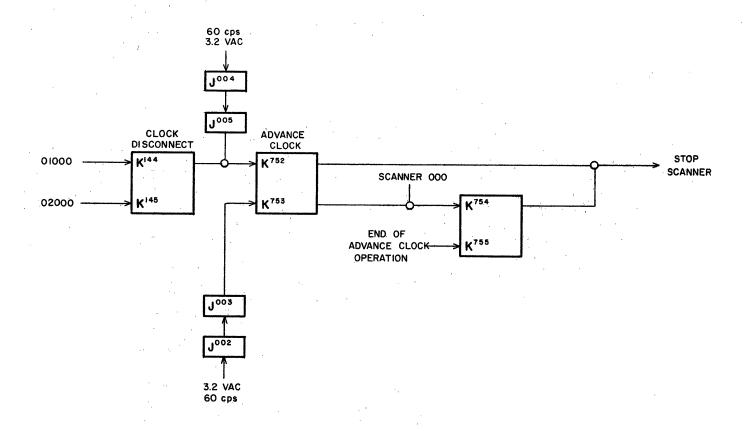

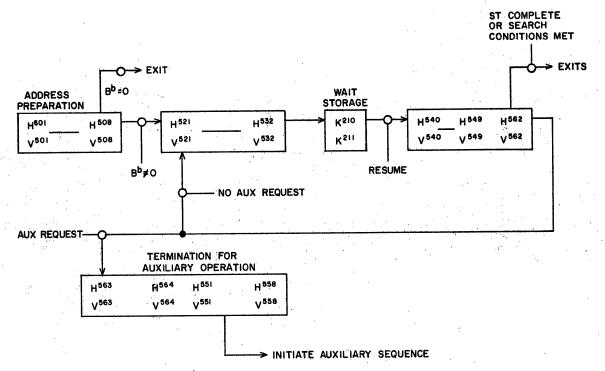

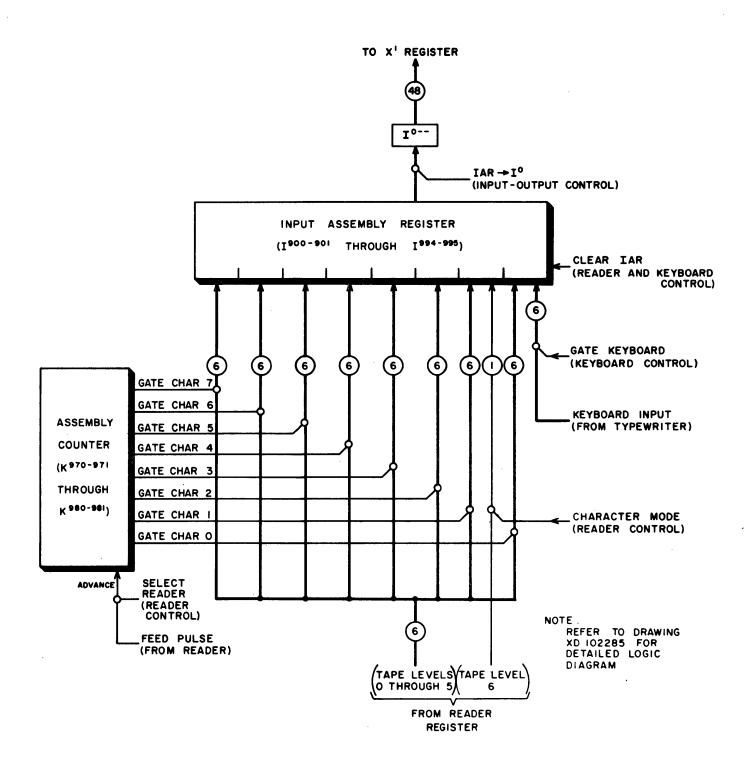

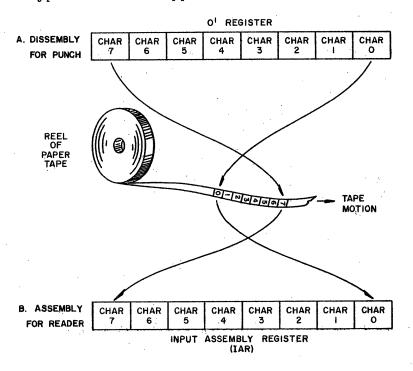

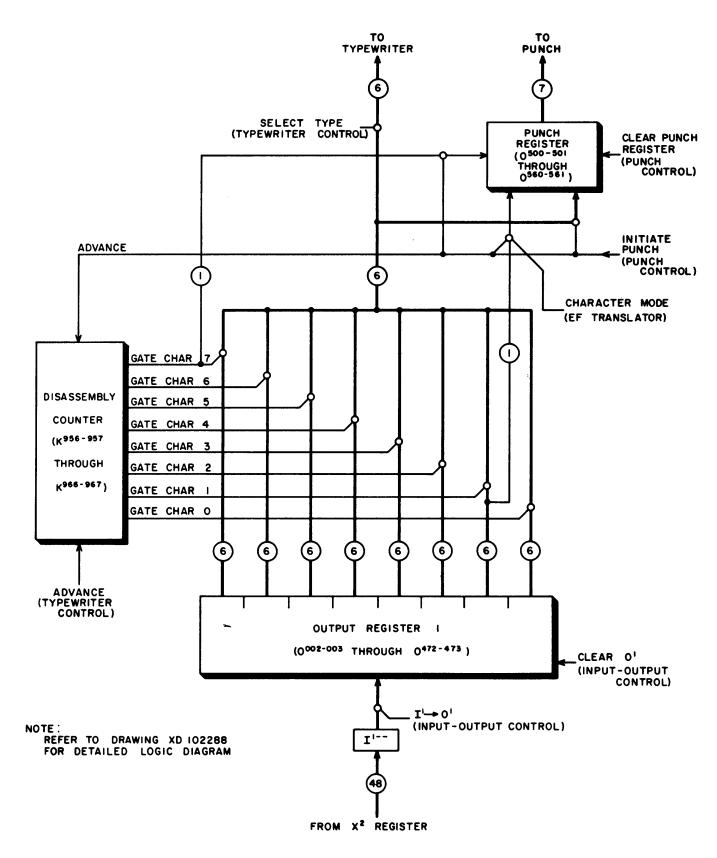

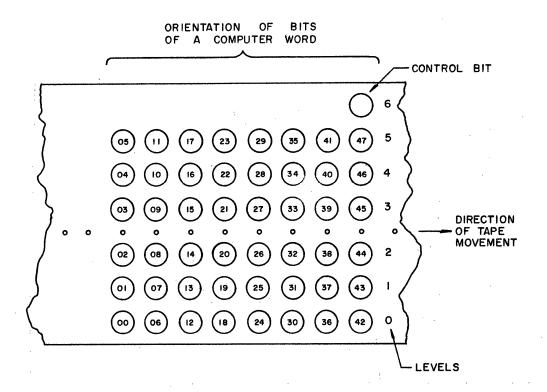

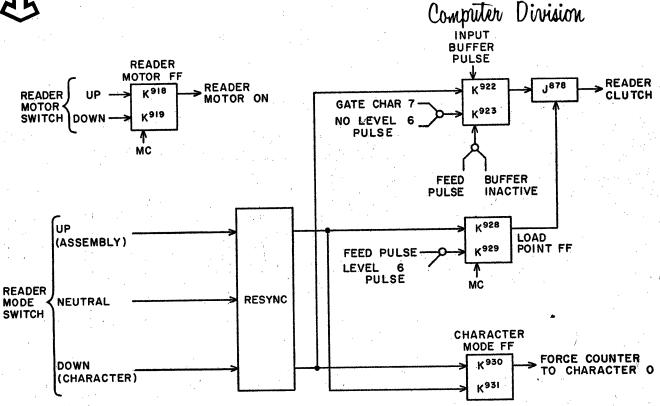

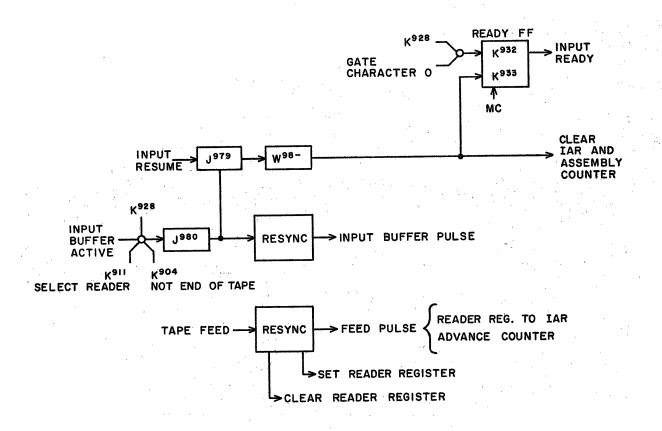

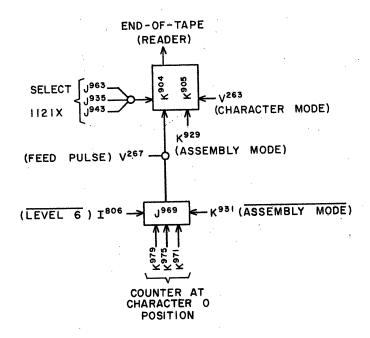

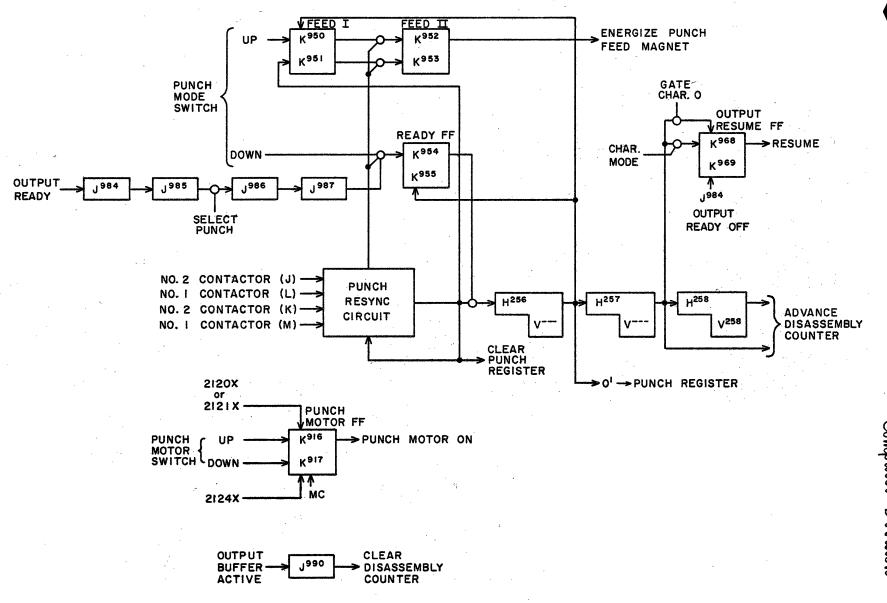

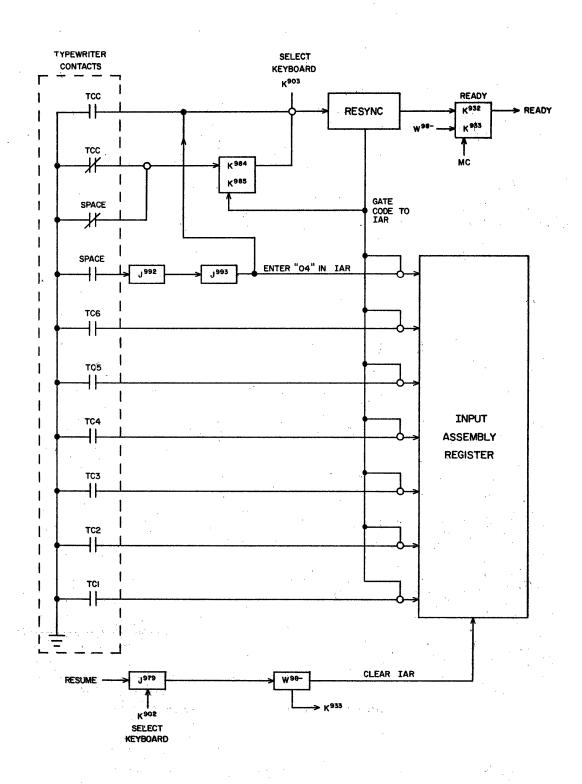

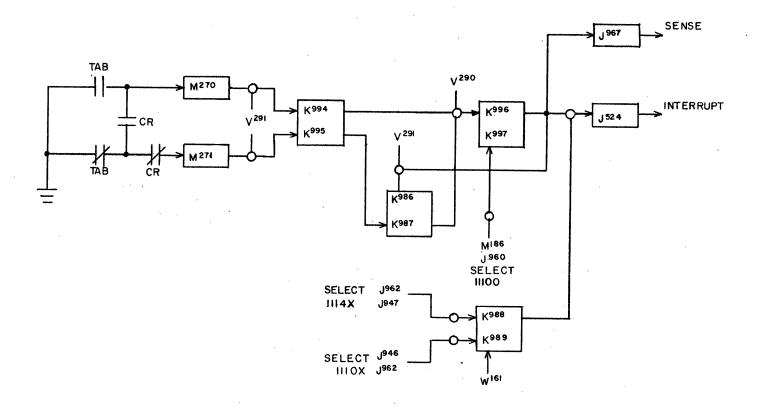

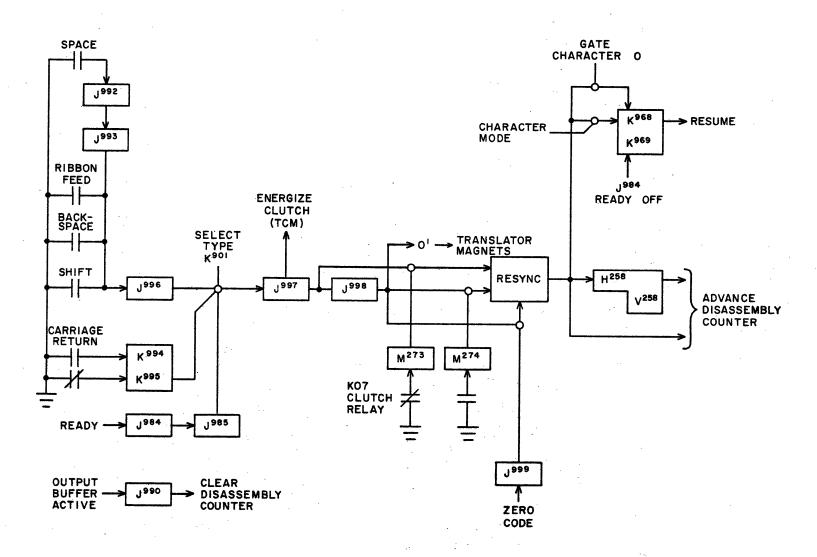

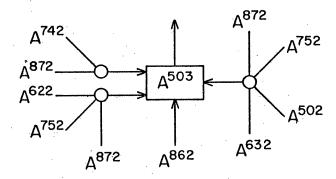

The primary function of the 3-bit designator in an instruction is to specify the index, or B, register whose content is used in executing the instruction. When used as an index designator it is denoted by the letter b. For most of these cases namely, the 01-21, 24-33, 36, 37, 40-47, and 70-73 instructions, B<sup>b</sup> is added to the execution address. With b=0 no modification of the execution address occurs; with b=7 indirect addressing is used.