MM54HC/74HC HIGH SPEED microCMOS™ LOGIC FAMILY DATABOOK

NATIONAL

SEMICONDUCTOR

CORPORATION

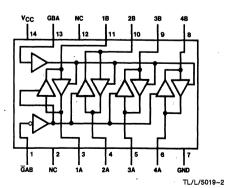

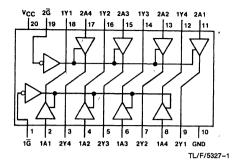

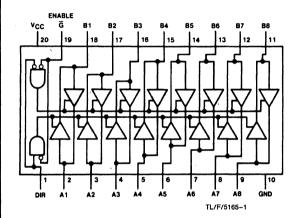

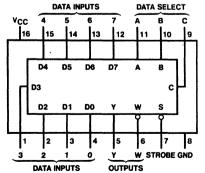

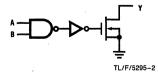

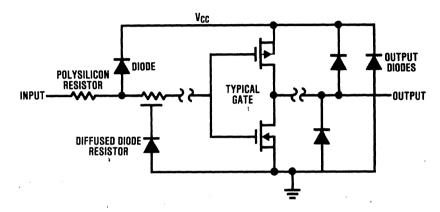

High Speed CMOS AC Diagrams

Application Notes

Connection Diagrams

MM54HC/MM74HC Data Sheets

MM54HCT/MM74HCT Data Sheets

Enhancement Programs

Reliability Report

Ordering and Package Information

<u>6</u>

### **TRADEMARKS**

Following is the most current list of National Semiconductor Corporation's trademarks and registered trademarks.

Abuseable™ M2CMOS™ SERIES/800™ Anadig™ Macrocomponent<sup>TM</sup> SPIRETM Auto-Chem Deflasher™ Microbus™ data bus (adjective) Starlink<sup>TM</sup> BI-FETTM microCMOSTM STARPLEXTM. BLC/BLXTM MICROWIRETM STARPLEX IITM СІМТМ MICRO-DACTM SuperChip<sup>TM</sup> **CIMBUSTM** MSTTM, SYS-16TM CIM-BD™ Nitride Plus™ TAPE-PAK™ CIM-XXXTM Nitride Plus Oxide™ Trapezoidal<sup>TM</sup> COPS™ microcontrollers NSC800™ TRI-CODE™ DIBTM NS16000™ TRI-POLYTM DIGITALKER™ NSX-16™ TRI-SAFE™ **XMOSTM** DISCERN™ NURAM™ DNRTM **OXISSTM XPUTM** P2CMOSTM **DPVMTM** Z STARTM E-Z-LINKTM Perfect Watch™ 883B/RETS™ HEX 3000™ Polycraft<sup>TM</sup> 883S/RETSTM **ISETM** POSitalker™ The National Anthem® QUAD3000TM Integral ISETM Datachecker® **RATTM** Maxi-ROM® Intelisplay™ ISE-16TM Shelf-Chek™ TRI-STATE®

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

### Introduction

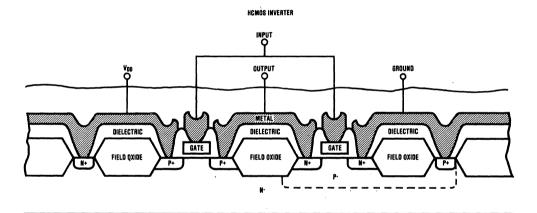

This comprehensive databook provides information on National Semiconductor's MM54HC/MM74HC high speed CMOS family of SSI/MSI/LSI logic components. The family utilizes microCMOSTM Technology\* to achieve the input and power supply characteristics of CD4000B CMOS with the high speed and large output drive of 54LS/74LS logic. This combination enables the construction of very high thru-put low power systems.

The MM54HC/MM74HC family has the same pin-out as equivalent 54LS/74LS functions, in addition, many popular CD4000 series logic functions are offered where no equivalent TTL function exists. Also, this high speed logic family incorporates a growing number of new functions not previously implemented in either a CMOS or TTL logic family.

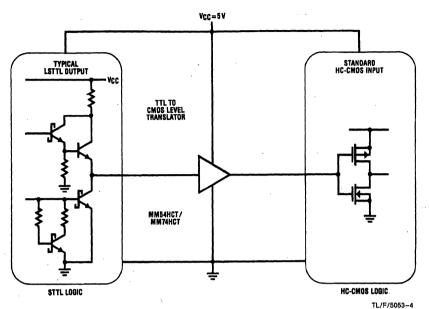

The MM54HCT/MM74HCT are a subfamily of MM54HC/MM74HC offering TTL compatible inputs. These MM54HCT/MM74HCT devices offer convenient TTL level translation to CMOS for those interface points where only TTL levels are provided, i.e. NMOS microprocessor bus, 54S/74S, 54ALS/74ALS, etc.

The broad line of MM54HC/MM74HC functions greatly simplifies the task of designing complete high speed systems in CMOS.

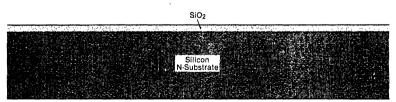

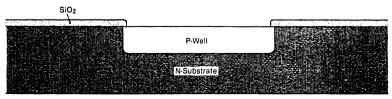

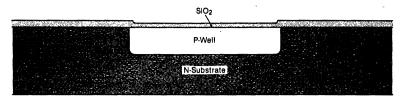

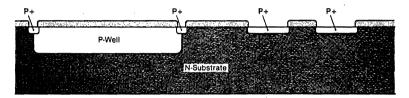

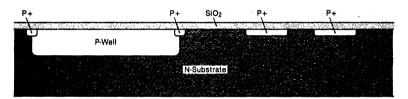

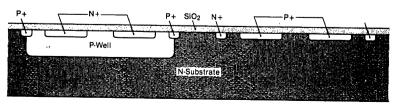

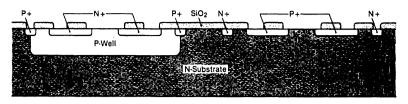

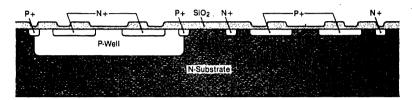

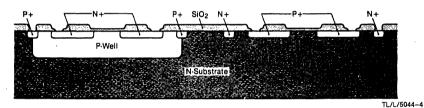

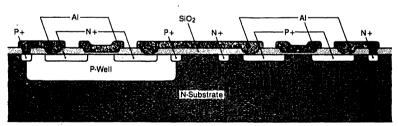

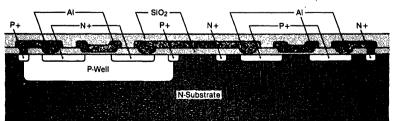

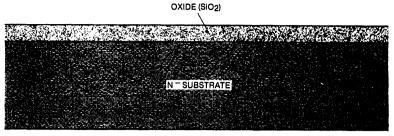

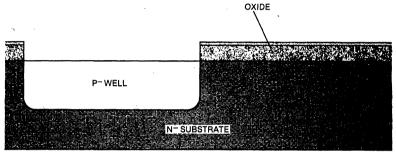

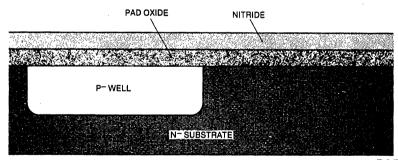

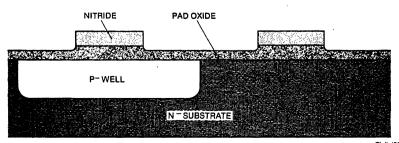

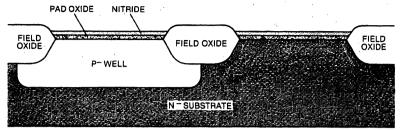

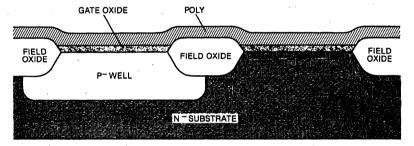

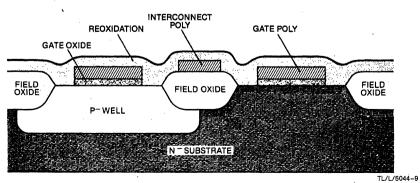

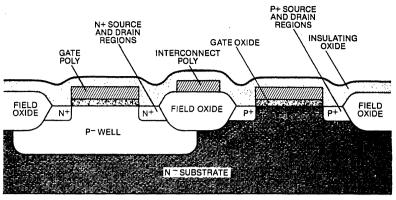

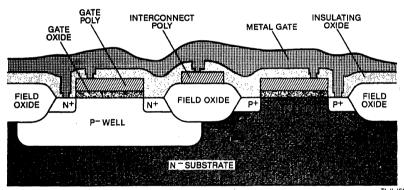

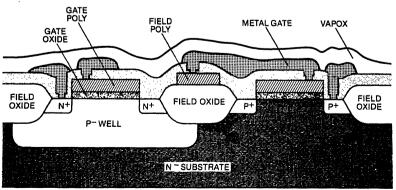

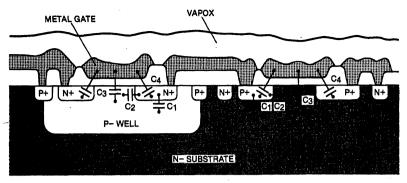

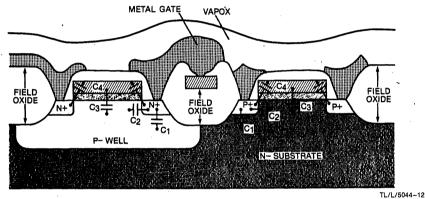

\* National's microCMOSTM Technology consists of N & P well, oxide-isolated processes with 1, 2 or 3 layers of metal and 1, 2 or 3 layers of polysilicon using either 2, 2.5, 3 or 3.5 micron features—leading to 1 micron and sub-micron in the future.

### **Quality and Reliability**

As electronic systems become more and more complex, the need for consistently high quality integrated circuits becomes increasingly important. Having recognized this need as far back as the 1970s, National Semiconductor initiated a unique, company-wide Quality Improvement Program. The results have been dramatic and, we believe, unmatched in this industry. Over the years, National has regularly been named by many major customers as "Quality Manufacturer of the Year." We are proud of our success, which sets a standard for others to achieve. And yet our quest for perfection is ongoing, so that customers can continue to rely on National Semiconductor integrated circuits and products in their system designs.

## **Numerical Index and Table of Contents**

| Introductioniii                                                      |

|----------------------------------------------------------------------|

| Numerical Index and Table of Contentsiv                              |

| High Speed CMOS Product Guideix                                      |

| High Speed CMOS Product Availability Guide                           |

| SECTION 1 HIGH SPEED CMOS AC DIAGRAMS                                |

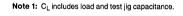

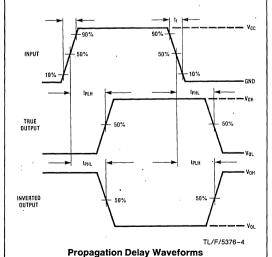

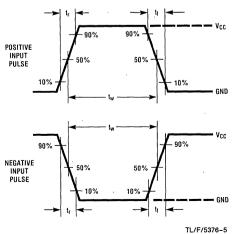

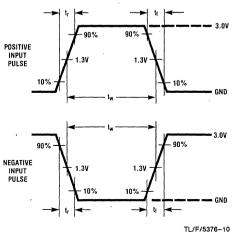

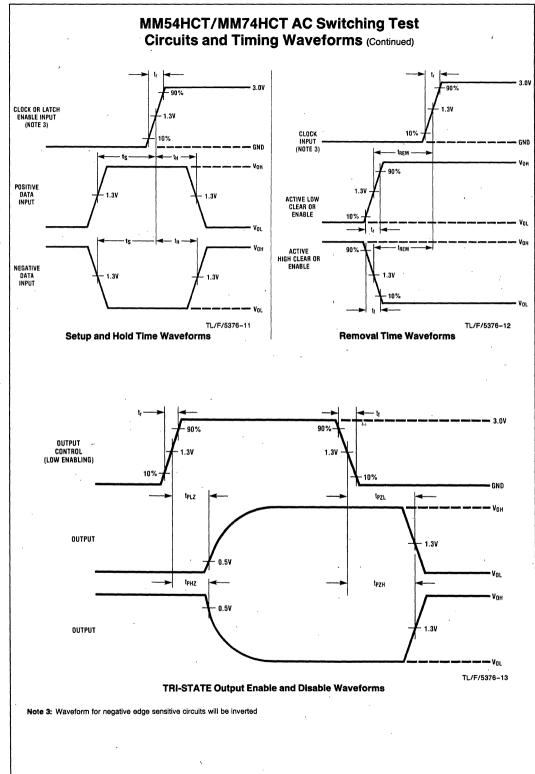

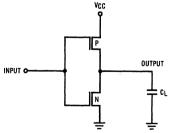

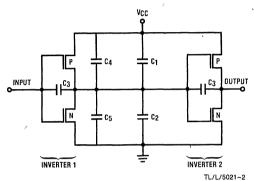

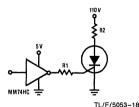

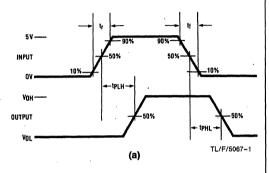

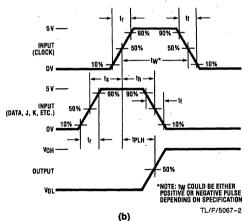

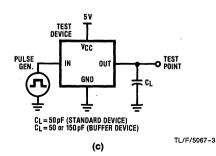

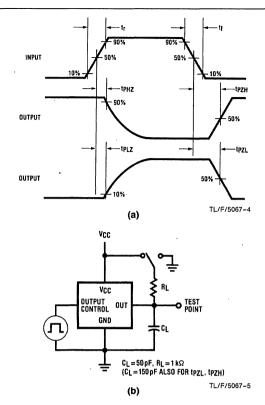

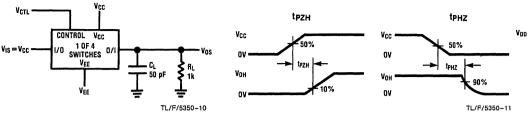

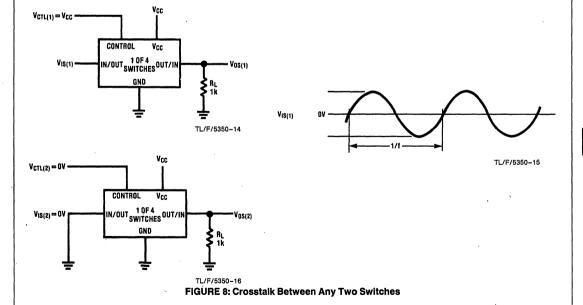

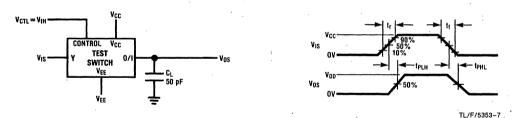

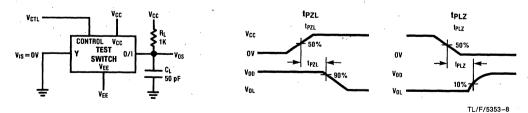

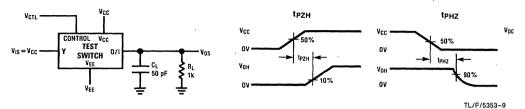

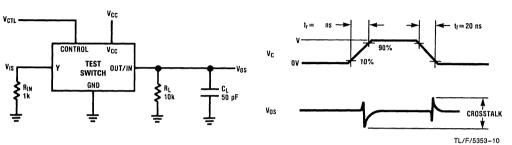

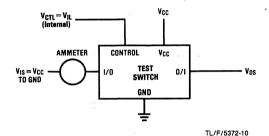

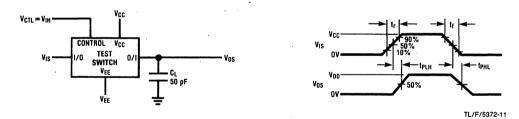

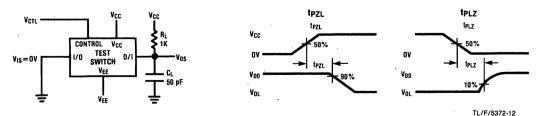

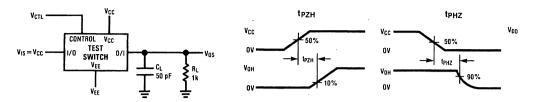

| AC Parameter Definitions1-2                                          |

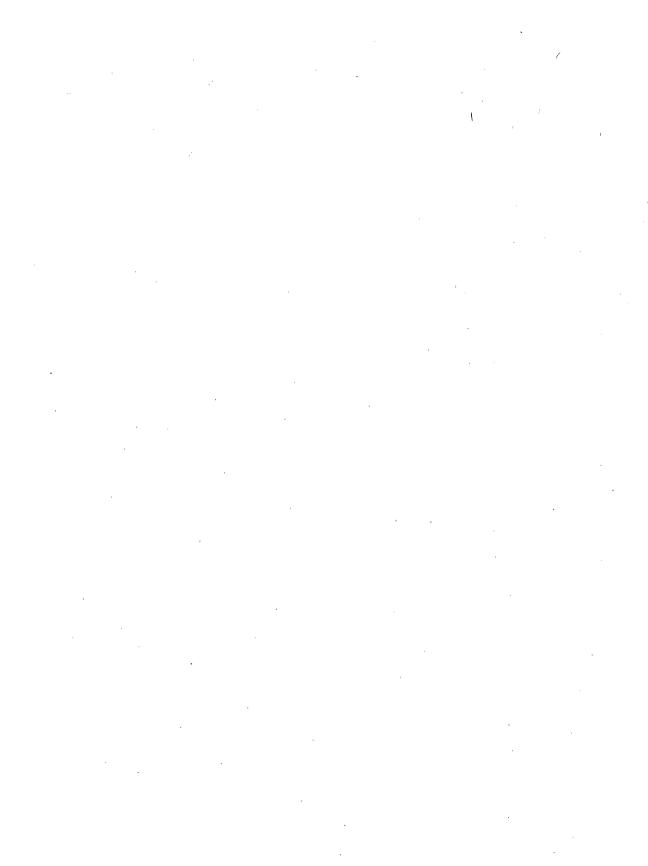

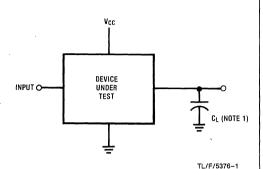

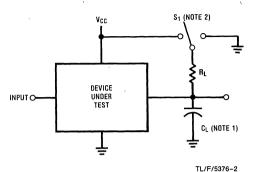

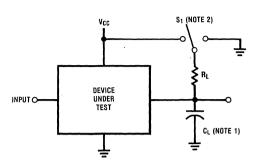

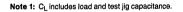

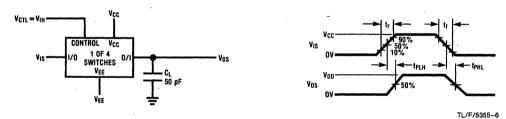

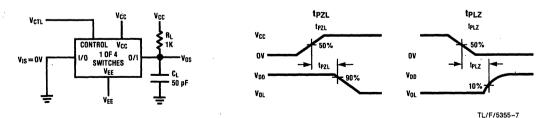

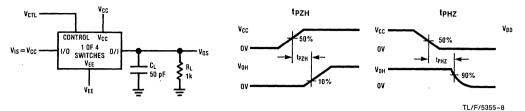

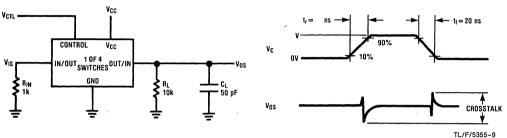

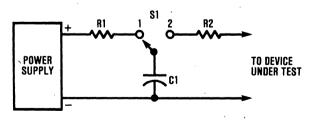

| MM54HC/MM74HC AC Switching Waveforms and Test Circuits1-3            |

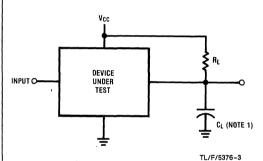

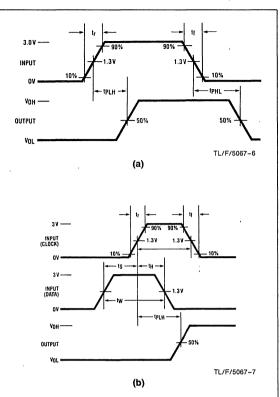

| MM54HCT/MM74HCT AC Switching Waveforms and Test Circuits             |

| SECTION 2 APPLICATION NOTES                                          |

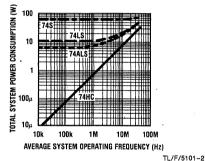

| AN-303 HC-CMOS Power Dissipation                                     |

| AN-310 High Speed CMOS Processing                                    |

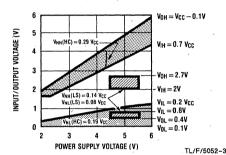

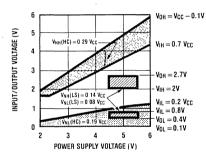

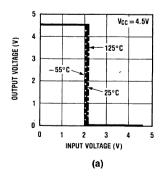

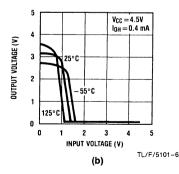

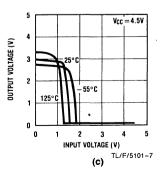

| AN-313 DC Electrical Characteristics of MM54HC/MM74HC CMOS2-15       |

| AN-314 Interfacing MM54HC/MM74HC High Speed CMOS Logic               |

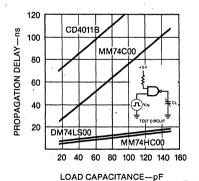

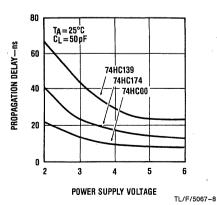

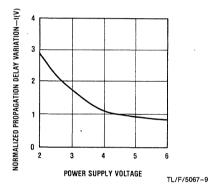

| AN-317 AC Electrical Characteristics of High Speed CMOS              |

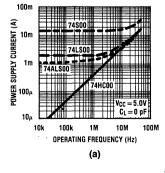

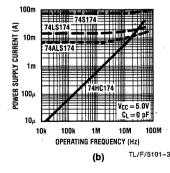

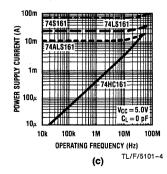

| AN-319 Comparison of HC-CMOS, LS-TTL, ALS-TTL and S-TTL              |

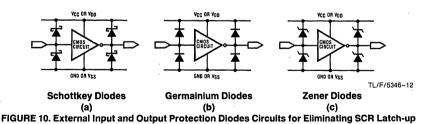

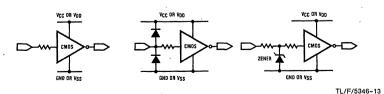

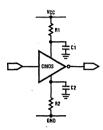

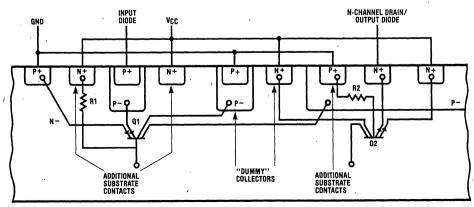

| AN-339 Understanding SCR Latch Up in MM54HC/MM74HC CMOS Circuits2-43 |

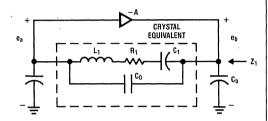

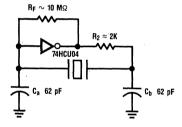

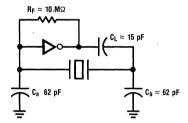

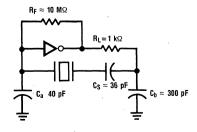

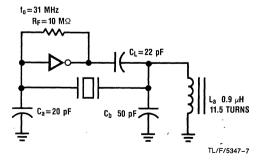

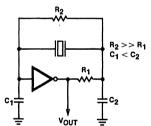

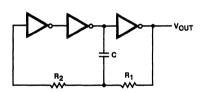

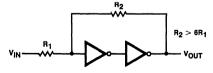

| AN-340 Crystal oscillators Using High Speed CMOS Circuits            |

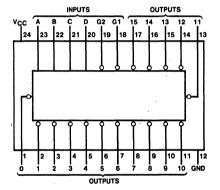

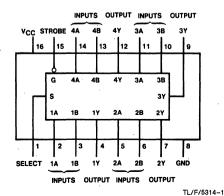

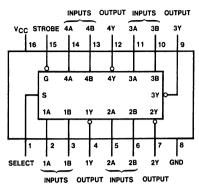

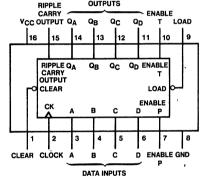

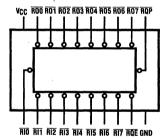

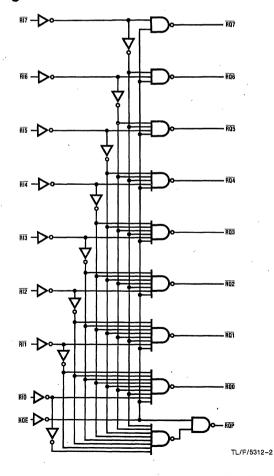

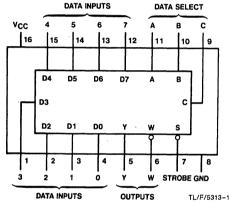

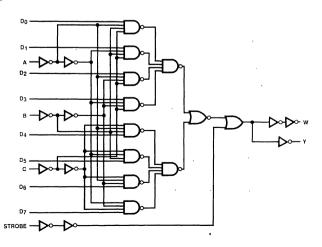

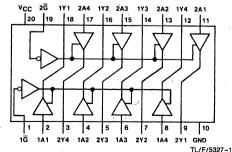

| SECTION 3 CONNECTION DIAGRAMS                                        |

| SECTION 4 MM54HC/MM74HC DATA SHEETS                                  |

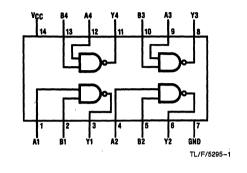

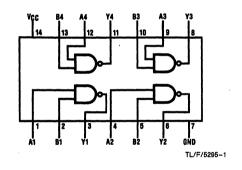

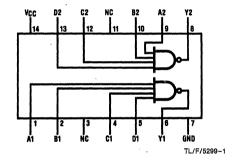

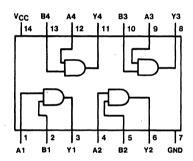

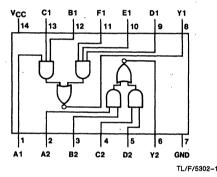

| MM54HC00/MM74HC00 Quad 2-Input NAND Gate                             |

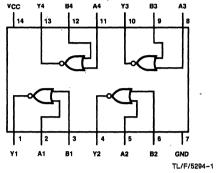

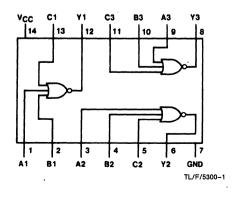

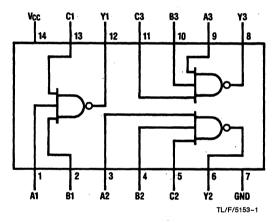

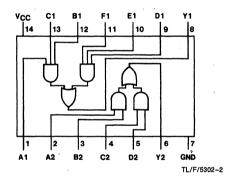

| MM54HC02/MM74HC02 Quad 2-Input NOR Gate4-5                           |

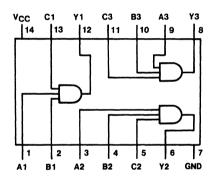

| MM54HC03/MM74HC03 Quad 2-Input Open Drain NAND Gate                  |

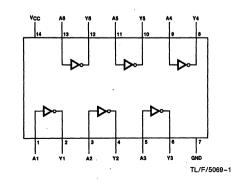

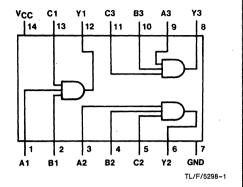

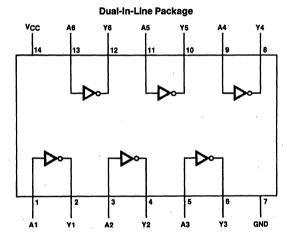

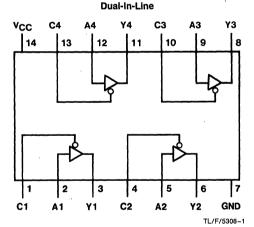

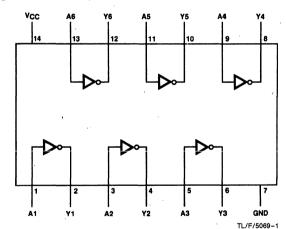

| MM54HCU04/MM74HCU04 Hex Inverter (Unbuffered)                        |

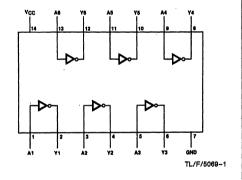

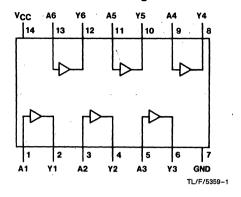

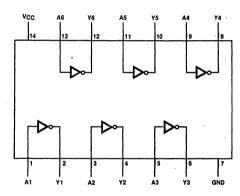

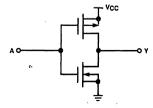

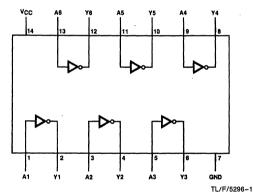

| MM54HC04/MM74HC04 Hex Inverter4-14                                   |

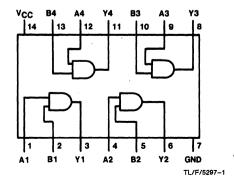

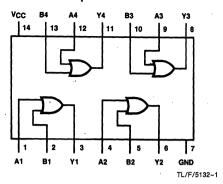

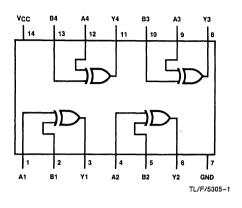

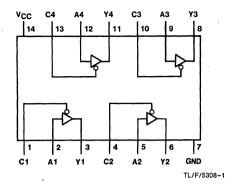

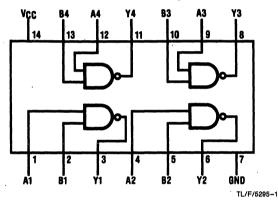

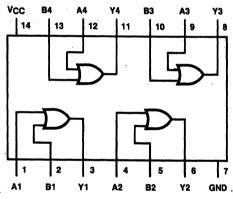

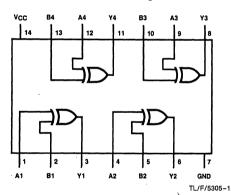

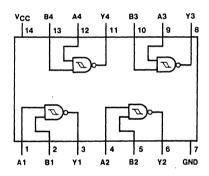

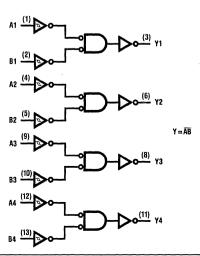

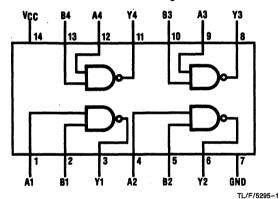

| MM54HC08/MM74HC08 Quad 2-Input AND Gate4-17                          |

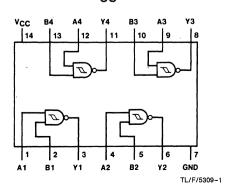

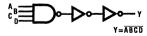

| MM54HC10/MM74HC10 Triple 3-Input NAND Gate4-20                       |

| MM54HC11 Triple 3-Input AND Gate4-23                                 |

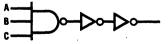

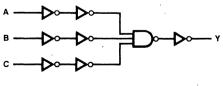

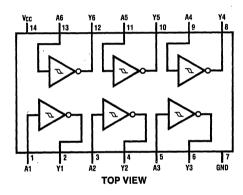

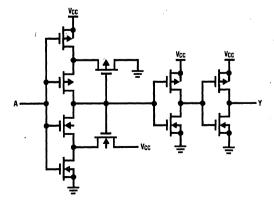

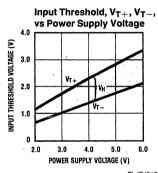

| MM54HC14/MM74HC14 Hex Schmitt Trigger4-26                            |

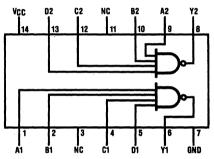

| MM54HC20/MM74HC20 Dual 4-Input NAND Gate4-29                         |

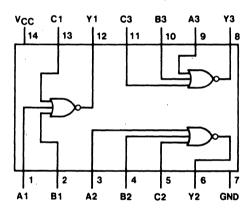

| MM54HC27/MM74HC27 Triple 3-Input NOR Gate4-32                        |

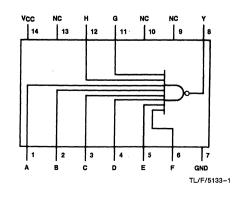

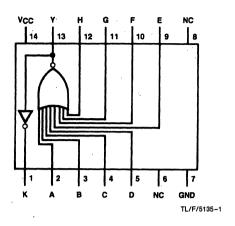

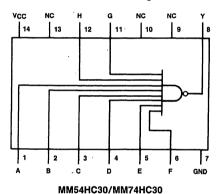

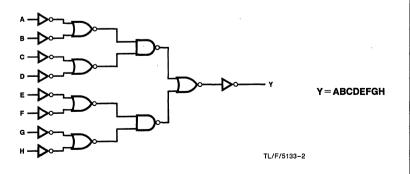

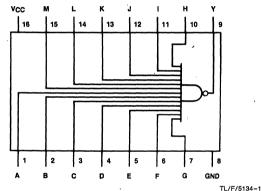

| MM54HC30/MM74HC30 8-Input NAND Gate                                  |

| MM54HC32/MM74HC32 Quad 2-Input OR Gate                               |

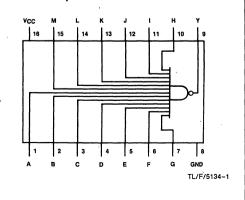

| MM54HC42/MM74HC42 BCD-to-Decimal Decoder                             |

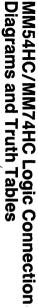

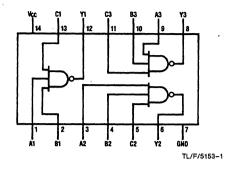

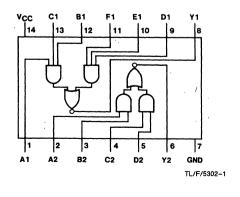

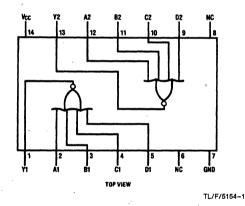

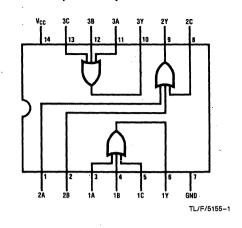

| MM54HC51/MM74HC51 Dual AND-OR-Invert Gate                            |

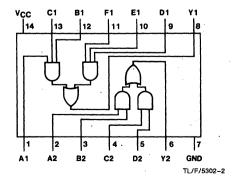

| MM54HC58/MM74HC58 Dual AND-OR Gate4-4-4                              |

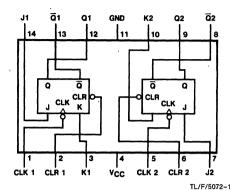

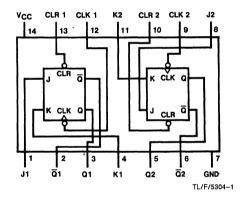

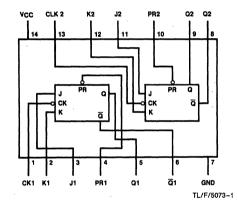

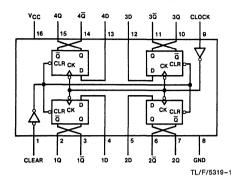

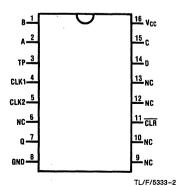

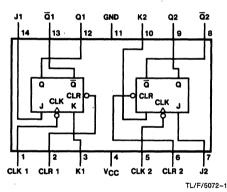

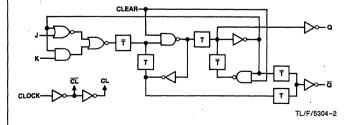

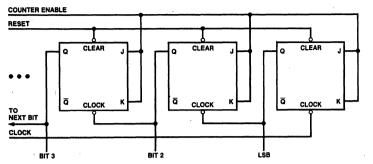

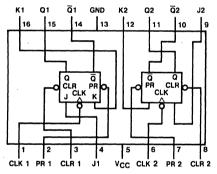

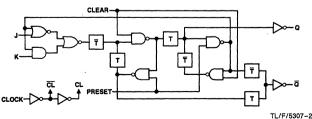

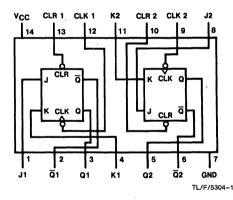

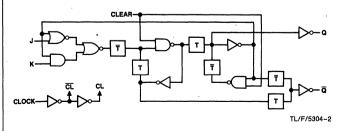

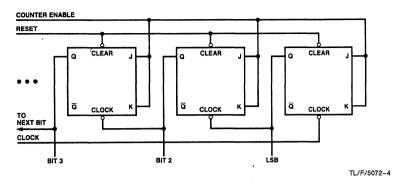

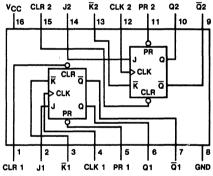

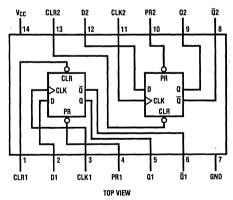

| MM54HC73/MM74HC73 Dual J-K Flip-Flop with Clear                      |

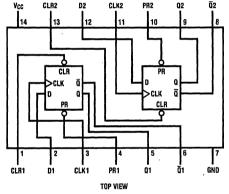

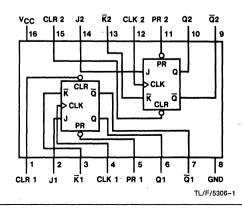

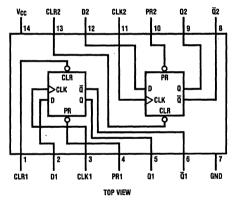

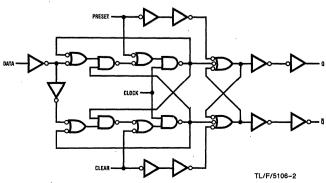

| MM54HC74/MM74HC74 Dual D Flip-Flop with Preset and Clear             |

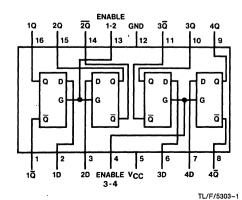

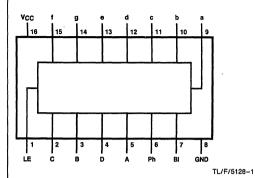

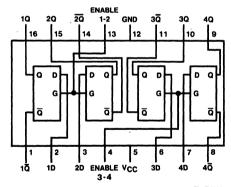

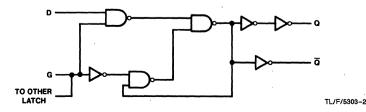

| MM54HC75/MM74HC75 4-Bit Bistable Latch with Q and Q4-54              |

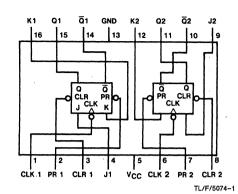

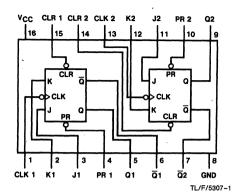

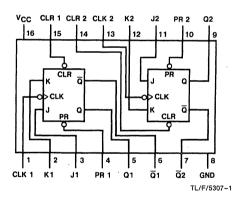

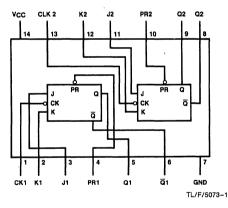

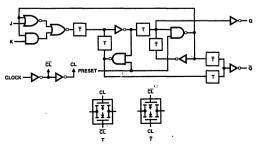

| MM54HC76/MM74HC76 Dual J-K Flip-Flop with Preset and Clear           |

|                                                                      |

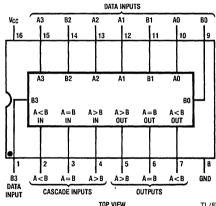

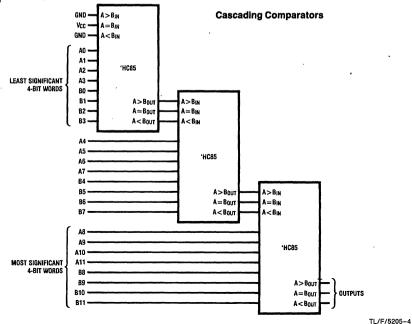

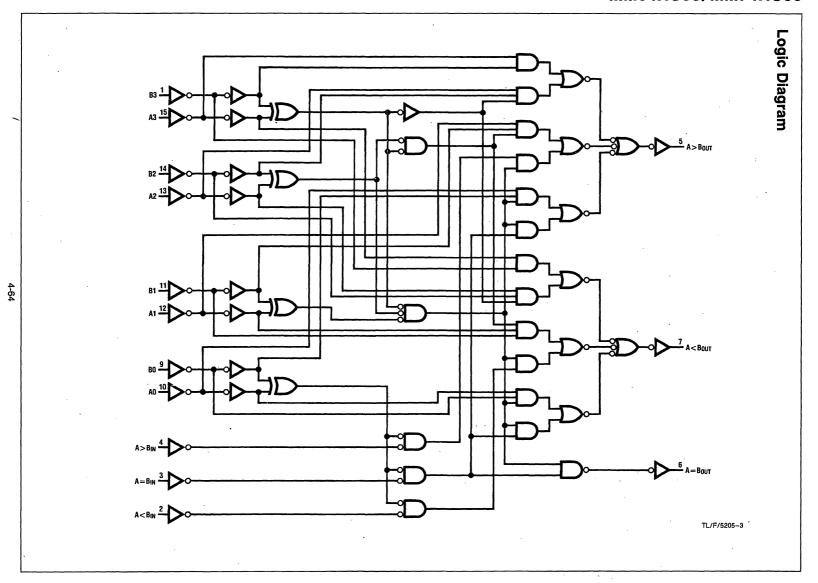

| MM54HC85/MM74HC85 4-Bit Magnitude Comparator                          |

|-----------------------------------------------------------------------|

| MM54HC86/MM74HC86 Quad Exclusive OR Gate                              |

| MM54HC107/MM74HC107                                                   |

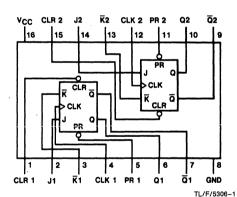

| MM54HC109/MM74HC109 Dual J-L Flip-Flop with Preset and Clear          |

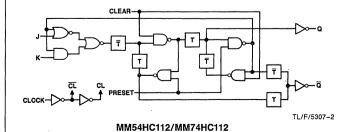

| MM54HC112/MM74HC112 Dual J-K Flip-Flop with Preset and Clear          |

| MM54HC113/MM74HC113 Dual J-K Flip-Flop with Preset4-79                |

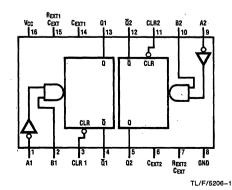

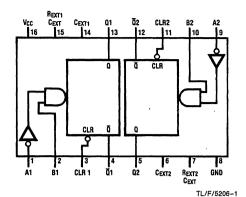

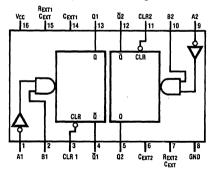

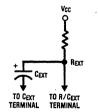

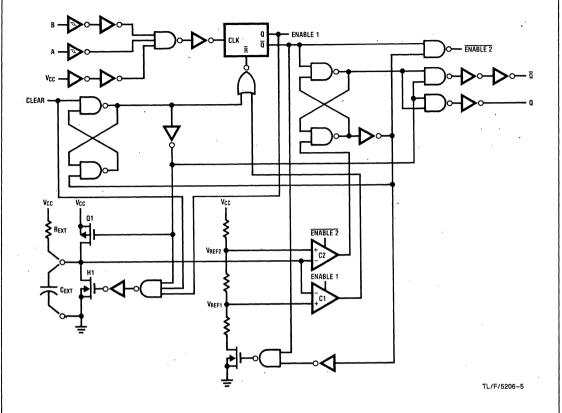

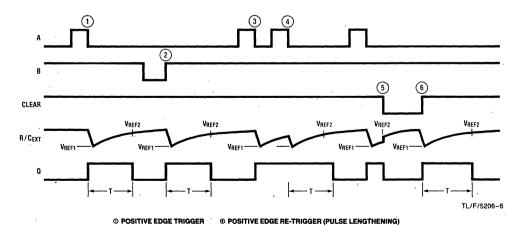

| MM54HC123/MM74HC123 Dual Retriggerable Monostable Multivibrator       |

| MM54HC125/MM74HC125 Quad Tri-State Buffers                            |

| MM54HC126/MM74HC126 Quad Tri-State Buffers                            |

| MM54HC132/MM74HC132 Quad 2-Input Schmitt Trigger                      |

| MM54HC133/MM74HC133 13-Input NAND Gate                                |

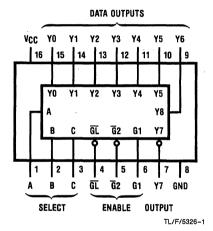

| MM54HC137/MM74HC137 3-to-8 Line Decoder with Address Latches          |

| MM54HC138/MM74HC138 3-to-8 Line Decoder                               |

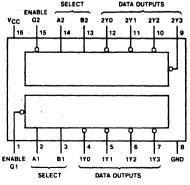

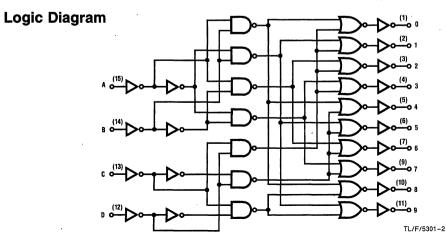

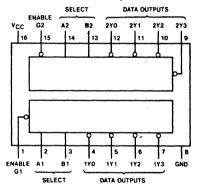

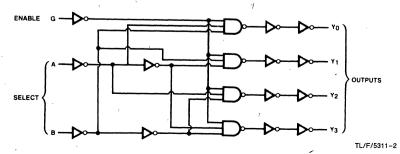

| MM54HC139/MM74HC139 Dual 2-to-4 Line Decoder                          |

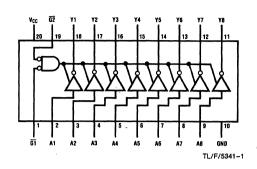

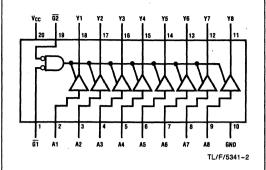

| MM54HC147/MM74HC147 10-to-4 Line Priority Encoder                     |

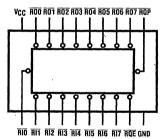

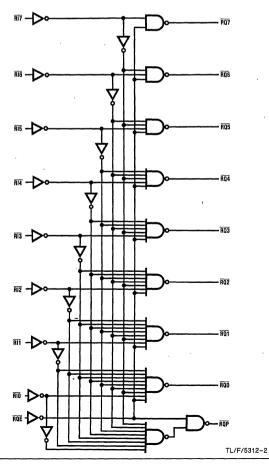

| MM54HC149/MM74HC149 8-to-8 Line Priority Encoder                      |

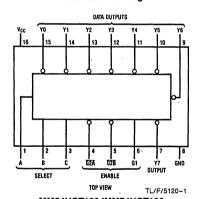

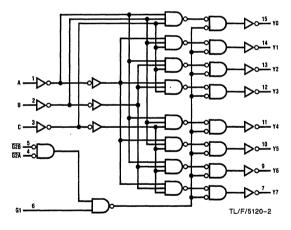

| MM54HC151/MM74HC151 8 Channel Multiplexer                             |

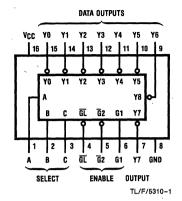

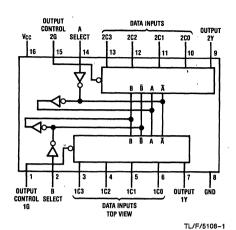

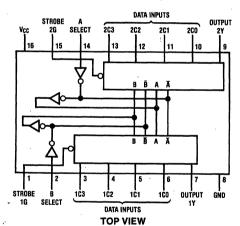

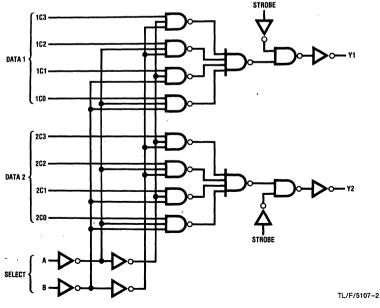

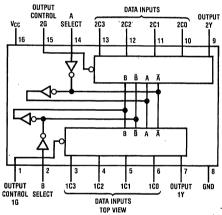

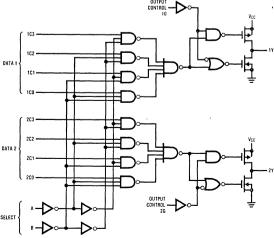

| MM54HC153/MM74HC153                                                   |

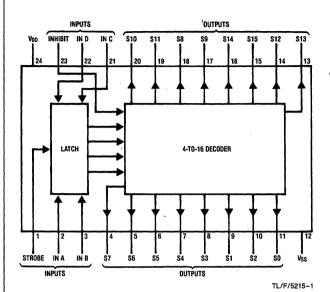

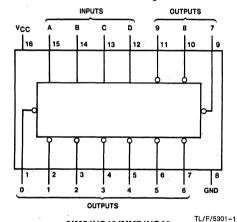

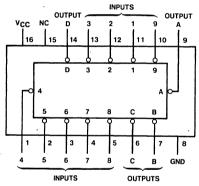

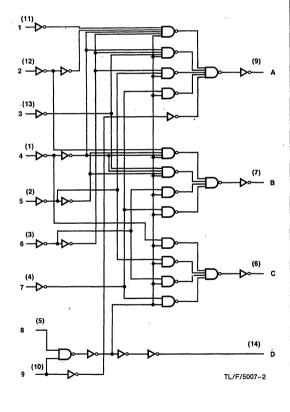

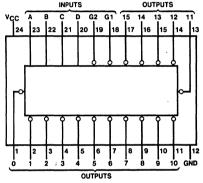

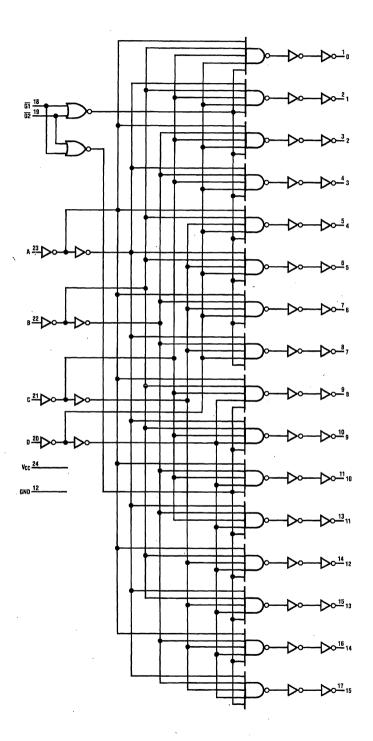

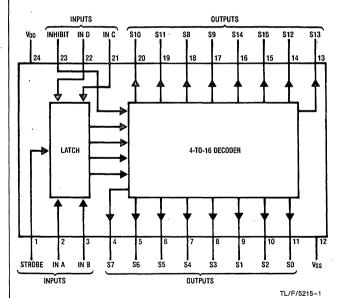

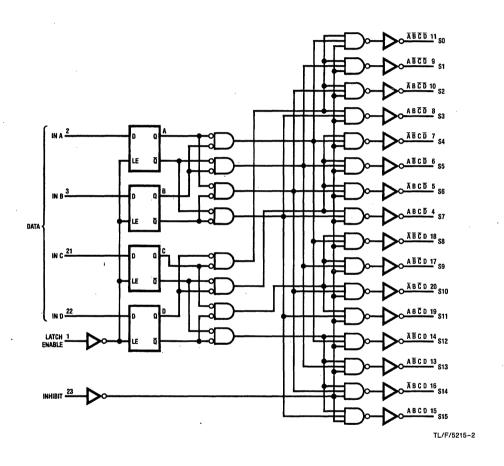

| MM54HC154/MM74HC154 4-to-16 Line Decoder                              |

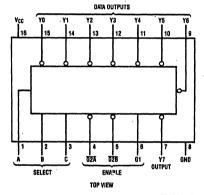

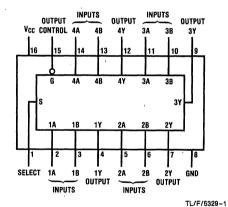

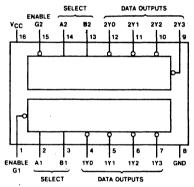

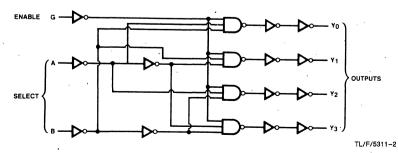

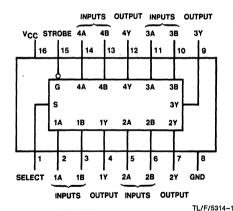

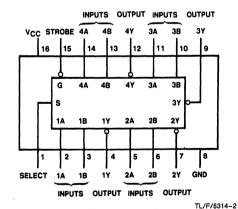

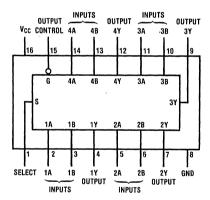

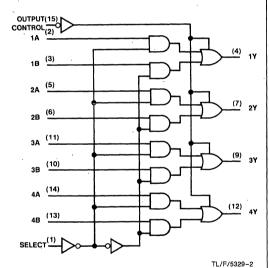

| MM54HC157/MM74HC157    Quad 2 Channel Multiplexer                     |

| MM54HC158/MM74HC158 Quad 2 Channel Multiplexer with Inverting Outputs |

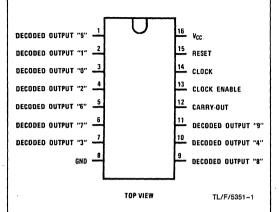

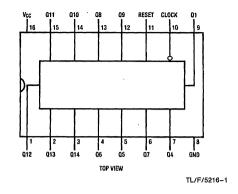

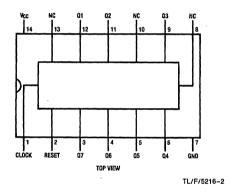

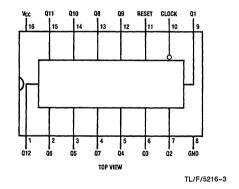

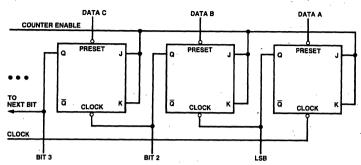

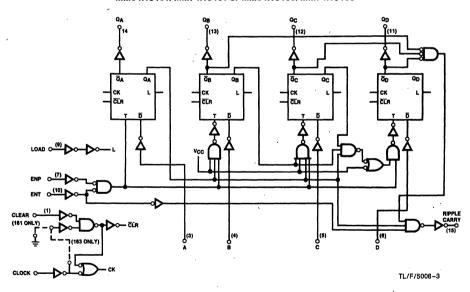

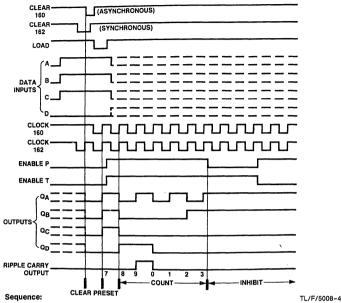

| MM54HC160/MM74HC160 4-Bit Synchronous Decade Counter                  |

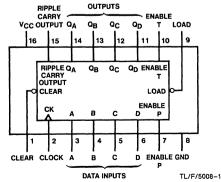

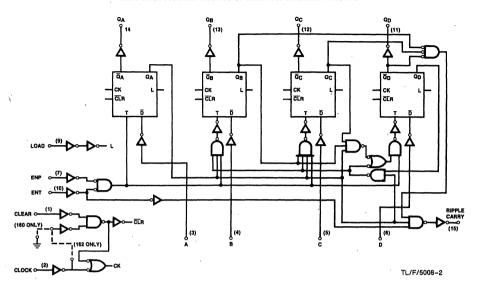

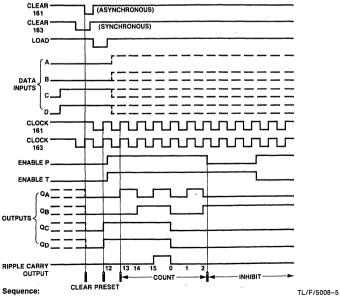

| MM54HC161/MM74HC161 4-Bit Synchronous Binary Counter4-127             |

| MM54HC162/MM74HC162 4-Bit Synchronous Decade Counter                  |

| MM54HC163/MM74HC163 4-Bit Synchronous Binary Counter                  |

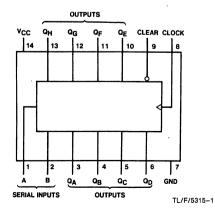

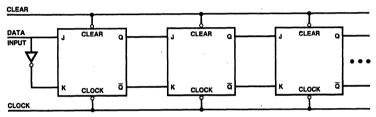

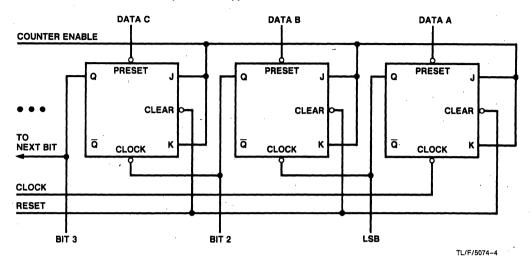

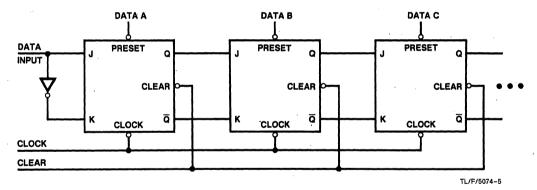

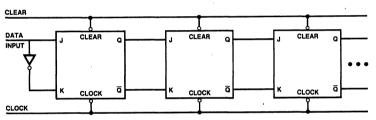

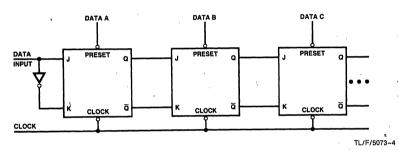

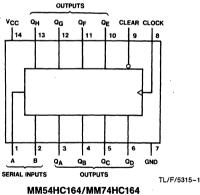

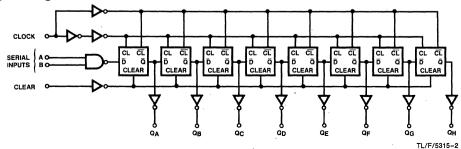

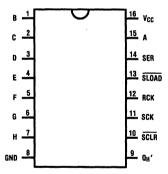

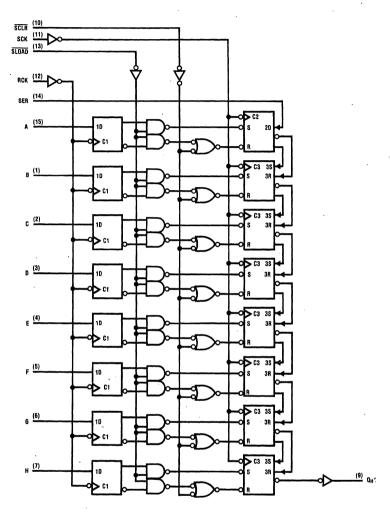

| MM54HC164/MM74HC164 8-Bit Serial-In Parallel-Out Shift Register       |

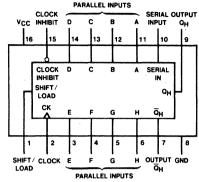

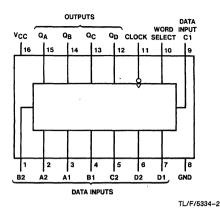

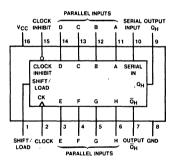

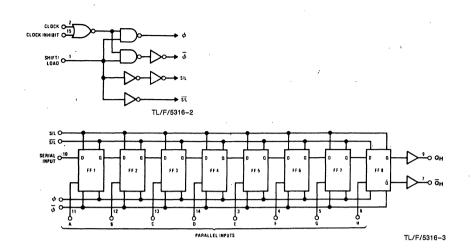

| MM54HC165/MM74HC165 8-Bit Parallel-In Serial-Out Shift Register       |

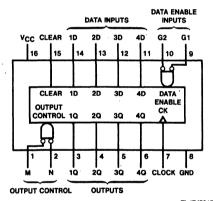

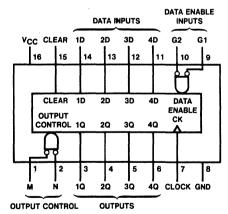

| MM54HC173/MM74HC173 Tri-State Quad D Flip-Flop                        |

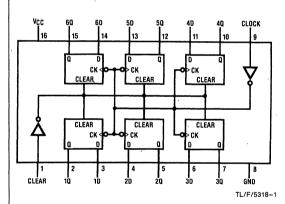

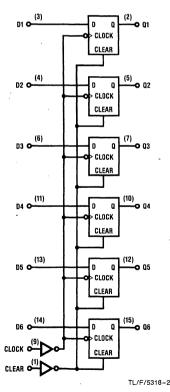

| MM54HC174/MM74HC174 Hex D Flip-Flop with Clear                        |

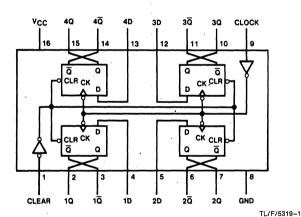

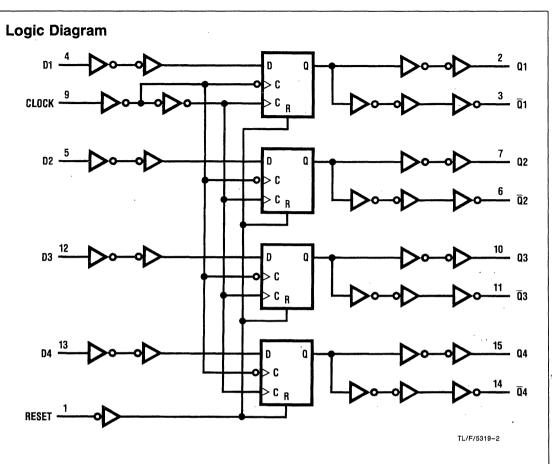

| MM54HC175/MM74HC175                                                   |

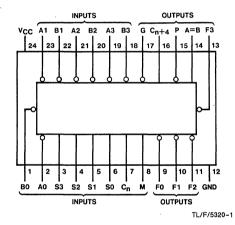

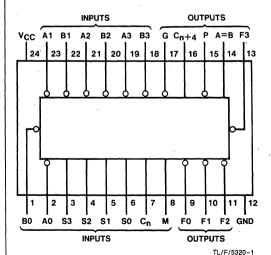

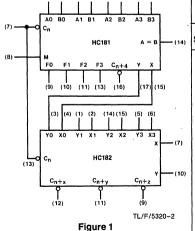

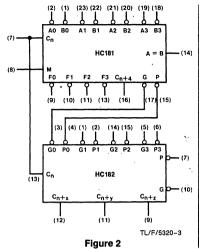

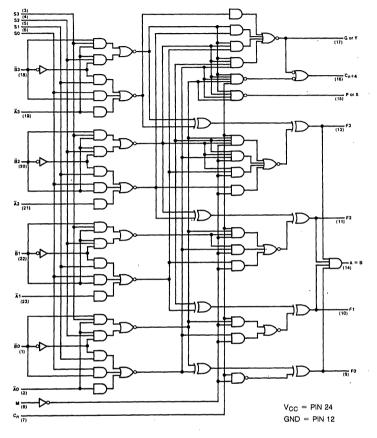

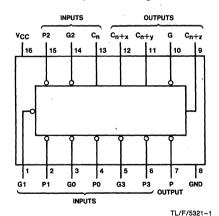

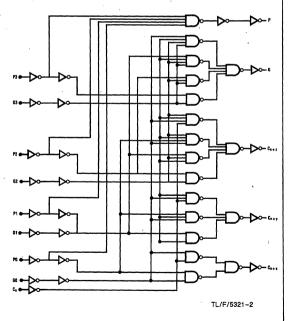

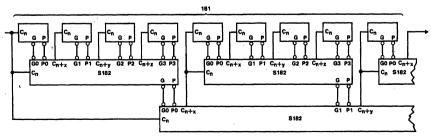

| MM54HC181/MM74HC181 4-Bit Arithmetic/Logic Unit                       |

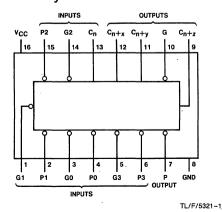

| MM54HC182/MM74HC182 4-Bit Look Ahead Carry Generator                  |

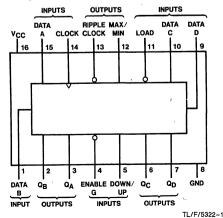

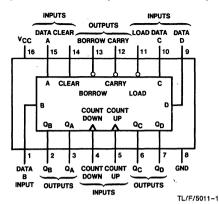

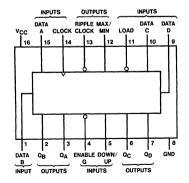

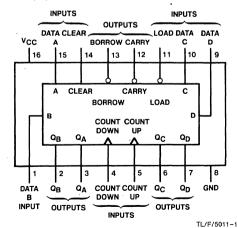

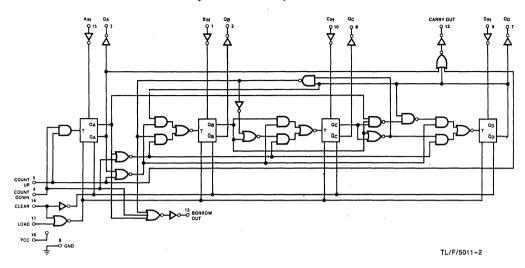

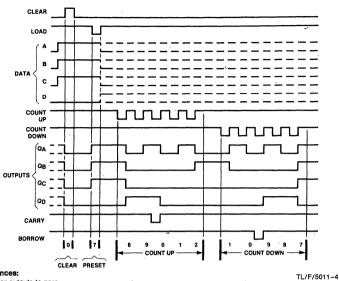

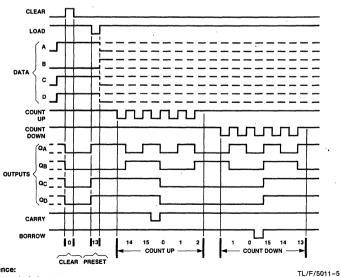

| MM54HC190/MM74HC190 4-Bit Synchronous Decade Up/Down Counter          |

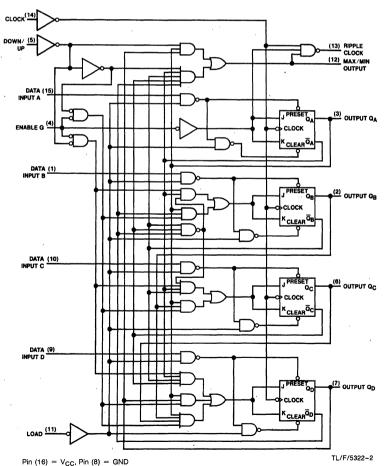

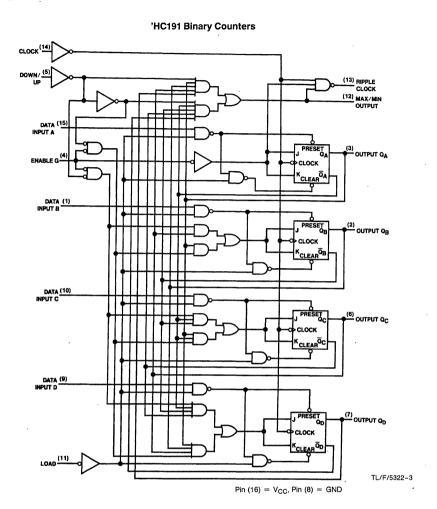

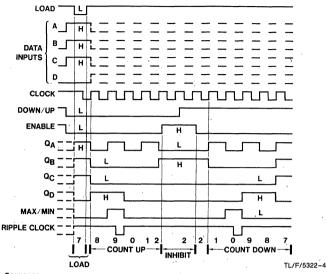

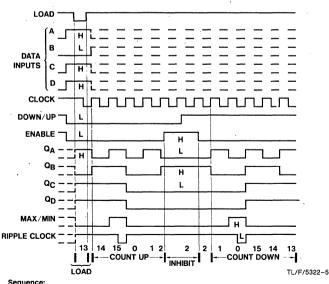

| MM54HC191/MM74HC191 4-Bit Synchronous Binary Up/Down Counter          |

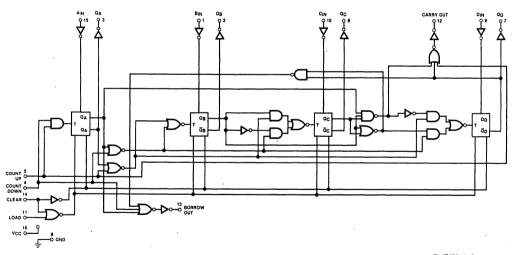

| MM54HC192/MM74HC192 4-Bit Synchronous Decade Up/Down Counter          |

| MM54HC193/MM74HC193 4-Bit Synchronous Binary Up/Down Counter          |

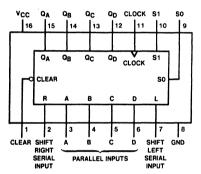

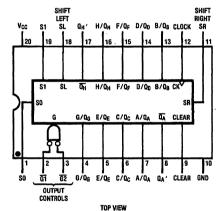

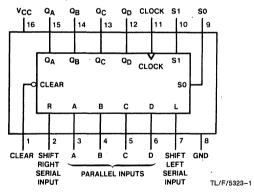

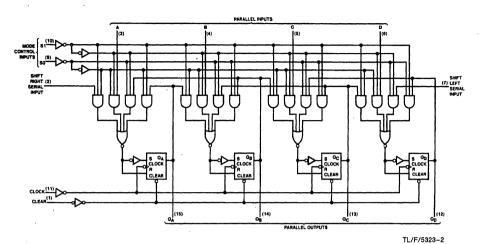

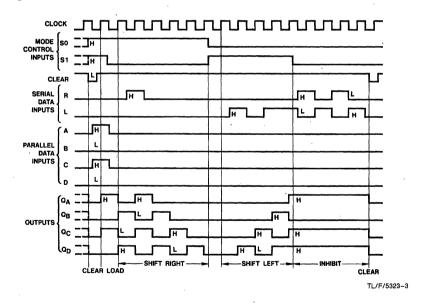

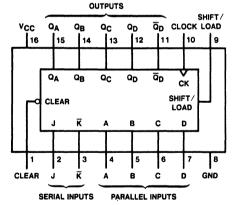

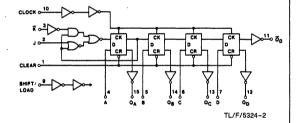

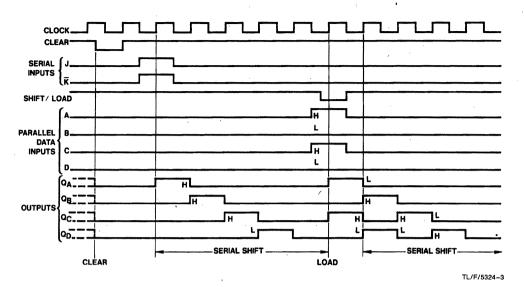

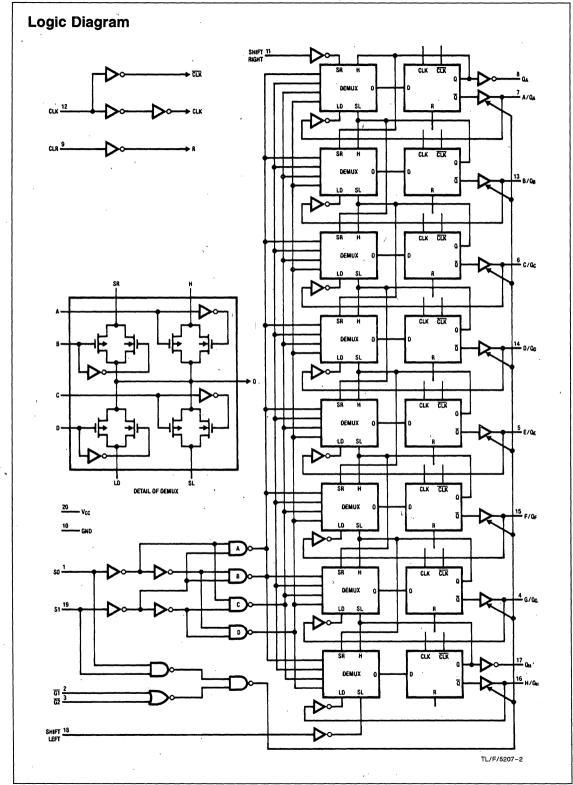

| MM54HC194/MM74HC194 4-Bit Bidirectional Shift Register                |

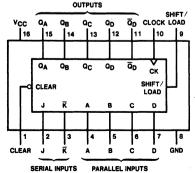

| MM54HC195/MM74HC195 4-Bit Parallel-In Shift Register                  |

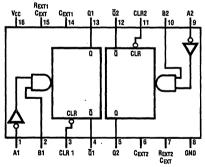

| MM54HC221/MM74HC221 Dual Monostable Multivibrator                     |

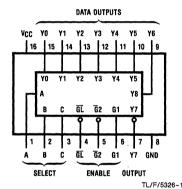

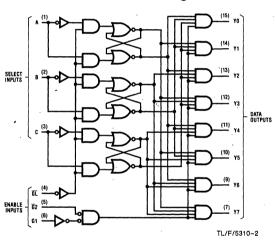

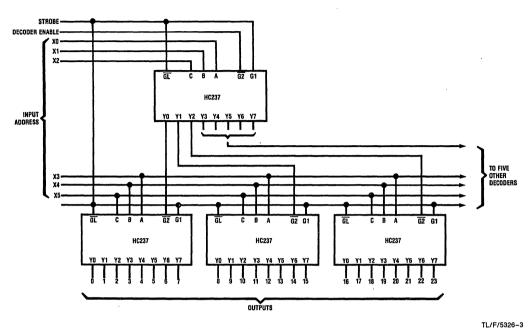

| MM54HC237/MM74HC237 3-to-8 Decoder with Address Latches               |

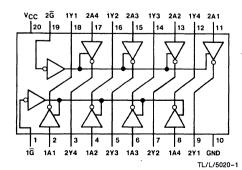

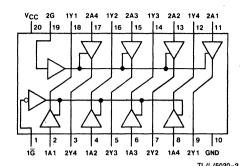

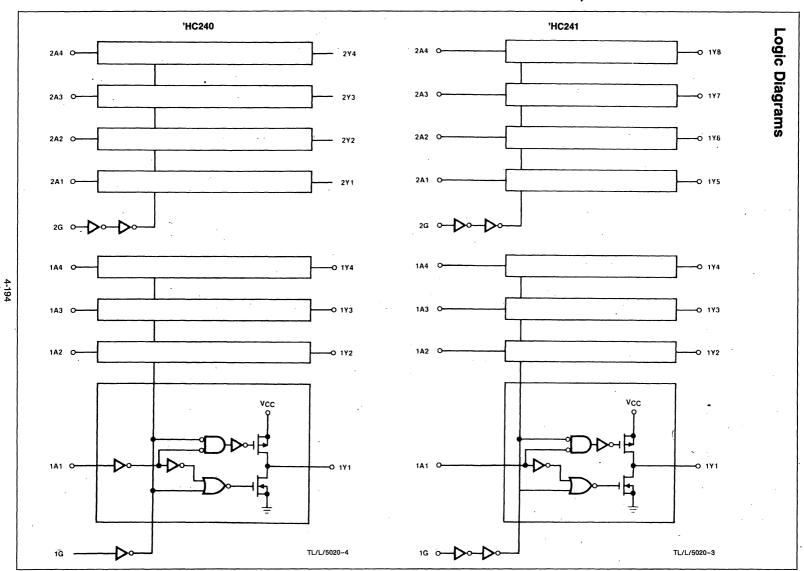

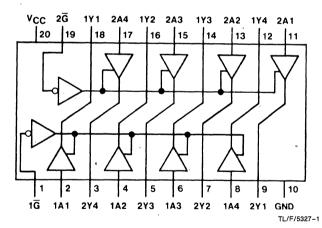

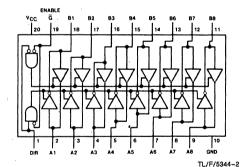

| MM54HC240/MM74HC240 Inverting Octal Tri-State Buffer                  |

| MM54HC241/MM74HC241 Octal Tri-State Buffer                            |

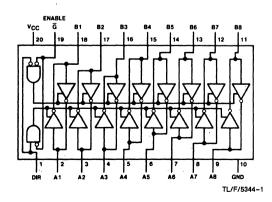

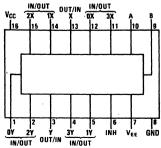

| MM54HC242/MM74HC242 | Inverting Quad Tri-State Transceivers4-195                         |

|---------------------|--------------------------------------------------------------------|

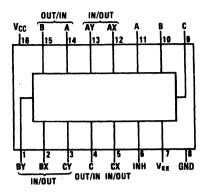

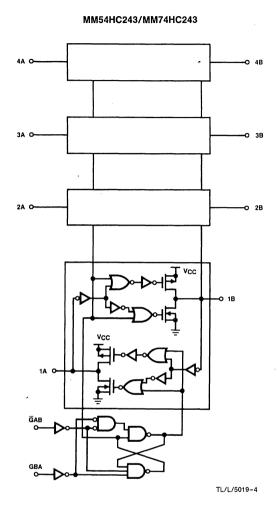

| MM54HC243/MM74HC243 | Quad Tri-State Transceivers                                        |

| MM54HC244/MM74HC244 | Octal Tri-State Buffer4-200                                        |

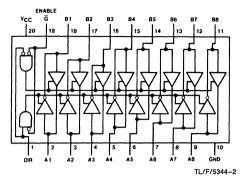

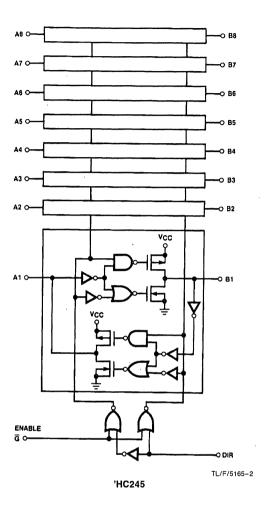

| MM54HC245/MM74HC245 | Octal Bidirectional Transceiver4-204                               |

| MM54HC251/MM74HC251 | 8 Channel Tri-State Multiplexer4-208                               |

| MM54HC253/MM74HC253 | Dual 4 Channel Tri-State Multiplexer                               |

| MM54HC257/MM74HC257 | Quad 2 Channel Tri-State Multiplexer                               |

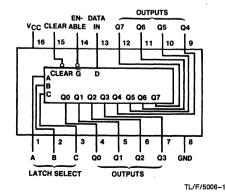

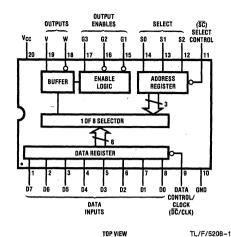

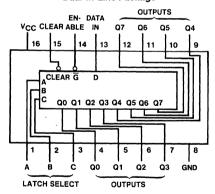

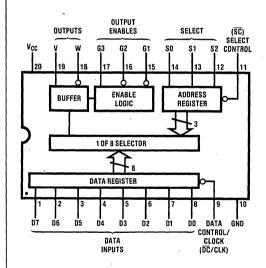

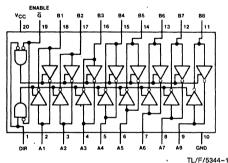

| MM54HC259/MM74HC259 | 8-Bit Addressable Latch                                            |

| MM54HC266/MM74HC266 | Quad 2-Input Exclusive NOR Gate4-221                               |

| MM54HC273/MM74HC273 | Octal D Flip-Flop with Clear4-224                                  |

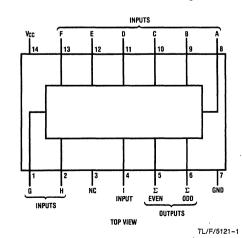

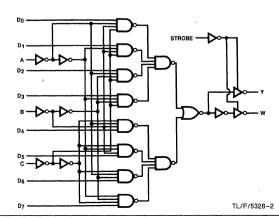

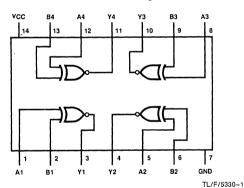

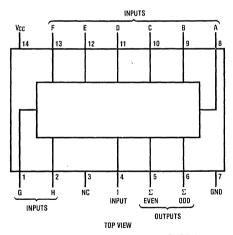

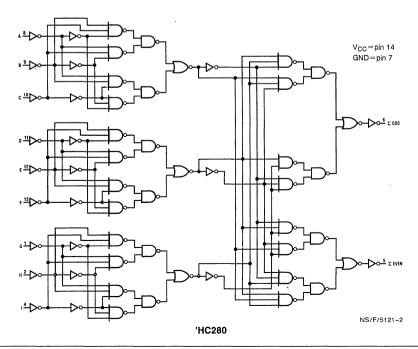

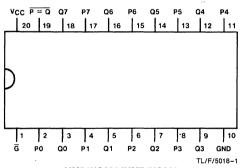

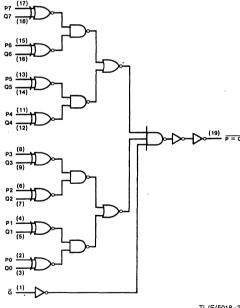

| MM54HC280/MM74HC280 | 9-Bit Odd/Even Parity Generator4-227                               |

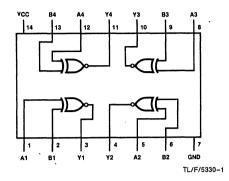

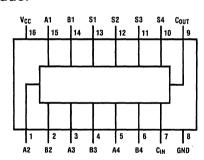

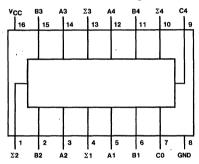

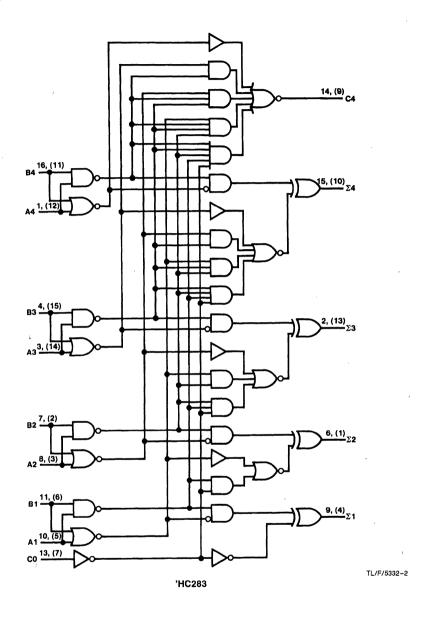

| MM54HC283/MM74HC283 | 4-Bit Binary Adder4-230                                            |

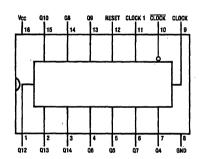

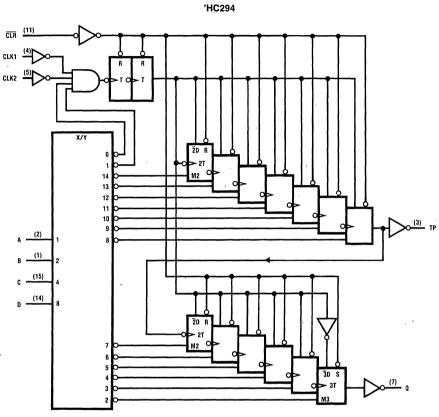

| MM54HC292/MM74HC292 | 31-Bit Programmable Frequency Divider4-234                         |

| MM54HC294/MM74HC294 | 15-Bit Programmable Frequency Divider4-234                         |

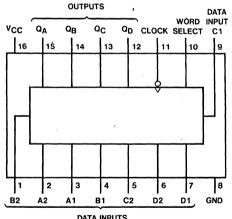

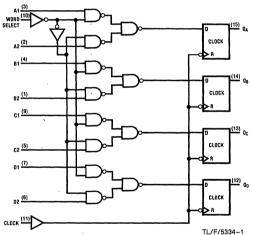

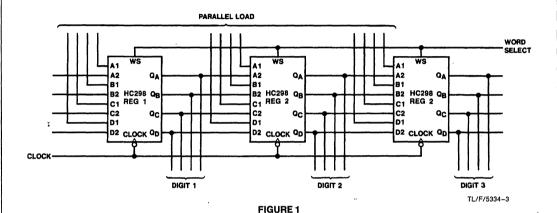

| MM54HC298/MM74HC298 | Quad 2 Channel Multiplexer with Latches4-240                       |

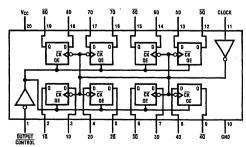

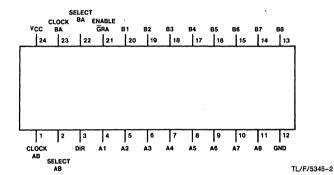

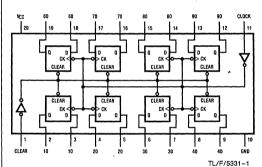

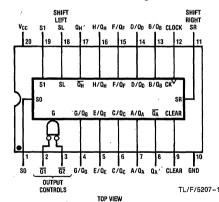

| MM54HC299/MM74HC299 | 8-Bit Universal Shift Register4-244                                |

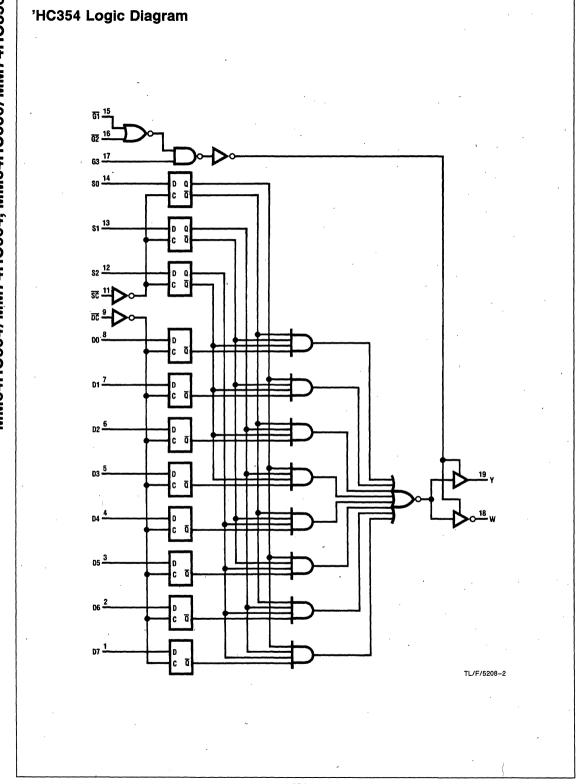

|                     | 8 Channel Tri-State Multiplexer with Latches4-249                  |

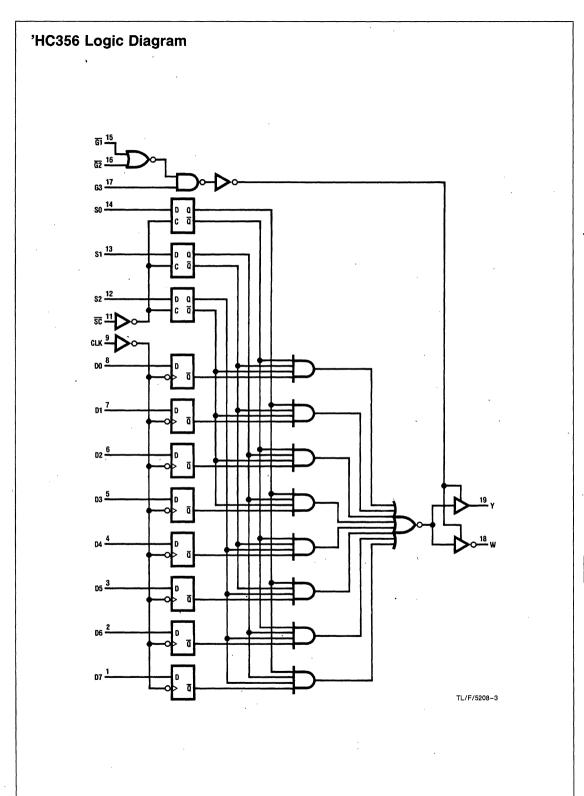

| MM54HC356/MM74HC356 | 8 Channel Tri-State Multiplexer with Latches                       |

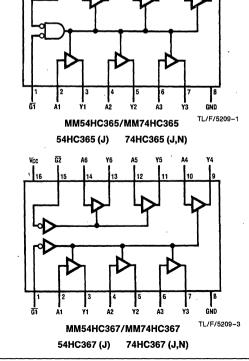

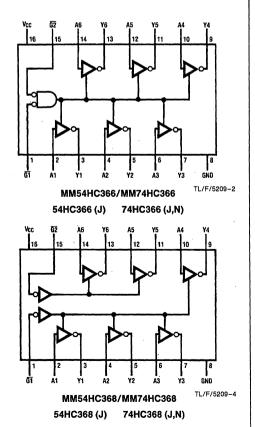

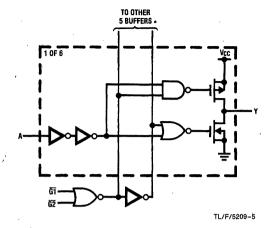

| MM54HC365/MM74HC365 | Hex Tri-State Buffer4-256                                          |

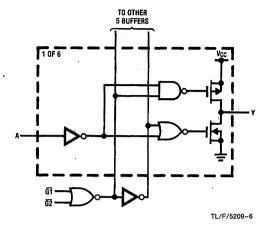

|                     | Inverting Hex Tri-State Buffer                                     |

| MM54HC367/MM74HC367 | Hex Tri-State Buffer         4-256                                 |

| MM54HC368/MM74HC368 | Inverting Hex Tri-State Buffer4-256                                |

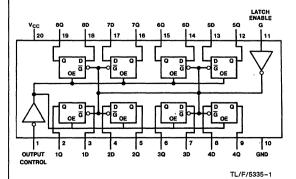

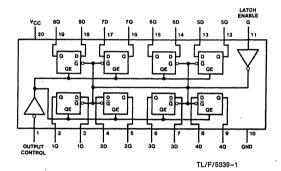

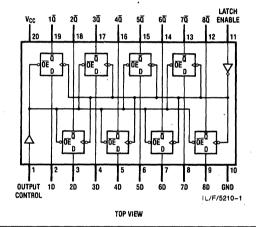

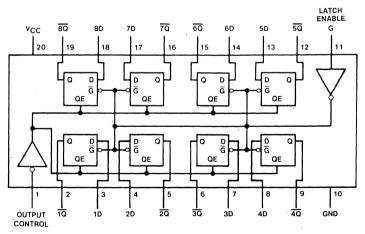

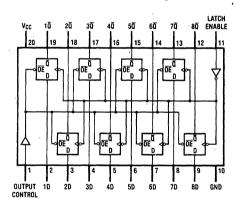

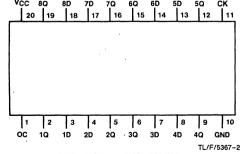

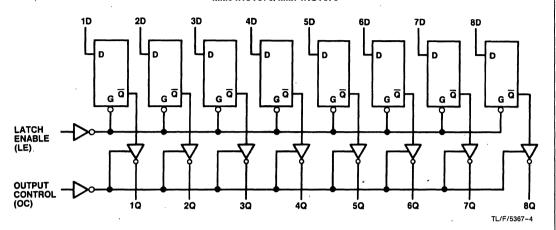

| MM54HC373/MM74HC373 | Octal Tri-State D Latch                                            |

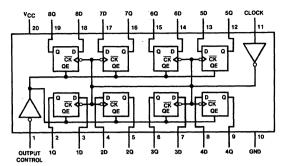

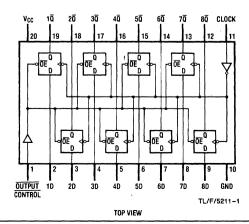

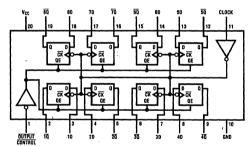

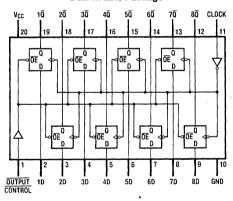

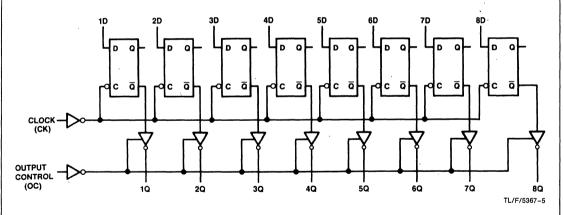

| MM54HC374/MM74HC374 | Octal Tri-State D Flip-Flop4-266                                   |

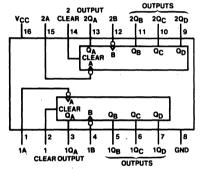

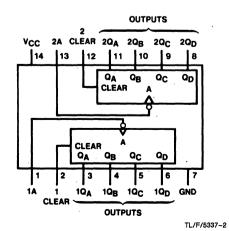

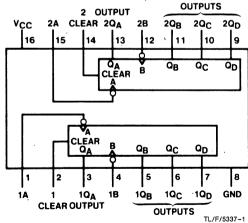

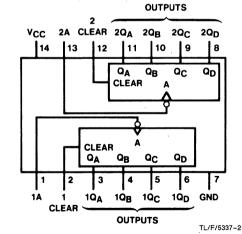

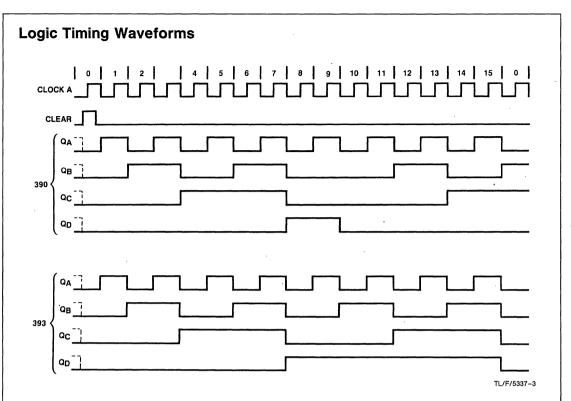

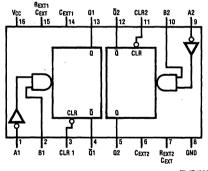

| MM54HC390/MM74HC390 | Dual 4-Bit Decade Counter                                          |

| MM54HC393/MM74HC393 | Dual 4-Bit Binary Counter        4-269                             |

| MM54HC423/MM74HC423 | Dual Retriggerable Monostable Multivibrator4-274                   |

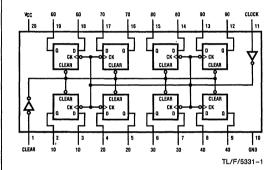

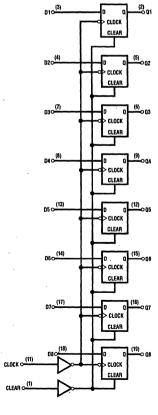

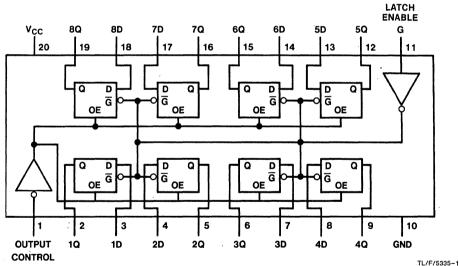

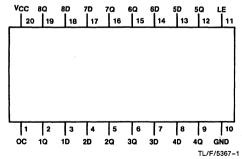

| MM54HC533/MM74HC533 | Octal Tri-State D Latch with Inverting Outputs4-279                |

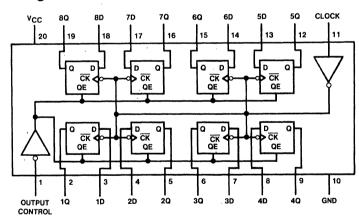

|                     | Octal Tri-State D Flip-Flop with Inverting Outputs                 |

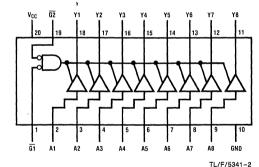

| MM54HC540/MM74HC540 | Inverting Octal Tri-State Buffer4-285                              |

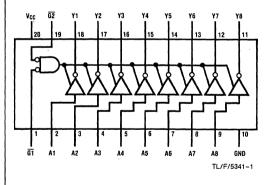

| MM54HC541/MM74HC541 | Octal Tri-State Buffer4-285                                        |

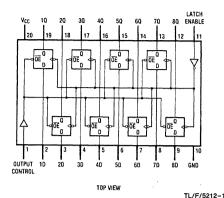

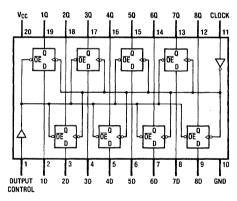

| MM54HC563/MM74HC563 | Octal Tri-State D Latch with Inverting Outputs4-288                |

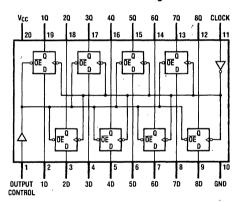

| MM54HC564/MM74HC564 | Octal Tri-State D Flip-Flop with Inverting Outputs                 |

| MM54HC573/MM74HC573 | Octal Tri-State D Latch4-294                                       |

| MM54HC574/MM74HC574 | Octal Tri-State D Flip-Flop4-297                                   |

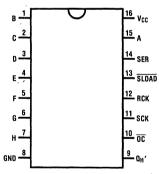

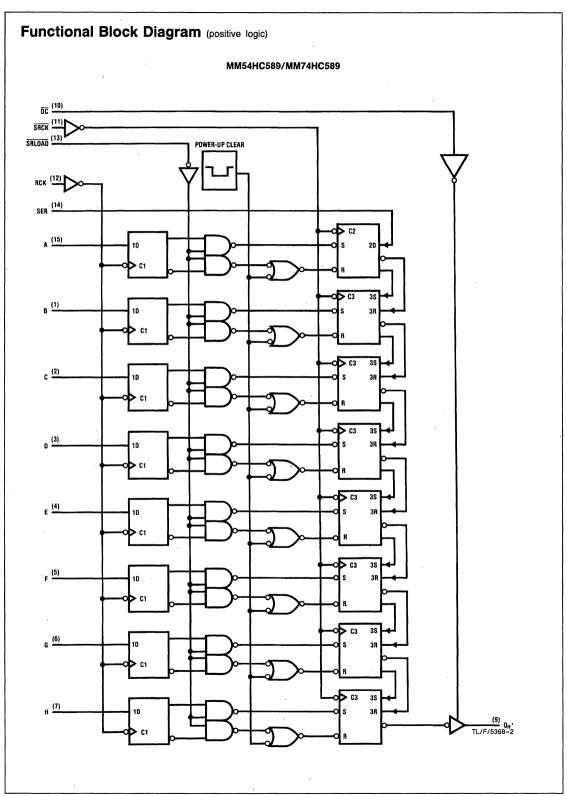

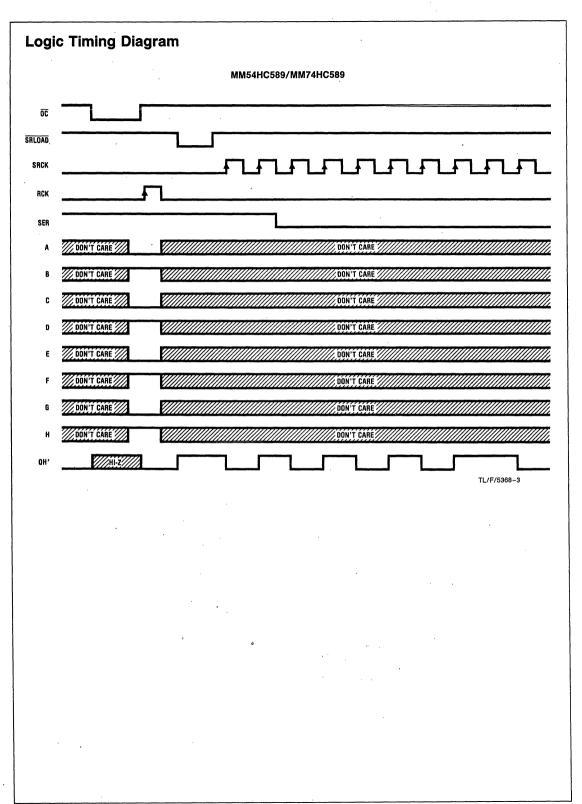

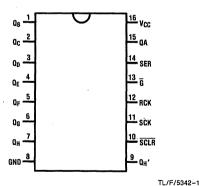

| MM54HC589/MM74HC589 | 8-Bit Tri-State Parallel-In Serial-Out Shift Register with Latches |

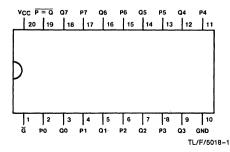

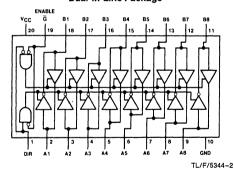

| MM54HC595/MM74HC595 | 8-Bit Tri-State Serial-In Parallel-Out Shift Register with Latches |

|                     | 8-Bit Tri-State Serial-In Parallel-Out Shift Register with Latches |

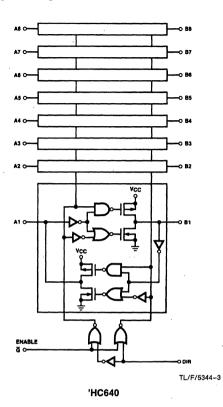

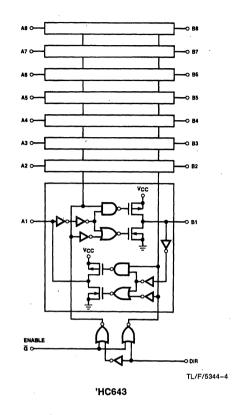

| MM54HC640/MM74HC640 | Inverting Octal Tri-State Transceiver                              |

| MM54HC643/MM74HC643 | True/Inverting Octal Tri-State Transceiver                         |

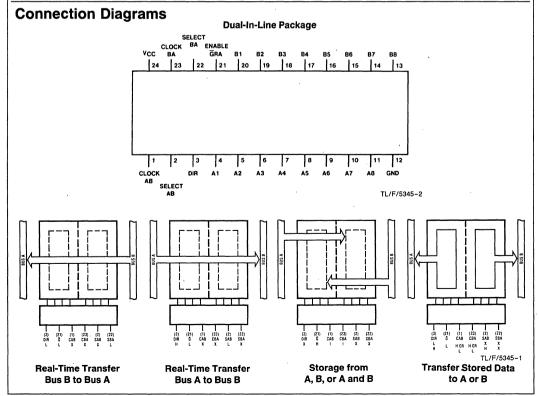

| i i                 | Octal Tri-State Bus Transceiver/Latch                              |

| MM54HC648/MM74HC648 | Inverting Octal Tri-State Bus Transceiver/Latch                    |

|                     |                                                                    |

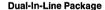

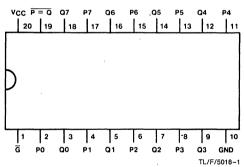

| MM54HC688/MM74HC688 8-Bit Equality Comparator                                           |

|-----------------------------------------------------------------------------------------|

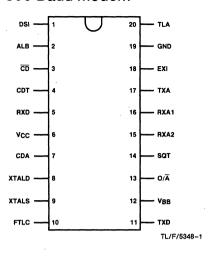

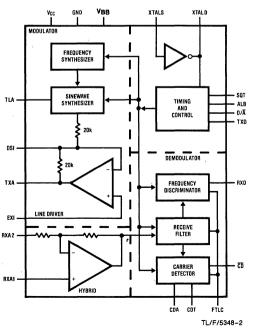

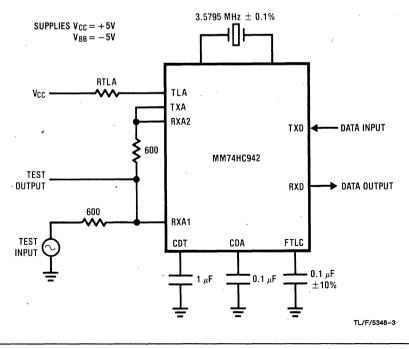

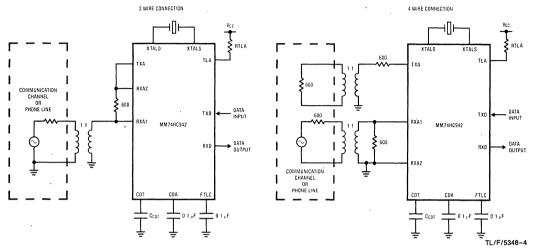

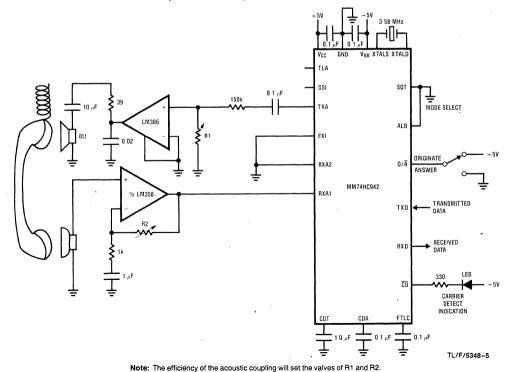

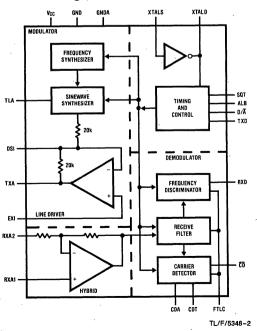

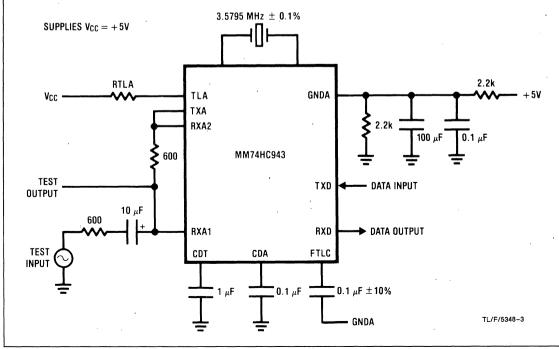

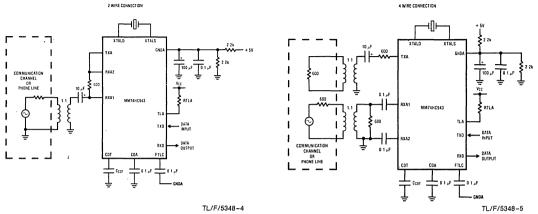

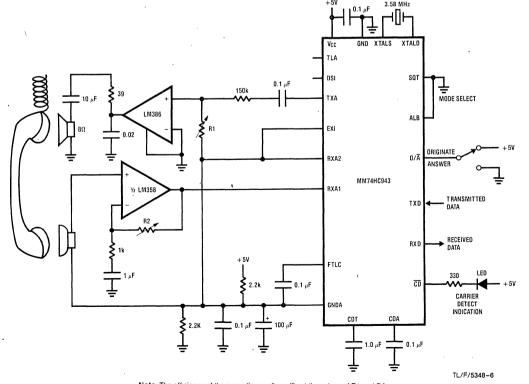

| MM74HC942 300 Baud Modem (+5, -5 Volt Supply)                                           |

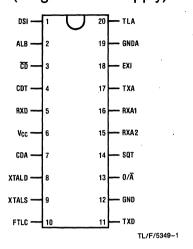

| MM74HC943 300 Baud Modem (5 Volt Supply)                                                |

| MM54HC4002/MM74HC4002 Dual 4-Input NOR Gate                                             |

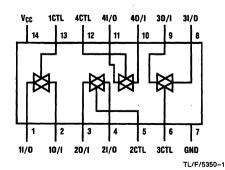

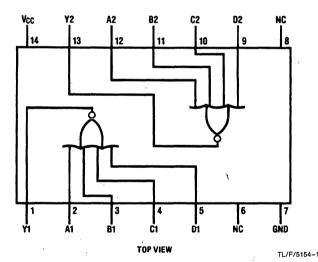

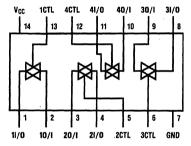

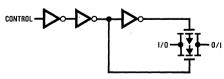

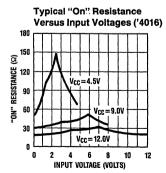

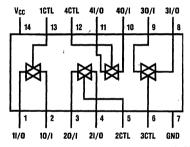

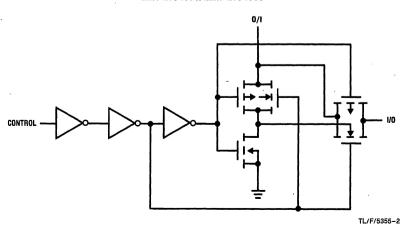

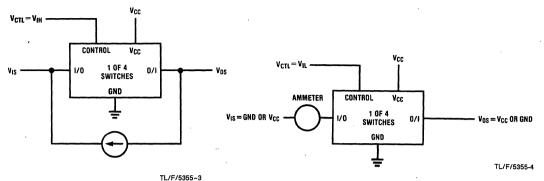

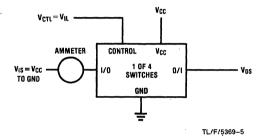

| MM54HC4016/MM74HC4016 Quad Bilateral Analog Switch                                      |

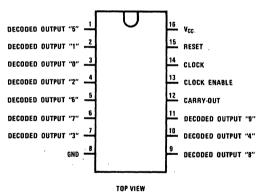

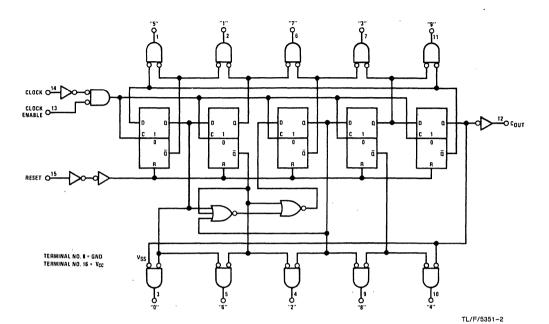

| MM54HC4017/MM74HC4017 Decade Counter Divider with 10 Decoded Outputs                    |

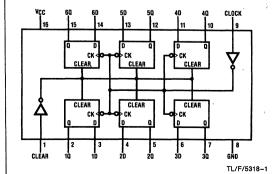

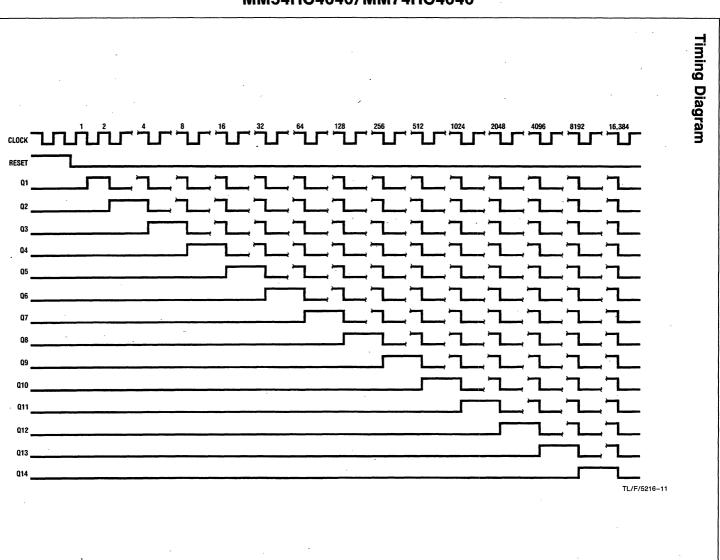

| MM54HC4020/MM74HC4020 14 Stage Binary Counter                                           |

| MM54HC4024/MM74HC4024 7 Stage Binary Counter                                            |

| MM54HC4040/MM74HC4040 12 Stage Binary Counter                                           |

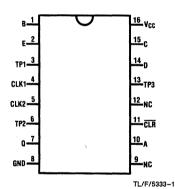

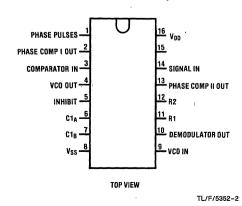

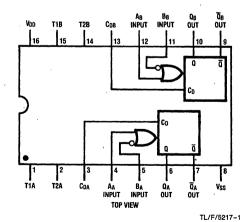

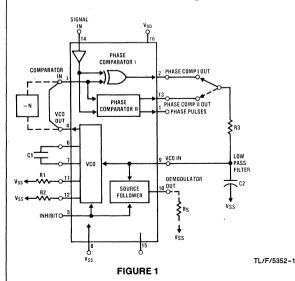

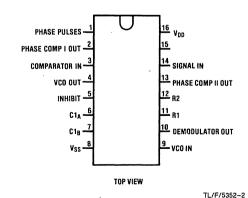

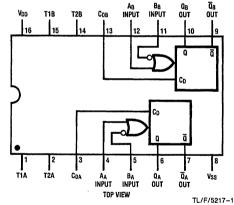

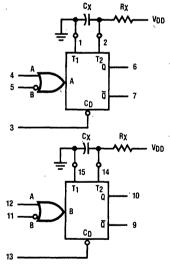

| MM54HC4046/MM74HC4046 Phase Lock Loop                                                   |

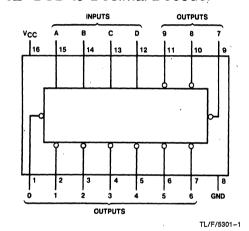

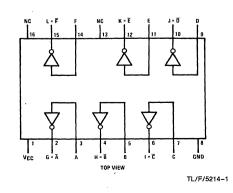

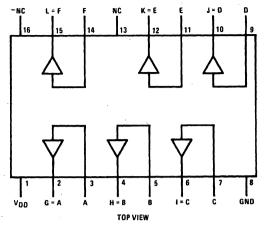

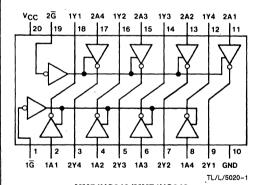

| MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                          |

| MM54HC4050/MM74HC4050 Hex Logic Down Converter                                          |

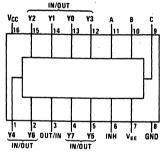

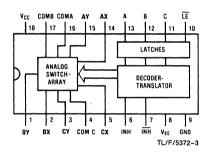

| MM54HC4051/MM74HC4051 8 Channel Analog Multiplexer                                      |

| MM54HC4052/MM74HC4052 Dual 4 Channel Analog Multiplexer                                 |

| MM54HC4053/MM74HC4053 Triple 2 Channel Analog Multiplexer                               |

| MM54HC4060/MM74HC4060 14 Stage Binary Counter                                           |

| MM54HC4066/MM74HC4066 Quad Bilateral Analog Switch                                      |

| MM54HC4075/MM74HC4075 Triple 3-Input OR Gate                                            |

| MM54HC4078/MM74HC4078 8-Input OR/NOR Gate                                               |

| MM54HC4316/MM74HC4316 Quad Bilateral Analog Switch                                      |

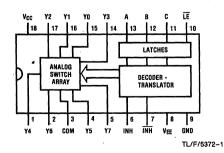

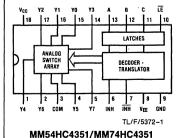

| MM54HC4351/MM74HC4351 8 Channel Analog Multiplexer with Latches                         |

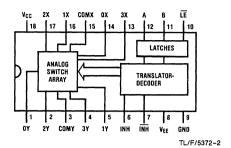

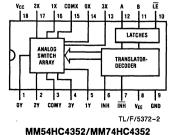

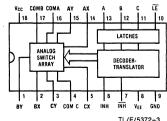

| MM54HC4352/MM74HC4352 Dual 4 Channel Analog Multiplexer with Latches                    |

| MM54HC4353/MM74HC4353 Triple 2 Channel Analog Multiplexer with Latches                  |

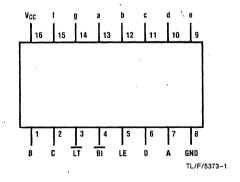

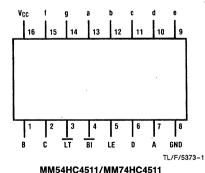

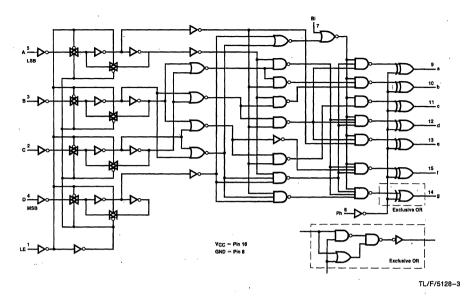

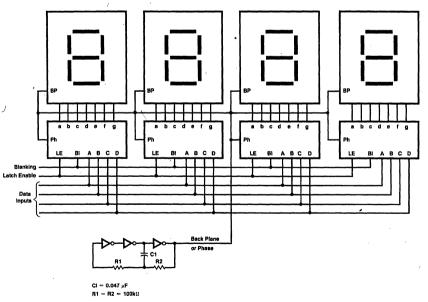

| MM54HC4511/MM74HC4511 BCD-to-7 Segment Latch/Decoder/Driver                             |

| MM54HC4514/MM74HC4514 4-to-16 Decoder with Address Latches                              |

| MM54HC4538/MM74HC4538 Dual Retriggerable Monostable Multivibrator                       |

| MM54HC4543/MM74HC4543 BCD-to-7 Segment Latch/Decoder/Driver for Liquid Crystal Displays |

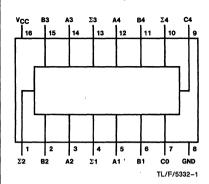

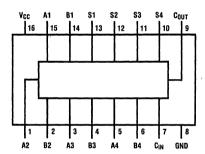

| MM54HC4560/MM74HC4560 4-Bit NBCD Adder                                                  |

|                                                                                         |

| SECTION 5 MM54HCT/MM74HCT DATA SHEETS                                                   |

| MM54HCT00/MM74HCT00 Quad 2-Input NAND Gate (TTL Input)                                  |

| MM54HCT04/MM74HCT04 Hex Inverter (TTL Input)                                            |

| MM54HCT05/MM74HCT05 Hex Inverter with Open Drain Outputs (TTL Input)                    |

| MM54HCT34/MM74HCT34 Hex Non-Inverting Gate (TTL Input)                                  |

| MM54HCT74/MM74HCT74 Dual D Flip-Flop with Preset (TTL Input)                            |

| MM54HCT109/MM74HCT109 Dual J-K Flip-Flop with Preset (TTL Input)                        |

| MM54HCT138/MM74HCT138 3-to-8 Line Decoder (TTL Input)                                   |

| MM54HCT139/MM74HCT139 Dual 2-to-8 Line Decoder (TTL Input)                              |

| MM54HCT149/MM74HCT149 8-to-8 Line Priority Encoder (TTL Input)                          |

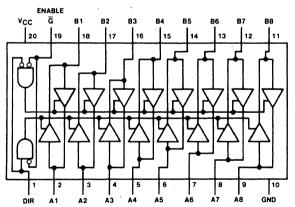

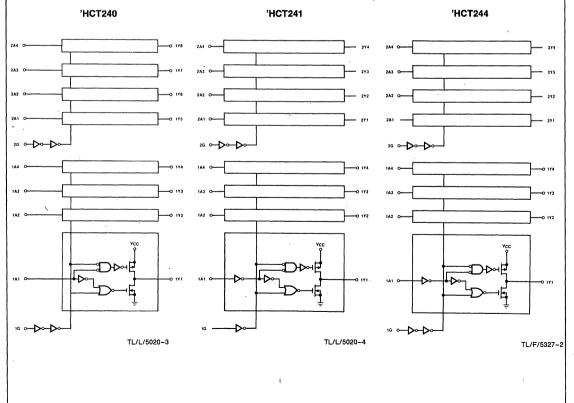

| MM54HCT240/MM74HCT240 Inverting Octal Tri-State Buffer (TTL Input)                      |

| MM54HCT241/MM74HCT241 Octal Tri-State Buffer (TTL Input)                                |

| MM54HCT244/MM74HCT244 Octal Tri-State Buffer (TTL Input)                                |

|                                                                                         |

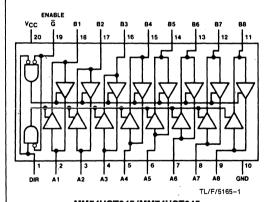

| MM54HCT245/MM74HCT245 Octal Bidirectional Transceiver (TTL Input)            | 5-32 |

|------------------------------------------------------------------------------|------|

| MM54HCT373/MM74HCT373 Octal Tri-State D Latch (TTL Input)                    | 5-35 |

| MM54HCT374/MM74HCT374 Octal Tri-State D Flip-Flop (TTL Input)                | 5-35 |

| MM54HCT640/MM74HCT640 Inverting Octal Tri-State Transceiver (TTL Input)      | 5-40 |

| MM54HCT643/MM74HCT643 True/Inverting Octal Tri-State Transceiver (TTL Input) | 5-40 |

| MM54HCT688/MM74HCT688 8-Bit Equality Comparator (TTL Input)                  | 5-43 |

| SECTION 6 ENHANCEMENT PROGRAMS                                               |      |

| NATIONAL'S A+ Program                                                        |      |

| NATIONAL'S B+ Program                                                        |      |

| NATIONAL'S Military 883/38510 Program                                        | 6-6  |

| SECTION 7 RELIABILITY REPORT                                                 |      |

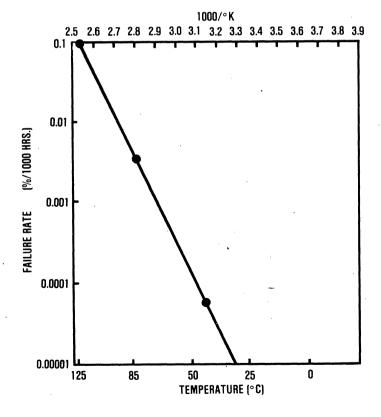

| Reliability of High Speed CMOS Logic PR-11                                   | 7-2  |

| SECTION 8 ORDERING AND PACKAGE INFORMATION                                   |      |

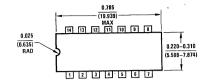

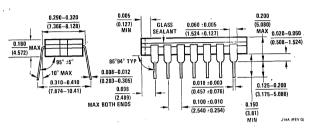

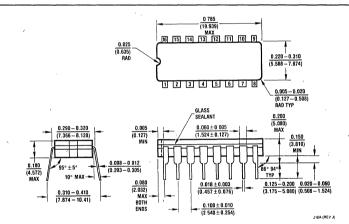

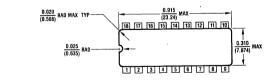

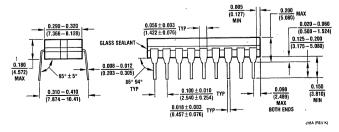

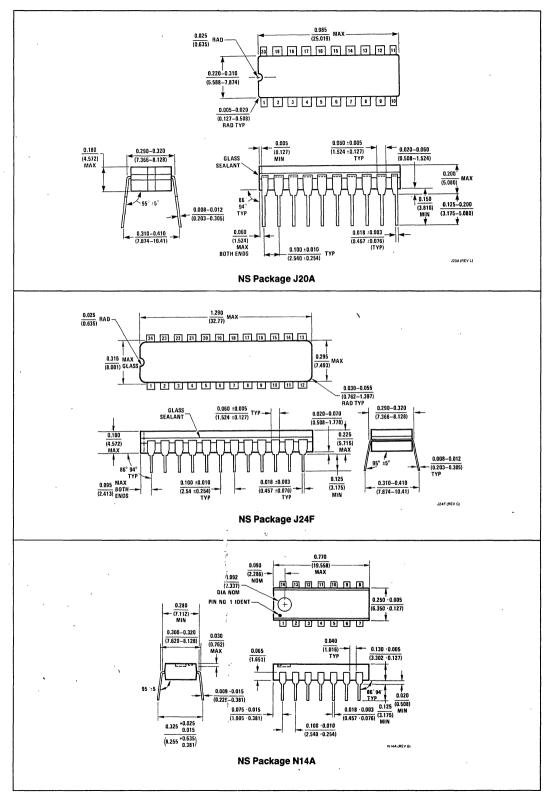

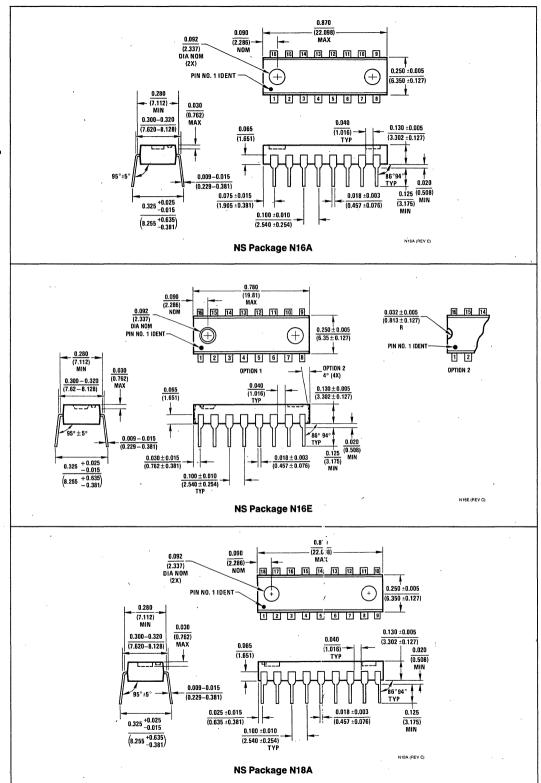

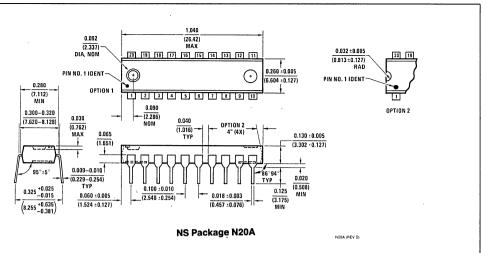

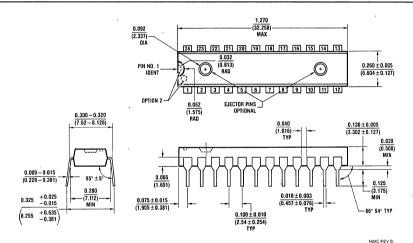

| Physical Dimensions                                                          | 8-2  |

## **High Speed CMOS Product Guide**

### NAND/NOR/Inverting Gates

| MM54HC00/MM74HC00 Quad 2-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MM54HCT00/MM74HCT00 Quad 2-Input NAND Gate (TTL Input)5-2                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MM54HC02/MM74HC02 Quad 2-Input NOR Gate4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MM54HC03/MM74HC03 Quad 2-Input Open Drain NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MM54HC04/MM74HC04 Hex Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MM54HCT04/MM74HCT04 Hex Inverter (TTL Input)5-5                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MM54HCU04/MM74HCU04 Hex Unbuffered Inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MM54HCT05/MM74HCT05 Hex Inverter with Open Drain Outputs (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MM54HC10/MM74HC10 Triple 3-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MM54HC14/MM74HC14 Hex Schmitt Trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MM54HC20/MM74HC20 Dual 4-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MM54HC27/MM74HC27 Triple 3-Input NOR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MM54HC30/MM74HC30 8-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MM54HC133 /MM74HC133 13-Input NAND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AND/OR Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MM54HC08/MM74HC08 Quad 2-Input AND Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HC11/MM74HC11 Triple 3-Input AND Gate4-23                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MM54HC32/MM54HC32 Quad 2-Input OR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM54HCT34/MM74HCT34 Hex Non-Inverting Gate (TTL Input)5-10                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MM54HC4002/MM74HC4002 Dual 4-Input NOR Gate4-340                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MM54HC4075/MM74HC4075 Triple 3-Input OR Gate4-376                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MM54HC4078/MM74HC4078 8-Input OR/NOR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AND-OR Gates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MM54HC58/MM74HC58 Dual AND-OR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MM54HC58/MM74HC58 Dual AND-OR Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Logic Level Converters                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters         MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter       4-358         MM54HC4050/MM74HC4050 Hex Logic Level Down Converter       4-358                                                                                                                                                                                                                                                                                                                  |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters         MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter       4-358         MM54HC4050/MM74HC4050 Hex Logic Level Down Converter       4-358                                                                                                                                                                                                                                                                                                                  |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters           MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter         4-358           MM54HC4050/MM74HC4050 Hex Logic Level Down Converter         4-358           XOR/XNOR Gates         4-65           MM54HC86/MM74HC86 Quad Exclusive OR Gate         4-65           MM54HC266/MM74HC266 Quad 2-Input Exclusive NOR Gate         4-221                                                                                                                        |

| Logic Level Converters         MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter       4-358         MM54HC4050/MM74HC4050 Hex Logic Level Down Converter       4-358         XOR/XNOR Gates         MM54HC86/MM74HC86 Quad Exclusive OR Gate       4-65         MM54HC266/MM74HC266 Quad 2-Input Exclusive NOR Gate       4-221         Schmitt Triggers         MM54HC14/MM74HC14 Hex Schmitt Trigger       4-26         MM54HC132/MM74HC132 Quad 2-Input Schmitt Trigger       4-91 |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| Logic Level Converters  MM54HC4049/MM74HC4049 Hex Inverting Logic Level Down Converter                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM54HCT240/MM74HCT240 Inverting Octal Tri-State Buffer (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MM54HC241/MM74HC241 Octal Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MM54HCT241/MM74HCT241 Octal Tri-State Buffer (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

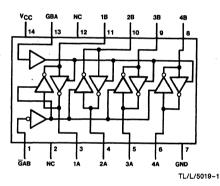

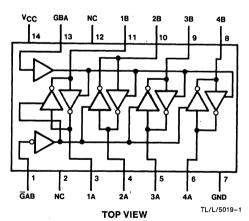

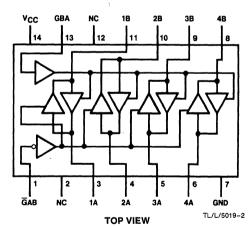

| MM54HC242/MM74HC242 Inverting Quad Tri-State Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HC243/MM74HC243 Quad Tri-State Transceivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MM54HC244/MM74HC244 Octal Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MM54HCT244/MM74HCT244 Octal Tri-State Buffer (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM54HC245/MM74HC245 Octal Bidirectional Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MM54HCT245/MM74HCT245 Octal Bidirectional Transceiver (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MM54HC365/MM54HC365 Hex Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM54HC366/MM54HC366 Inverting Hex Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MM54HC367/MM54HC367 Hex Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| MM54HC368/MM54HC368 Inverting Hex Tri-State Buffer4-256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MM54HC540/MM74HC540 Inverting Octal Tri-State Buffer4-285                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HC541/MM74HC541 Octal Tri-State Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MM54HC640/MM74HC640 Inverting Octal Tri-State Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HCT640/MM74HCT640 Inverting Octal Tri-State Transceiver (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MM54HC643/MM74HC643 True/Inverting Octal Tri-State Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MM54HCT643/MM74HCT643 True/Inverting Octal Tri-State Transceiver (TTL Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MM54HC646/MM74HC646 Octal Tri-State Bus Transceiver/Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HC648 /MM74HC648 Inverting Octal Tri-State Bus Transceiver/Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Analog Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MM54HC4016/MM74HC4016       Quad Bilateral Analog Switch       4-343         MM54HC4051/MM74HC4051       8 Channel Analog Multiplexer       4-361                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MINISTRICTUS IT MINIT 4 HO4051 6 Charinel Arialog Multiplexer4-301                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| MM54HC4052/MM74HC4052 Dual 4 Channel Analog Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MM54HC4052/MM74HC4052         Dual 4 Channel Analog Multiplexer         .4-361           MM54HC4053/MM74HC4053         Triple 2 Channel Analog Multiplexer         .4-361                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MM54HC4052/MM74HC4052       Dual 4 Channel Analog Multiplexer       .4-361         MM54HC4053/MM74HC4053       Triple 2 Channel Analog Multiplexer       .4-361         MM54HC4066/MM74HC4066       Quad Bilateral Analog Switch       .4-371                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| MM54HC4052/MM74HC4052       Dual 4 Channel Analog Multiplexer       4-361         MM54HC4053/MM74HC4053       Triple 2 Channel Analog Multiplexer       .4-361         MM54HC4066/MM74HC4066       Quad Bilateral Analog Switch       .4-371         MM54HC4316/MM74HC4316       Quad Bilateral Analog Switch       .4-382                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| MM54HC4052/MM74HC4052       Dual 4 Channel Analog Multiplexer       4-361         MM54HC4053/MM74HC4053       Triple 2 Channel Analog Multiplexer       .4-361         MM54HC4066/MM74HC4066       Quad Bilateral Analog Switch       .4-371         MM54HC4316/MM74HC4316       Quad Bilateral Analog Switch       .4-382         MM54HC4351/MM74HC4351       8 Channel Analog Multiplexer with Latches       .4-387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MM54HC4052/MM74HC4052       Dual 4 Channel Analog Multiplexer       .4-361         MM54HC4053/MM74HC4053       Triple 2 Channel Analog Multiplexer       .4-361         MM54HC4066/MM74HC4066       Quad Bilateral Analog Switch       .4-371         MM54HC4316/MM74HC4316       Quad Bilateral Analog Switch       .4-382         MM54HC4351/MM74HC4351       8 Channel Analog Multiplexer with Latches       .4-387         MM54HC4352/MM74HC4352       Dual 4 Channel Analog Multiplexer with Latches       .4-387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

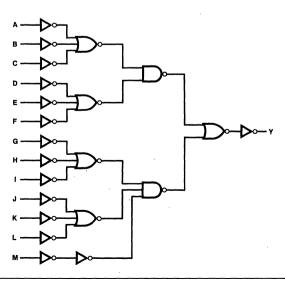

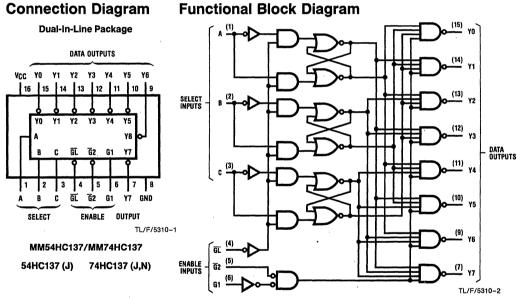

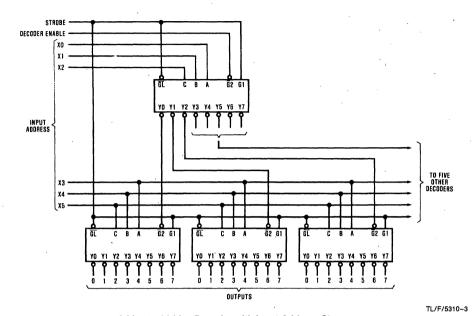

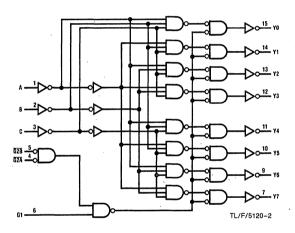

| MM54HC4052/MM74HC4052       Dual 4 Channel Analog Multiplexer       4-361         MM54HC4053/MM74HC4053       Triple 2 Channel Analog Multiplexer       .4-361         MM54HC4066/MM74HC4066       Quad Bilateral Analog Switch       .4-371         MM54HC4316/MM74HC4316       Quad Bilateral Analog Switch       .4-382         MM54HC4351/MM74HC4351       8 Channel Analog Multiplexer with Latches       .4-387                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |