# **High-Speed CMOS Data**

| <b>Alphanumeric</b> | 1 |

|---------------------|---|

| Index               |   |

| <b>Function</b> | 2 |

|-----------------|---|

| Selector Guide  |   |

- Definitions and Glossary of Terms

- Design Considerations

- Data Sheets

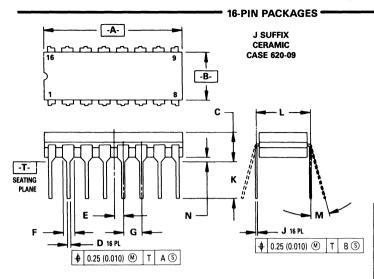

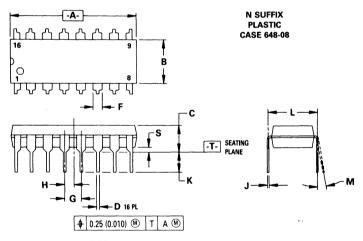

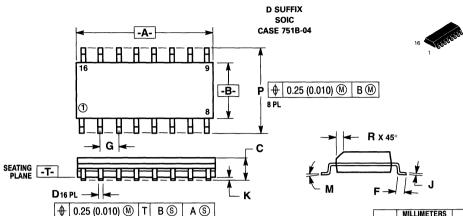

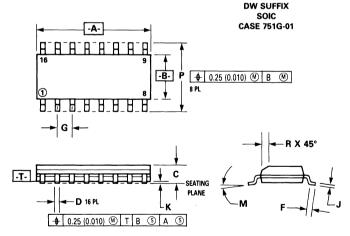

- Package Dimensions

#### DATA CLASSIFICATION

#### **Product Preview**

This heading on a data sheet indicates that the device is in the formative stages or in design (under development). The disclaimer at the bottom of the first page reads: "This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice."

#### Advance Information

This heading on a data sheet indicates that the device is in sampling, preproduction, or first production stages. The disclaimer at the bottom of the first page reads: "This document contains information on a new product. Specifications and information herein are subject to change without notice."

#### Fully Released

A fully released data sheet contains neither a classification heading nor a disclaimer at the bottom of the first page. This document contains information on a product in full production. Guaranteed limits will not be changed without written notice to your local Motorola Semiconductor Sales Office.

### **MOTOROLA**

### HIGH-SPEED CMOS LOGIC DATA

This book presents technical data for the broad line of High-Speed Logic integrated circuits. Complete specifications are provided in the form of data sheets. In addition, a comprehensive Function Selector Guide and a Design Considerations chapter have been included to familiarize the user with these logic circuits.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation counsequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended. or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries. affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

> Series D ©Motorola, Inc. 1993 Previous Edition ©Q2/1989 "All Rights Reserved"

Printed in U.S.A.

## WHAT'S NEW! DATA SHEETS

| Data Sheets Added |                |               | Sheets<br>eleted |

|-------------------|----------------|---------------|------------------|

| MC54/74HCT00A     | MC54/74HCT245A | MC54/74HC03   | MC54/74HC374     |

| MC54/74HC03A      | MC54/74HC273A  | MC54/74HC04   | MC54/74HC386     |

| MC54/74HCT08A     | MC54/74HCT273A | MC54/74HC76   | MC54/74HC533     |

| MC54/74HCT14A     | MC54/74HC373A  | MC54/74HC113  | MC54/74HCT533    |

| MC54/74HCT32A     | MC54/74HC374A  | MC54/74HC158  | MC54/74HC534     |

| MC54/74HCT74A     | MC54/74HC534A  | MC54/74HC161  | MC54/74HCT534    |

| MC54/74HCT138A    | MC54/74HC573A  | MC54/74HC163  | MC54/74HCT540    |

| MC54/74HCT157A    | MC54/74HCT573A | MC54/74HC174  | MC54/74HC573     |

| MC54/74HC161A     | MC54/74HC574A  | MC54/74HC242  | MC54/74HC574     |

| MC54/74HC163A     | MC54/74HCT574A | MC54/74HCT245 | MC54/74HCT640    |

| MC54/74HC174A     | MC54/74HC4046A | MC54/74HC273  | MC54/74HC648     |

| MC54/74HCT174A    | MC54/74HC4538A | MC54/74HC354  | MC54/74HC4352    |

|                   |                | MC54/74HC373  | MC54/74HC4538    |

The old "Non-A" process was a 5 micron process that was modified to run a 3.5 micron family. The new "A" process is a true 3 micron process and gives better process control, with improved performance and quality.

9-Wide and Nine-Wide are trademarks of Motorola Inc.

**<sup>&</sup>quot;A" Versus "Non-A"** — Motorola has an on-going device performance enhancement program for the High-Speed CMOS family. This is indicated by the "A" suffix of the device identification. Some of the characteristics of this "A" enhancement program are improved design, a better quality process, faster performing AC propagation delays and enhancements to various dc characteristics.

# Alphanumeric Index

#### **ALPHANUMERIC INDEX**

|   | , |   |

|---|---|---|

| Ц |   | ı |

|   |   | П |

|   |   | п |

|   |   |   |

| Device Number |                                                                     | Page    |

|---------------|---------------------------------------------------------------------|---------|

| MC54/MC74     | Function                                                            | Number  |

| HC00A         | Quad 2-Input NAND Gate                                              | . 5-2   |

| HCT00A        | Quad 2-Input NAND Gate with LSTTL-Compatible Inputs                 | . 5-5   |

| HC02A         | Quad 2-Input NOR Gate                                               | . 5-8   |

| HC03A         | Quad 2-Input NAND Gate with Open-Drain Outputs                      | . 5-11  |

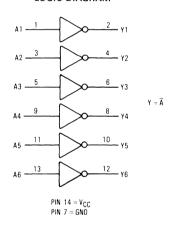

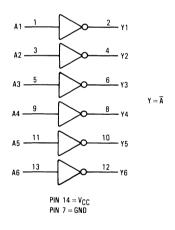

| HC04A         | Hex Inverter                                                        | . 5-15  |

| HCT04A        | Hex Inverter with LSTTL-Compatible Inputs                           |         |

| HCU04         | Hex Unbuffered Inverter                                             | . 5-21  |

| HC08A         | Quad 2-Input AND Gate                                               | . 5-25  |

| HCT08A        | Quad 2-Input AND Gate with LSTTL-Compatible Inputs                  | . 5-28  |

| HC10          | Triple 3-Input NAND Gate                                            | . 5-31  |

| HC11          | Triple 3-Input AND Gate                                             | . 5-34  |

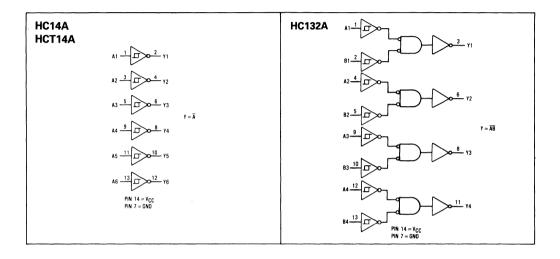

| HC14A         | Hex Schmitt-Trigger Inverter                                        | . 5-37  |

| HCT14A        | Hex Schmitt-Trigger Inverter with LSTTL-Compatible Inputs           | . 5-41  |

| HC20          | Dual 4-Input NAND Gate                                              | . 5-44  |

| HC27          | Triple 3-Input NOR Gate                                             |         |

| HC30          | 8-Input NAND Gate                                                   | . 5-50  |

| HC32A         | Quad 2-Input OR Gate                                                |         |

| HCT32A        | Quad 2-Input OR Gate with LSTTL-Compatible Inputs                   | . 5-56  |

| HC42          | 1-of-10 Decoder                                                     |         |

| HC51          | 2-Wide, 2-Input/2-Wide, 3-Input AND-NOR Gates                       | . 5-63  |

| HC58          | 2-Wide, 2-Input/2-Wide, 3-Input AND-OR Gates                        | . 5-66  |

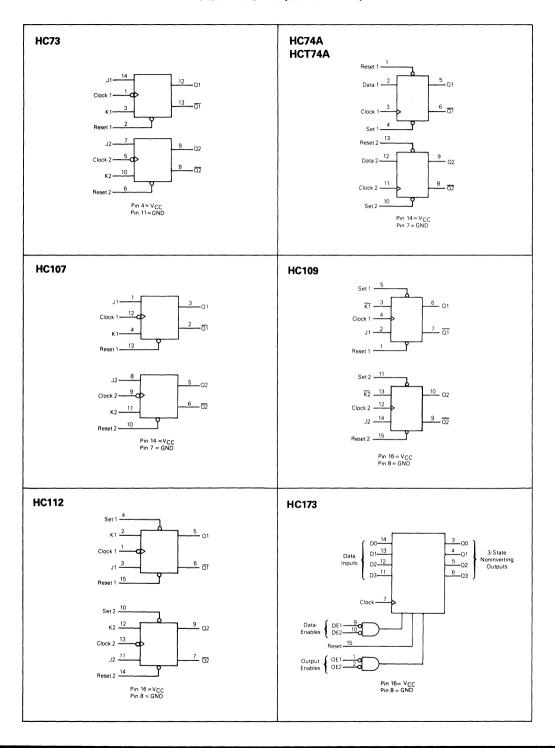

| HC73          | Dual J-K Flip-Flop with Reset                                       | . 5-69  |

| HC74A         | Dual D Flip-Flop with Set and Reset                                 |         |

| HCT74A        | Dual D Flip-Flop with Set and Reset with LSTTL-Compatible Inputs    | . 5-77  |

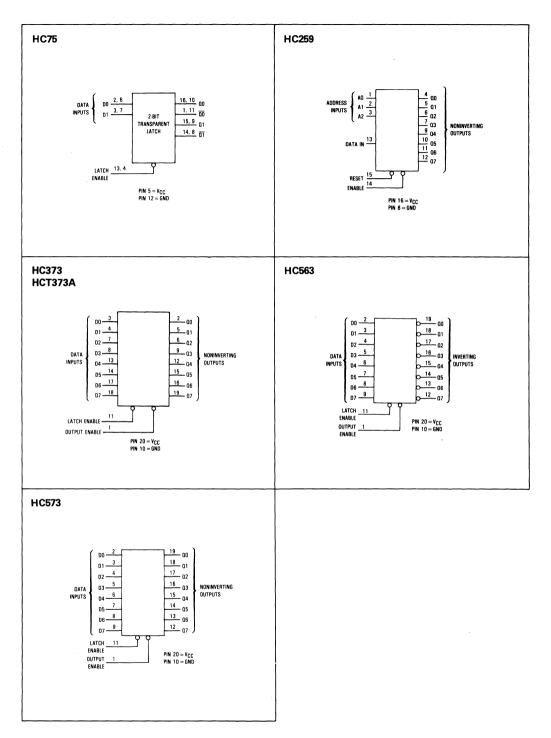

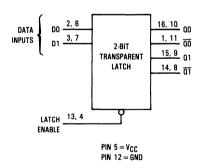

| HC75          | Dual 2-Bit Transparent Latch                                        | . 5-81  |

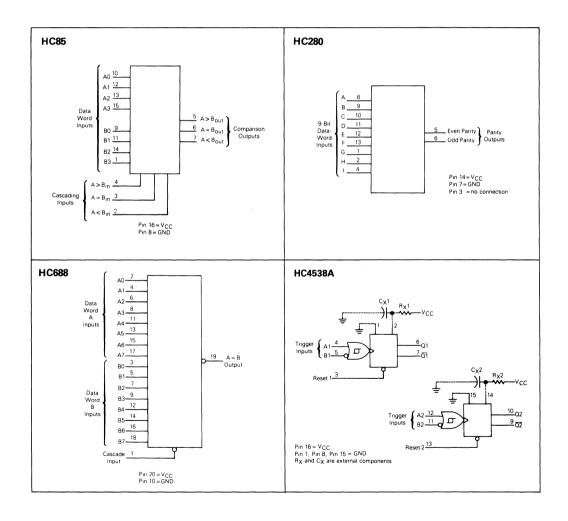

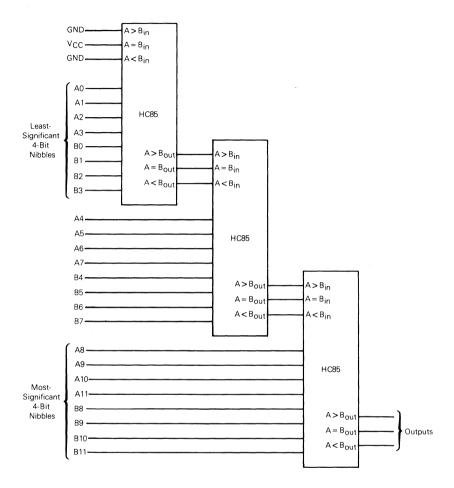

| HC85          | 4-Bit Magnitude Comparator                                          | . 5-85  |

| HC86          | Quad 2-Input Exclusive OR Gate                                      |         |

| HC107         | Dual J-K Flip-Flop with Reset                                       | . 5-94  |

| HC109         | Dual J-K Flip-Flop with Set and Reset                               |         |

| HC112         | Dual J-K Flip-Flop with Set and Reset                               | . 5-102 |

| HC125A        | Quad 3-State Noninverting Buffer                                    |         |

| HC126A        | Quad 3-State Noninverting Buffer                                    |         |

| HC132A        | Quad 2-Input NAND Gate with Schmitt-Trigger Inputs                  |         |

| HC133         | 13-Input NAND Gate                                                  |         |

| HC137         | 1-of-8 Decoder/Demultiplexer with Address Latch                     |         |

| HC138A        | 1-of-8 Decoder/Demultiplexer                                        | . 5-122 |

| HCT138A       | 1-of-8 Decoder/Demultiplexer with LSTTL-Compatible Inputs           |         |

| HC139A        | Dual 1-of-4 Decoder/Demultiplexer                                   |         |

| HC147         | Decimal-to-BCD Encoder                                              |         |

| HC151         | 8-Input Data Selector/Multiplexer                                   |         |

| HC153         | Dual 4-Input Data Selector/Multiplexer                              |         |

| HC154         | 1-of-16 Decoder/Demultiplexer                                       |         |

| HC157A        | Quad 2-Input Data Selector/Multiplexer                              |         |

| HCT157A       | Quad 2-Input Data Selector/Multiplexer with LSTTL-Compatible Inputs |         |

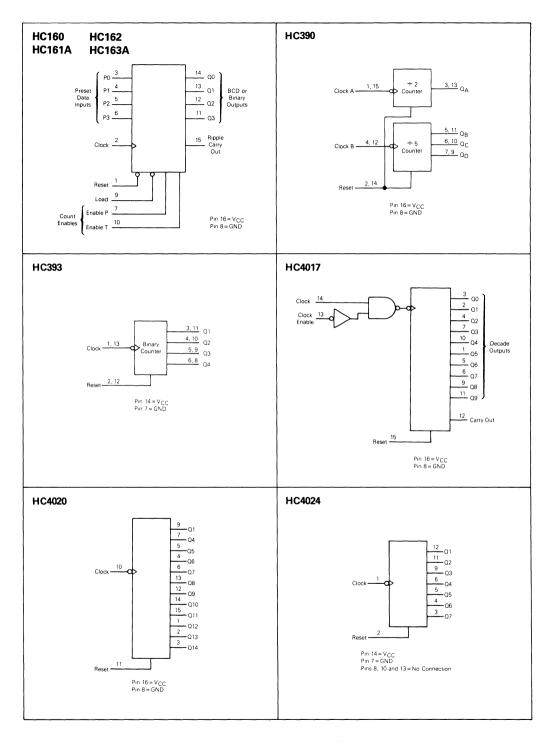

| HC160         | Presettable BCD Counter with Asynchronous Reset                     |         |

| HC161A        | Presettable 4-Bit Binary Counter with Asynchronous Reset            | . 5-171 |

#### **ALPHANUMERIC INDEX**

| <b>Device Number</b> |                                                                                                                  | Page  |

|----------------------|------------------------------------------------------------------------------------------------------------------|-------|

| MC54/MC74            | Function                                                                                                         | Numbe |

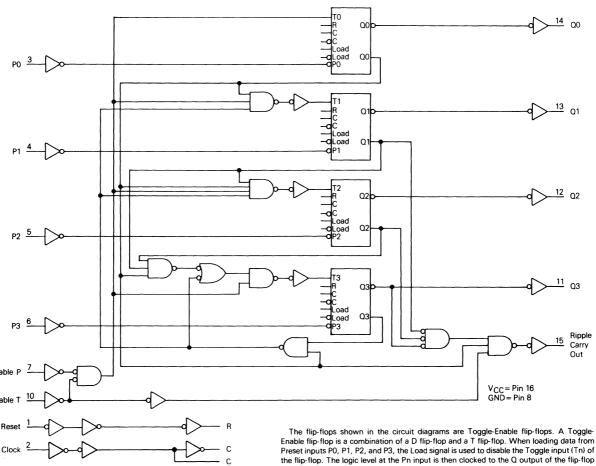

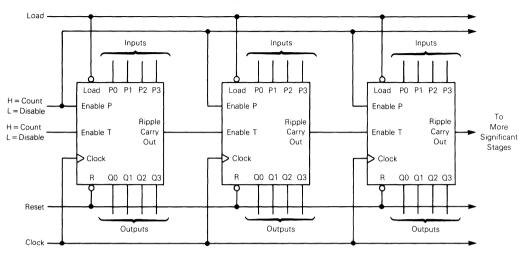

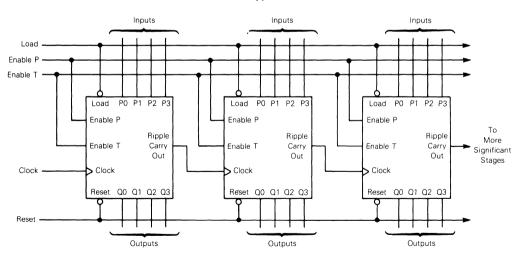

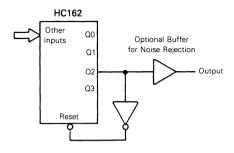

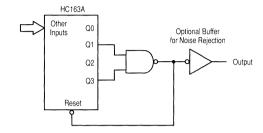

| HC162                | Presettable BCD Counter with Synchronous Reset                                                                   | 5-160 |

| HC163A               | Presettable 4-Bit Binary Counter with Synchronous Reset                                                          | 5-171 |

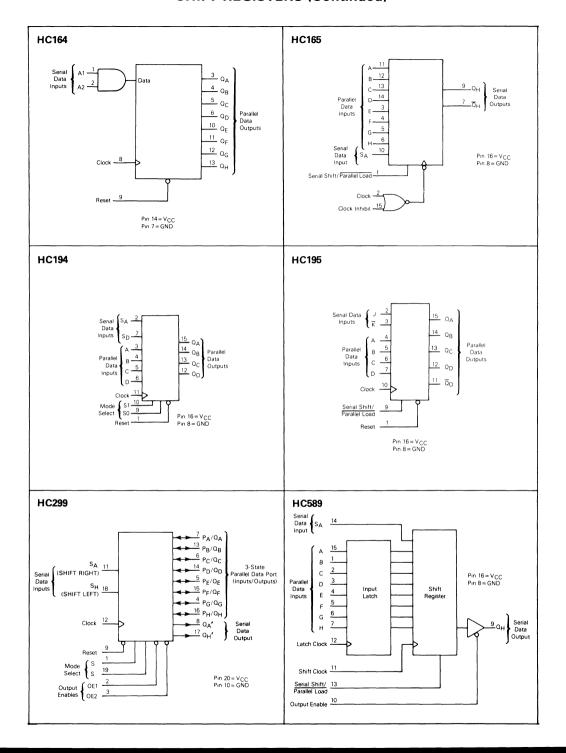

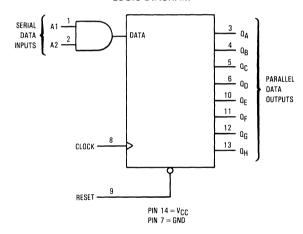

| HC164                | 8-Bit Serial-Input/Parallel-Output Shift Register                                                                | 5-182 |

| HC165                | 8-Bit Serial- or Parallel-Input/Serial-Output Shift Register                                                     | 5-187 |

| HC173                | Quad 3-State D Flip-Flop with Common Clock and Reset                                                             |       |

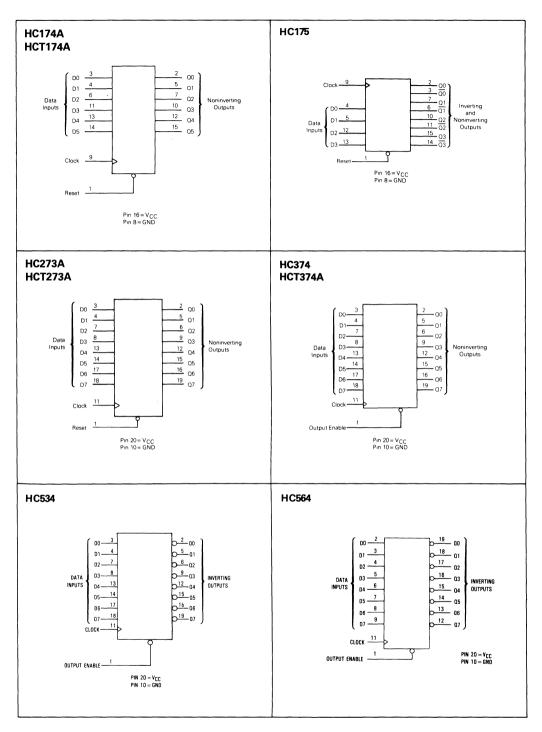

| HC174A               | Hex D Flip-Flop with Common Clock and Reset                                                                      | 5-198 |

| HCT174A              | Hex D Flip-Flop with Common Clock and Reset                                                                      | 5-202 |

| HC175                | Quad D Flip-Flop with Common Clock and Reset                                                                     | 5-206 |

| HC194                | 4-Bit Bidirectional Universal Shift Register                                                                     | 5-211 |

| HC195                | 4-Bit Universal Shift Register                                                                                   | 5-217 |

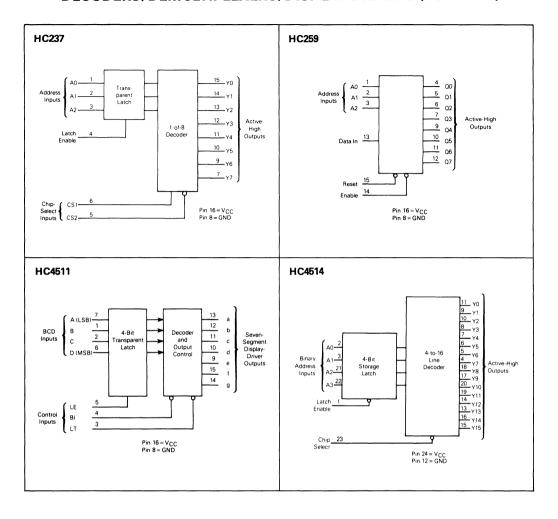

| HC237                | 1-of-8 Decoder/Demultiplexer with Address Latch                                                                  |       |

| HC240A               | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                                         |       |

| HCT240A              | Octal 3-State Inverting Buffer/Line Driver/Line Receiver with                                                    |       |

|                      | LSTTL-Compatible Inputs                                                                                          | 5-232 |

| HC241A               | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver                                                      |       |

| HCT241A              | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver with                                                 |       |

|                      | LSTTL-Compatible Inputs                                                                                          | 5-240 |

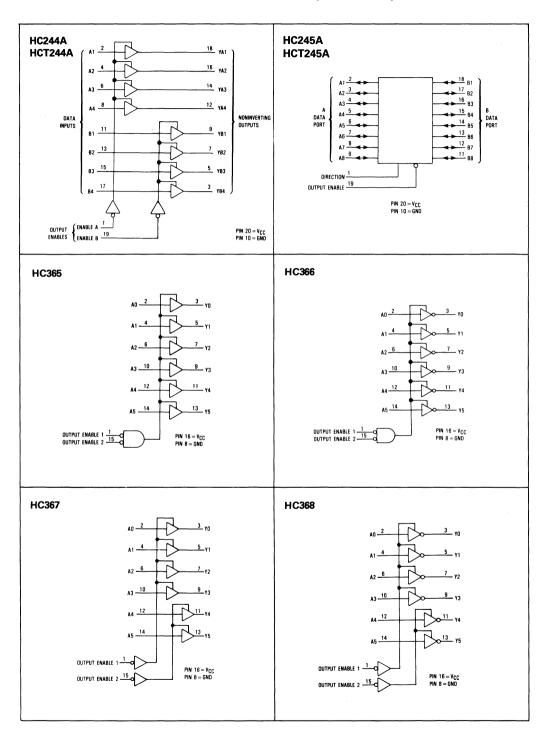

| HC244A               | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver                                                      |       |

| HCT244A              | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver with                                                 | 0 2   |

| 11012-1-17           | LSTTL-Compatible Inputs                                                                                          | 5-248 |

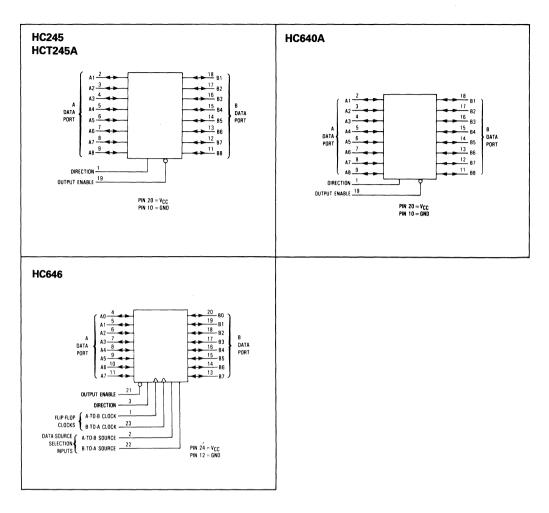

| HC245A               | Octal 3-State Noninverting Bus Transceiver                                                                       |       |

| HCT245A              | Octal 3-State Noninverting Bus Transceiver with LSTTL-Compatible                                                 | 0 202 |

| 1101240/             | Inputs                                                                                                           | 5-256 |

| HC251                | 8-Input Data Selector/Multiplexer with 3-State Outputs                                                           |       |

| HC253                | Dual 4-Input Data Selector/Multiplexer with 3-State Outputs                                                      |       |

| HC257                | Quad 2-Input Data Selector/Multiplexer with 3-State Outputs                                                      |       |

| HC259                | 8-Bit Addressable Latch/1-of-8 Decoder                                                                           |       |

| HC273A               | Octal D Flip-Flop with Common Clock and Reset                                                                    |       |

| HCT273A              | Octal D Flip-Flop with Common Clock and Reset with LSTTL-Compatible                                              | 0 270 |

| 11012/04             | Inputs                                                                                                           | 5-283 |

| HC280                | 9-Bit Odd/Even Parity Generator/Checker                                                                          |       |

| HC299                | 8-Bit Bidirectional Universal Shift Register with Parallel I/O                                                   |       |

| HC365                | Hex 3-State Noninverting Buffer with Common Enables                                                              |       |

| HC366                | Hex 3-State Inverting Buffer with Common Enables                                                                 |       |

| HC367                | Hex 3-State Noninverting Buffer with Separate 2-Bit and 4-Bit Sections                                           |       |

| HC368                | ·                                                                                                                |       |

| HC373A               | Hex 3-State Inverting Buffer with Separate 2-Bit and 4-Bit Sections Octal 3-State Noninverting Transparent Latch |       |

| HCT373A              | Octal 3-State Noninverting Transparent Latch with LSTTL-Compatible                                               | 5-315 |

| HC13/3A              |                                                                                                                  | 5-319 |

| HC374A               | Inputs                                                                                                           |       |

|                      | Octal 3-State Noninverting D Flip-Flop                                                                           |       |

| HCT374A              | Octal 3-State Noninverting D Flip-Flop with LSTTL-Compatible Inputs                                              |       |

| HC390                | Dual 4-Stage Binary Ripple Counter with ÷2 and ÷5 Sections                                                       |       |

| HC393                | Dual 4-Stage Binary Ripple Counter                                                                               |       |

| HC534A               | Octal 3-State Inverting D Flip-Flop                                                                              |       |

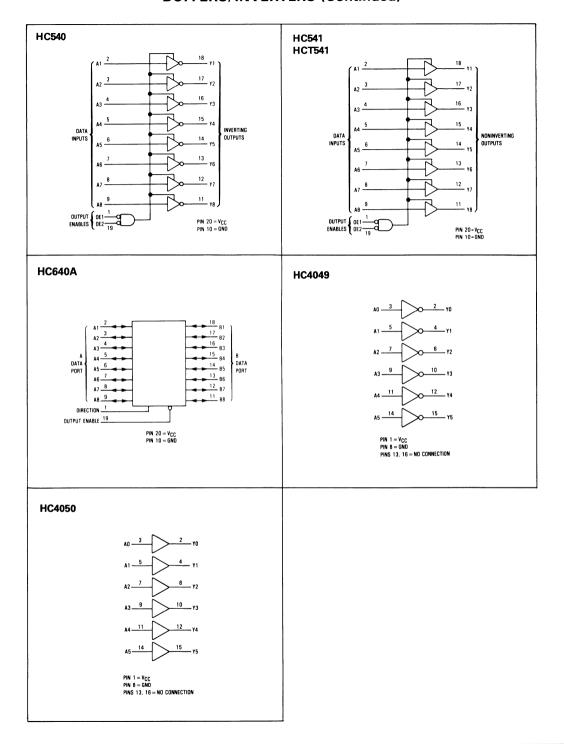

| HC540                | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                                         |       |

| HC541                | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver                                                      | 5-350 |

#### **ALPHANUMERIC INDEX**

|   | 7 |

|---|---|

| _ |   |

|   |   |

| • |   |

|   |   |

| Device Number<br>MC54/MC74 | Function                                                                                  | Page<br>Number |

|----------------------------|-------------------------------------------------------------------------------------------|----------------|

| HCT541                     | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver with                          |                |

|                            | LSTTL-Compatible Inputs                                                                   | . 5-354        |

| HC563                      | Octal 3-State Inverting Transparent Latch                                                 | . 5-358        |

| HC564                      | Octal 3-State Inverting D Flip-Flop                                                       | . 5-363        |

| HC573A                     | Octal 3-State Noninverting Transparent Latch                                              | . 5-368        |

| HCT573A                    | Octal 3-State Noninverting Transparent Latch with LSTTL-Compatible Inputs                 | . 5-372        |

| HC574A                     | Octal 3-State Noninverting D Flip-Flop                                                    | . 5-376        |

| HCT574A                    | Octal 3-State Noninverting D Flip-Flop with LSTTL-Compatible Inputs                       | . 5-380        |

| HC589                      | 8-Bit Serial- or Parallel-Input/Serial-Output Shift Register with 3-State Output          | . 5-384        |

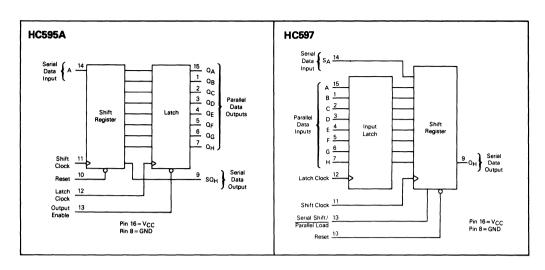

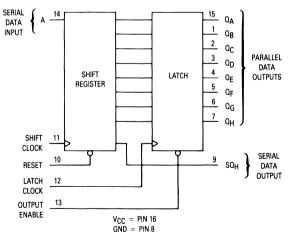

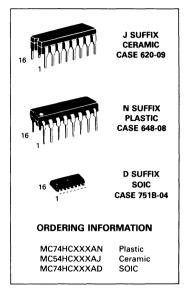

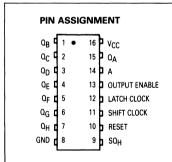

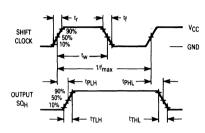

| HC595A                     | 8-Bit Serial-Input/Serial- or Parallel-Output Shift Register with Latched 3-State Outputs | . 5-392        |

| HC597                      | 8-Bit Serial- or Parallel-Input/Serial-Output Shift Register with Input Latch.            |                |

| HC640A                     | Octal 3-State Inverting Bus Transceiver                                                   |                |

| HC646                      | Octal 3-State Noninverting Bus Transceiver and D Flip-Flop                                |                |

| HC688                      | 8-Bit Equality Comparator                                                                 |                |

| HC4002                     | Dual 4-Input NOR Gate                                                                     |                |

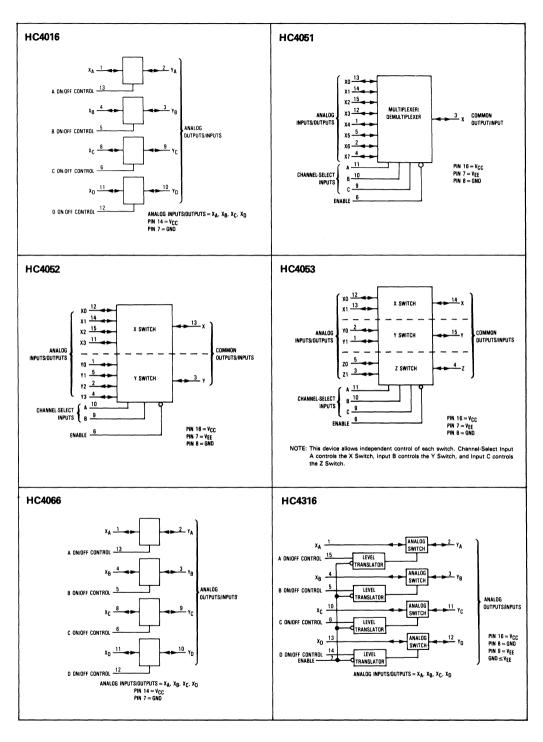

| HC4016                     | Quad Analog Switch/Multiplexer/Demultiplexer                                              |                |

| HC4017                     | Decade Counter                                                                            |                |

| HC4020                     | 14-Stage Binary Ripple Counter                                                            |                |

| HC4024                     | 7-Stage Binary Ripple Counter                                                             |                |

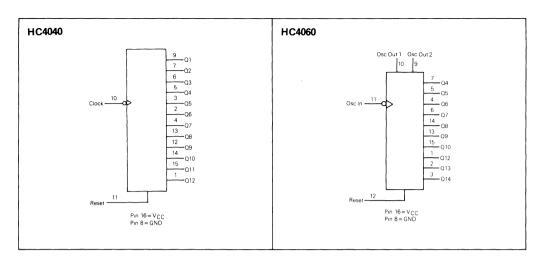

| HC4040                     | 12-Stage Binary Ripple Counter                                                            |                |

| HC4046A                    | Phase-Locked Loop                                                                         |                |

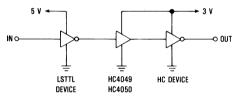

| HC4049                     | Hex Inverting Buffer/Logic-Level Down Converter                                           |                |

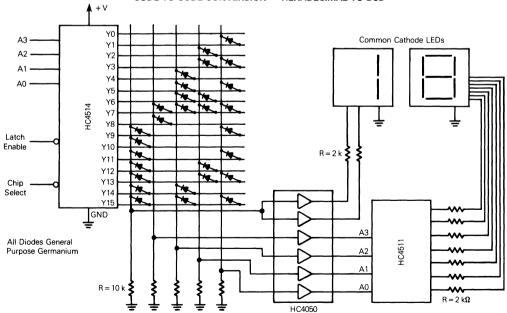

| HC4050                     | Hex Noninverting Buffer/Logic-Level Down Converter                                        |                |

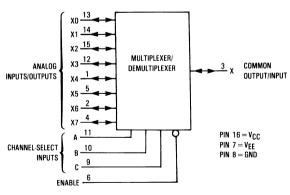

| HC4051                     | 8-Channel Analog Multiplexer/Demultiplexer                                                |                |

| HC4052                     | Dual 4-Channel Analog Multiplexer/Demultiplexer                                           |                |

| HC4053                     | Triple 2-Channel Analog Multiplexer/Demultiplexer                                         | . 5-476        |

| HC4060                     | 14-Stage Binary Ripple Counter with Oscillator                                            |                |

| HC4066                     | Quad Analog Switch/Multiplexer/Demultiplexer                                              |                |

| HC4075                     | Triple 3-Input OR Gate                                                                    |                |

| HC4078                     | 8-Input NOR/OR Gate                                                                       | . 5-508        |

| HC4316                     | Quad Analog Switch/Multiplexer/Demultiplexer with Separate Analog                         |                |

|                            | and Digital Power Supplies                                                                | . 5-512        |

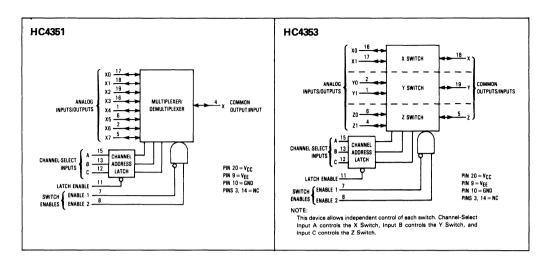

| HC4351                     | 8-Channel Analog Multiplexer/Demultiplexer with Address Latch                             | . 5-521        |

| HC4353                     | Triple 2-Channel Analog Multiplexer/Demultiplexer with Address Latch                      | . 5-521        |

| HC4511                     | BCD-to-Seven-Segment Latch/Decoder/Display Driver                                         |                |

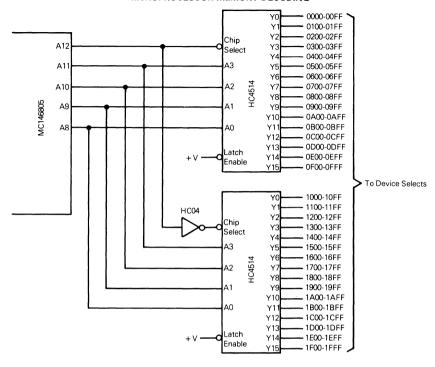

| HC4514                     | 1-of-16 Decoder/Demultiplexer with Address Latch                                          | . 5-539        |

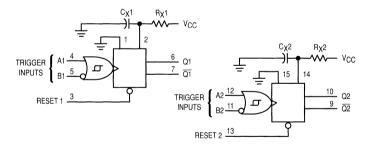

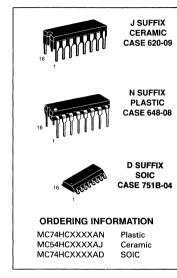

| HC4538A                    | Dual Precision Monostable Multivibrator (Retriggerable, Resettable)                       | . 5-546        |

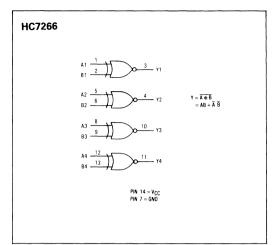

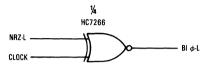

| HC7266                     | Quad 2-Input Exclusive NOR Gate                                                           | 5-557          |

## **Function Selector Guide**

| Subject P                             | age  |

|---------------------------------------|------|

| Buffers/Inverters 2                   | 2-2  |

| Gates 2                               | 2-8  |

| Schmitt Triggers 2                    | 2-14 |

| Bus Transceivers 2                    | 2-15 |

| Latches 2                             | 2-17 |

| Flip-Flops 2                          | 2-19 |

| Digital Data Selectors/Multiplexers 2 | 2-24 |

| Decoders/Demultiplexers/              |      |

| Display Drivers                       | 2-27 |

| Analog Switches/Multiplexers/         |      |

| Demultiplexers                        | 2-31 |

| Shift Registers 2                     | 2-35 |

| Counters 2                            | 2-38 |

| Miscellaneous Devices 2               | -41  |

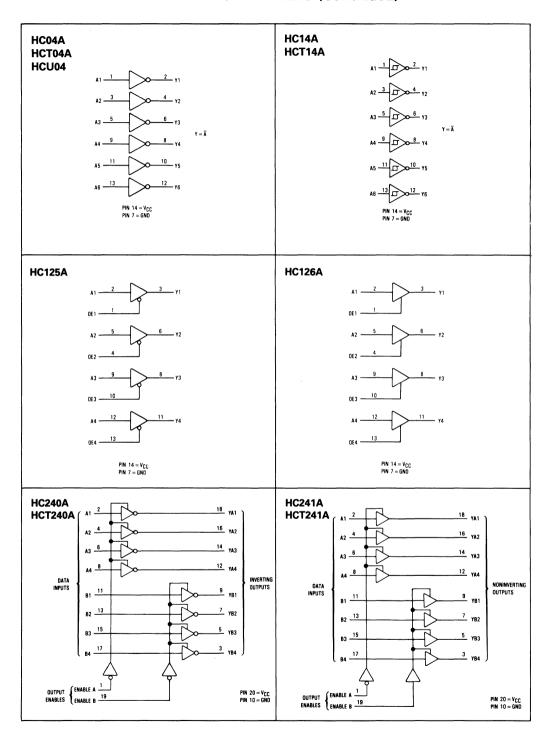

#### **BUFFERS/INVERTERS**

| Device<br>Number<br>MC54/MC74 | Function                                                                                    | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC04A                         | Hex Inverter                                                                                | LS04                                                 | *4069                                               | LS/CMOS                     | 14                   |

| HCT04A                        | Hex Inverter with LSTTL-Compatible Inputs                                                   | LS04                                                 | *4069                                               | LS/CMOS                     | 14                   |

| HCU04                         | Hex Unbuffered Inverter                                                                     | LS04                                                 | 4069                                                | LS/CMOS                     | 14                   |

| HC14A                         | Hex Schmitt-Trigger Inverter                                                                | LS14                                                 | 4584                                                | LS/CMOS                     | 14                   |

| HCT14A                        | Hex Schmitt-Trigger Inverter with LSTTL-Compatible<br>Inputs                                | LS14                                                 | 4584                                                | LS/CMOS                     | 14                   |

| HC125A                        | Quad 3-State Noninverting Buffer                                                            | LS125,LS125A                                         |                                                     | LS                          | 14                   |

| HC126A                        | Quad 3-State Noninverting Buffer                                                            | LS126,LS126A                                         |                                                     | LS                          | 14                   |

| HC240A                        | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                    | LS240                                                |                                                     | LS                          | 20                   |

| HCT240A                       | Octal 3-State Inverting Buffer/Line Driver/Line Receiver<br>with LSTTL-Compatible Inputs    | LS240                                                |                                                     | LS                          | 20                   |

| HC241A                        | Octal 3-State Noninverting Buffer/Line Driver/Line<br>Receiver                              | LS241                                                |                                                     | LS                          | 20                   |

| HCT241A                       | Octal 3-State Noninverting Buffer/Line Driver/Line<br>Receiver with LSTTL-Compatible Inputs | LS241                                                | 1                                                   | LS                          | 20                   |

| HC244A                        | Octal 3-State Noninverting Buffer/Line Driver/Line<br>Receiver                              | LS244                                                |                                                     | LS                          | 20                   |

| HCT244A                       | Octal 3-State Noninverting Buffer/Line Driver/Line<br>Receiver with LSTTL-Compatible Inputs | LS244                                                |                                                     | LS                          | 20                   |

| HC245A                        | Octal 3-State Noninverting Bus Transceiver                                                  | LS245                                                |                                                     | LS                          | 20                   |

| HCT245A                       | Octal 3-State Noninverting Bus Transceiver with LSTTL-Compatible Inputs                     | LS245                                                |                                                     | LS                          | 20                   |

| HC365                         | Hex 3-State Noninverting Buffer with Common Enables                                         | LS365,LS365A                                         |                                                     | LS                          | 16                   |

| HC366                         | Hex 3-State Inverting Buffer with Common Enables                                            | LS366,LS366A                                         |                                                     | LS                          | 16                   |

| HC367                         | Hex 3-State Noninverting Buffer with Separate 2-Bit and 4-Bit Sections                      | LS367,LS367A                                         | 4503                                                | LS/CMOS                     | 16                   |

| HC368                         | Hex 3-State Inverting Buffer with Separate 2-Bit and 4-Bit Sections                         | LS368,LS368A                                         |                                                     | LS                          | 16                   |

| HC540                         | Octal 3-State Inverting Buffer/Line Driver/Line Receiver                                    | LS540                                                |                                                     | LS                          | 20                   |

| HC541                         | Octal 3-State Noninverting Buffer/Line Driver/Line Receiver                                 | LS541                                                |                                                     | LS                          | 20                   |

| HCT541                        | Octal 3-State Noninverting Buffer/Line Driver/Line<br>Receiver with LSTTL-Compatible Inputs | LS541                                                |                                                     | LS                          | 20                   |

| HC640A                        | Octal 3-State Inverting Bus Transceiver                                                     | LS640                                                |                                                     | LS                          | 20                   |

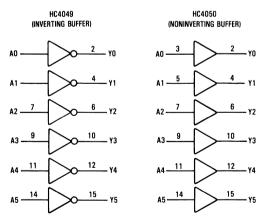

| HC4049                        | Hex Inverting Buffer/Logic-Level Down Converter                                             |                                                      | 4049                                                | CMOS                        | 16                   |

| HC4050                        | Hex Noninverting Buffer/Logic-Level Down Converter                                          |                                                      | 4050                                                | CMOS                        | 16                   |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                                                                                                                  | HC<br>HCT<br>04A | HCU<br>04 | HC<br>14A | HC<br>125A | HC<br>126A | HC<br>HCT<br>240A | HC<br>HCT<br>241A | HC<br>HCT<br>244A |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-----------|------------|------------|-------------------|-------------------|-------------------|

| # Pins                                                                                                                                                                  | 14               | 14        | 14        | 14         | 14         | 20                | 20                |                   |

| Quad Device<br>Hex Device<br>Octal Device<br>Nine-Wide Device                                                                                                           | •                | •         | •         | •          | •          | •                 | •                 | •                 |

| Noninverting Outputs Inverting Outputs                                                                                                                                  | •                | •         | •         | •          | •          | •                 | •                 | •                 |

| Single Stage (unbuffered)                                                                                                                                               |                  | •         |           |            |            |                   |                   |                   |

| Schmitt Trigger                                                                                                                                                         |                  |           | •         |            |            |                   |                   |                   |

| 3-State Outputs Open-Drain Outputs Common Output Enables Active-Low Output Enables Active-High Output Enables Separate 4-Bit Sections Separate 2-Bit and 4-Bit Sections |                  |           |           | •          | •          | •                 | •                 | •                 |

| Transceiver<br>Direction Control                                                                                                                                        |                  |           |           |            |            |                   |                   |                   |

| Logic-Level Down Converter                                                                                                                                              |                  |           |           |            |            |                   |                   |                   |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                                                                                | HC<br>HCT<br>245A | HC<br>365 | HC<br>366 | HC<br>367 | HC<br>368 | HC<br>540 | HC<br>HCT<br>541 | HC<br>640A |

|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------|-----------|-----------|-----------|-----------|------------------|------------|

| # Pins                                                                                                                                | 20                | 16        | 16        | 16        | 16        | 20        | 20               | 20         |

| Quad Device<br>Hex Device<br>Octal Device<br>Nine-Wide Device                                                                         | •                 | •         | •         | •         | •         | •         |                  |            |

| Noninverting Outputs Inverting Outputs                                                                                                | •                 | •         | •         | •         |           |           | •                |            |

| Single Stage (unbuffered)                                                                                                             |                   |           |           |           |           |           |                  |            |

| Schmitt Trigger                                                                                                                       |                   |           |           |           |           |           |                  |            |

| 3-State Outputs Open-Drain Outputs Common Output Enables Active-Low Output Enables Active-High Output Enables Separate 4-Bit Sections | :                 | •         | •         | •         | •         | :         | •                | •          |

| Separate 2-Bit and 4-Bit Sections                                                                                                     |                   |           |           | •         | •         |           |                  |            |

| Transceiver<br>Direction Control                                                                                                      | :                 |           |           |           |           |           |                  |            |

| Logic-Level Down Converter                                                                                                            |                   |           |           |           |           |           |                  |            |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                                                                                                                  | HC<br>4049 | HC<br>4050 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|

| # Pins                                                                                                                                                                  | 16         | 16         |

| Quad Device<br>Hex Device<br>Octal Device<br>Nine-Wide Device                                                                                                           | •          | •          |

| Noninverting Outputs Inverting Outputs                                                                                                                                  | •          | •          |

| Single Stage (unbuffered)                                                                                                                                               |            |            |

| Schmitt Trigger                                                                                                                                                         |            |            |

| 3-State Outputs Open-Drain Outputs Common Output Enables Active-Low Output Enables Active-High Output Enables Separate 4-Bit Sections Separate 2-Bit and 4-Bit Sections |            |            |

| Transceiver Direction Control                                                                                                                                           |            |            |

| Logic-Level Down Converter                                                                                                                                              | •          | •          |

| Device<br>Number<br>MC54/MC74 | Function                                            | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|-----------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

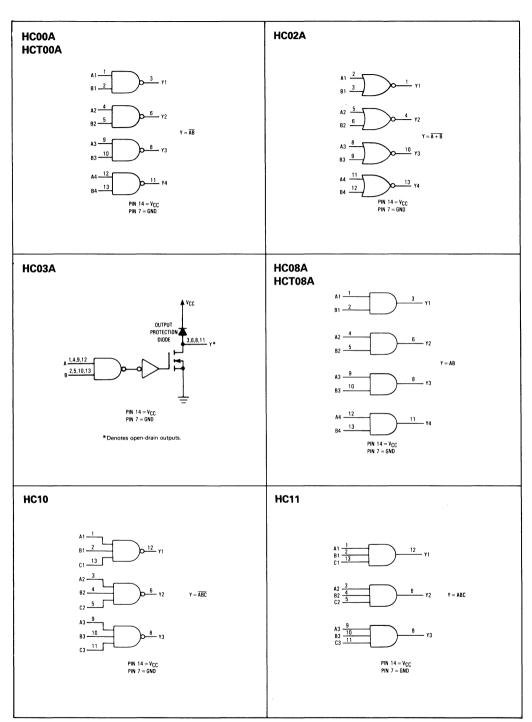

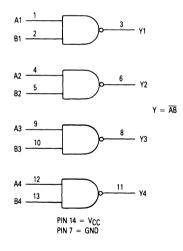

| HC00A                         | Quad 2-Input NAND Gate                              | LS00                                                 | 4011                                                | LS                          | 14                   |

| HCT00A                        | Quad 2-Input NAND Gate with LSTTL-Compatible Inputs | LS00                                                 | 4001                                                | LS                          | 14                   |

| HC02A                         | Quad 2-Input NOR Gate                               | LS02                                                 | 4001                                                | LS                          | 14                   |

| HC03A                         | Quad 2-Input NAND Gate with Open-Drain Outputs      | LS03                                                 | *4011                                               | LS                          | 14                   |

| HC08A                         | Quad 2-Input AND Gate                               | LS08                                                 | 4081                                                | LS                          | 14                   |

| HCT08A                        | Quad 2-Input AND Gate with LSTTL-Compatible Inputs  | LS08                                                 | 4081                                                | LS                          | 14                   |

| HC10                          | Triple 3-Input NAND Gate                            | LS10                                                 | 4023                                                | LS                          | 14                   |

| HC11                          | Triple 3-Input AND Gate                             | LS11                                                 | 4073                                                | LS                          | 14                   |

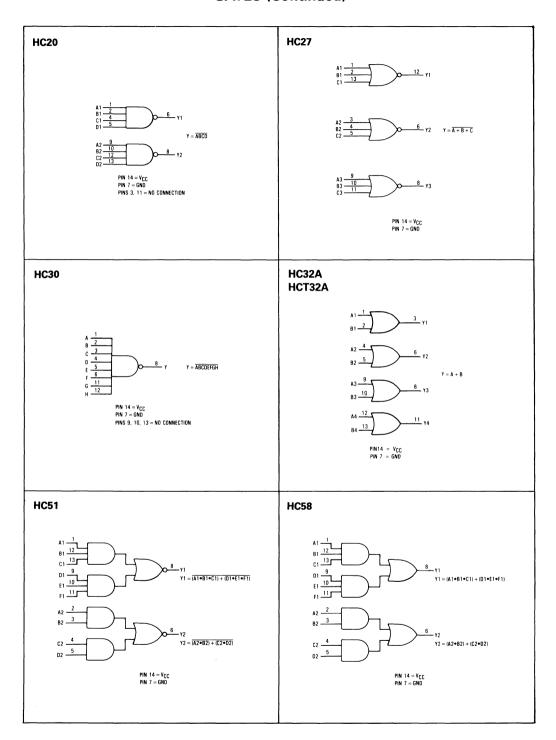

| HC20                          | Dual 4-Input NAND Gate                              | LS20                                                 | 4012                                                | LS                          | 14                   |

| HC27                          | Triple 3-Input NOR Gate                             | LS27                                                 | 4025                                                | LS                          | 14                   |

| HC30                          | 8-Input NAND Gate                                   | LS30                                                 | 4068                                                | LS                          | 14                   |

| HC32A                         | Quad 2-Input OR Gate                                | LS32                                                 | 4071                                                | LS                          | 14                   |

| HCT32A                        | Quad 2-Input OR Gate with LSTTL-Compatible Inputs   | LS32                                                 | 4071                                                | LS                          | 14                   |

| HC51                          | 2-Wide, 2-Input/2-Wide, 3-Input AND-NOR Gates       | LS51                                                 | *4506                                               | LS                          | 14                   |

| ★HC58                         | 2-Wide, 2-Input/2-Wide, 3-Input AND-OR Gates        |                                                      | *4506                                               |                             | 14                   |

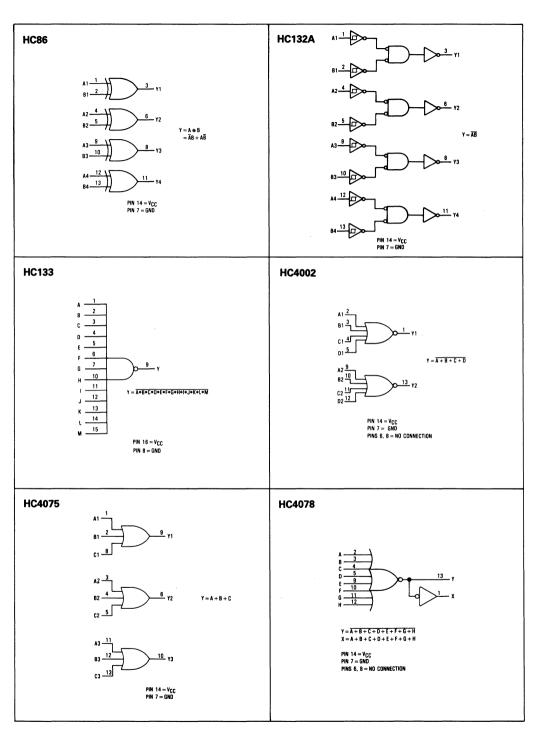

| HC86                          | Quad 2-Input Exclusive OR Gate                      | LS86                                                 | 4070                                                | LS                          | 14                   |

| HC132A                        | Quad 2-Input NAND Gate with Schmitt-Trigger Inputs  | LS132                                                | 4093                                                | LS                          | 14                   |

| HC133                         | 13-Input NAND Gate                                  | LS133                                                |                                                     | LS                          | 16                   |

| HC4002                        | Dual 4-Input NOR Gate                               | *LS25                                                | 4002                                                | CMOS                        | 14                   |

| HC4075                        | Triple 3-Input OR Gate                              |                                                      | 4075                                                | CMOS                        | 14                   |

| HC4078                        | 8-Input NOR/OR Gate                                 |                                                      | 4078                                                | CMOS                        | 14                   |

| ★HC7266                       | Quad 2-Input Exclusive NOR Gate                     | *LS266                                               | 4077                                                | LS/CMOS                     | 14                   |

<sup>★</sup>HC7266 | Quad 2-Input Exc

\*Suggested alternative

★Exclusive High-Speed CMOS design

#### **GATES** (Continued)

#### HC Devices Have CMOS-Compatible Inputs.

| Device                                               | HC<br>HCT<br>00A | HC<br>02A | HC<br>03A | HC<br>HCT<br>08A | HC<br>10 | HC<br>11 | HC<br>20 | HC<br>27 | HC<br>30 | HC<br>HCT<br>32A |

|------------------------------------------------------|------------------|-----------|-----------|------------------|----------|----------|----------|----------|----------|------------------|

| # Pins                                               | 14               | 14        | 14        | 14               | 14       | 14       | 14       | 14       | 14       | 14               |

| Single Device Dual Device Triple Device Quad Device  | •                | •         | •         | •                | •        | •        | •        | •        | •        | •                |

| NAND<br>NOR<br>AND<br>OR                             | •                | •         | •         | •                | •        | •        | •        | •        | •        | •                |

| Exclusive OR Exclusive NOR AND-NOR AND-OR            |                  |           |           |                  |          |          |          |          |          |                  |

| 2-Input<br>3-Input<br>4-Input<br>8-Input<br>13-Input | •                | •         | •         | •                | •        | •        | •        | •        | •        | •                |

| Schmitt-Trigger Inputs                               |                  |           |           |                  |          |          |          |          |          |                  |

| Open-Drain Outputs                                   |                  |           | •         |                  |          |          |          |          |          |                  |

#### HC Devices Have CMOS-Compatible Inputs.

| Device                                                       | HC<br>51 | HC<br>58 | HC<br>86 | HC<br>132A | HC<br>133 | HC<br>4002 | HC<br>4075 | HC<br>4078 | HC<br>7266 |

|--------------------------------------------------------------|----------|----------|----------|------------|-----------|------------|------------|------------|------------|

| # Pins                                                       | 14       | 14       | 14       | 14         | 16        | 14         | 14         | 14         | 14         |

| Single Device<br>Dual Device<br>Triple Device<br>Quad Device | •        | •        | •        | •          | •         | •          | •          | •          | •          |

| NAND<br>NOR<br>AND<br>OR                                     |          |          |          | •          | •         | •          | •          | •          |            |

| Exclusive OR<br>Exclusive NOR<br>AND-NOR<br>AND-OR           |          | •        | •        | 4          |           |            |            |            | •          |

| 2-Input<br>3-Input<br>4-Input<br>8-Input<br>13-Input         | :        | •        | •        | •          | •         | •          | •          | •          | •          |

| Schmitt-Trigger Inputs                                       |          |          |          | •          |           |            |            |            |            |

| Open-Drain Outputs                                           |          |          |          |            |           |            |            |            |            |

#### **GATES** (Continued)

#### **SCHMITT TRIGGERS**

| Device<br>Number<br>MC54/MC74 | Function                                                  | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|-----------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC14A                         | Hex Schmitt-Trigger Inverter                              | LS14                                                 | 4584                                                | LS/CMOS                     | 14                   |

| HCT14A                        | Hex Schmitt-Trigger Inverter with LSTTL-Compatible Inputs | LS14                                                 | 4584                                                | LS                          | 14                   |

| HC132A                        | Quad 2-Input NAND Gate with Schmitt-Trigger Inputs        | LS132                                                | 4093                                                | LS                          | 14                   |

#### **BUS TRANSCEIVERS**

| Device<br>Number<br>MC54/MC74 | Function                                                                   | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|----------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

| HC245A                        | Octal 3-State Noninverting Bus Transceiver                                 | LS245                                                |                                                     | LS                          | 20                   |

| HCT245A                       | Octal 3-State Noninverting Bus Transceiver with<br>LSTTL-Compatible Inputs | LS245                                                |                                                     | LS                          | 20                   |

| HC640A                        | Octal 3-State Inverting Bus Transceiver                                    | LS640                                                |                                                     | LS                          | 20                   |

| HC646                         | Octal 3-State Noninverting Bus Transceiver and<br>D Flip-Flop              | LS646                                                |                                                     | LS                          | 24                   |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                        | HC<br>HCT<br>245A | HC<br>HCT<br>640A | HC<br>646 |

|-------------------------------------------------------------------------------|-------------------|-------------------|-----------|

| # Pins                                                                        | 20                | 20                | 24        |

| Quad Device<br>Octal Device                                                   | •                 |                   |           |

| Buffer<br>Storage Capability                                                  | •                 | •                 | •         |

| Inverting Outputs Noninverting Outputs                                        | •                 | •                 |           |

| Common Output Enable<br>Active-Low Output Enable<br>Active-High Output Enable | •                 | •                 | •         |

| Direction Control                                                             | •                 | •                 | •         |

#### **LATCHES**

| Device<br>Number<br>MC54/MC74 | Function                                                                                                               | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional<br>Equivalent<br>CMOS<br>Device<br>MC1XXXX<br>or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|----------------------|

| HC75                          | Dual 2-Bit Transparent Latch                                                                                           | LS75                                                 |                                                                    | LS                          | 16                   |

| HC259                         | 8-Bit Addressable Latch/1-of-8 Decoder                                                                                 | LS259                                                |                                                                    | LS                          | 16                   |

| HC373A                        | Octal 3-State Noninverting Transparent Latch                                                                           | LS373,LS573                                          |                                                                    | LS373                       | 20                   |

| HCT373A                       | Octal 3-State Noninverting Transparent Latch with<br>LSTTL-Compatible Inputs                                           | LS373,LS573                                          |                                                                    | LS373                       | 20                   |

| HC563                         | Octal 3-State Inverting Transparent Latch                                                                              | LS533,LS563                                          |                                                                    | LS563                       | 20                   |

| HC573A<br>HCT573A             | Octal 3-State Noninverting Transparent Latch Octal 3-State Noninverting Transparent Latch with LSTTL-Compatible Inputs | LS373,LS573<br>LS373,LS573                           |                                                                    | LS573<br>LS573              | 20<br>20             |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                               | HC<br>75 | HC<br>259 | HC<br>HCT<br>373A | HC<br>563 | HC<br>HCT<br>573A |

|------------------------------------------------------|----------|-----------|-------------------|-----------|-------------------|

| # Pins                                               | 16       | 16        | 20                | 20        | 20                |

| Single Device<br>Dual Device<br>Octal Device         | •        | •         |                   | •         |                   |

| Number of Bits Controlled by Latch Enable:<br>2<br>8 | •        |           |                   | •         |                   |

| Transparent<br>Addressable<br>Readback Capability    | •        | •         | •                 | •         | •                 |

| Noninverting Outputs<br>Inverting Outputs            | :        | •         | •                 | •         | •                 |

| Common Latch Enable, Active-Low                      |          |           | •                 | •         | •                 |

| 3-State Outputs<br>Common Output Enable, Active-Low  |          |           | :                 | •         | :                 |

These devices are identical in function and are different in pinout only: HC/HCT373A and HC/HCT573A

#### **FLIP-FLOPS**

| Device<br>Number<br>MC54/MC74 | Function                                                                      | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional<br>Equivalent<br>CMOS<br>Device<br>MC1XXXX<br>or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------|-----------------------------|----------------------|

| HC73                          | Dual J-K Flip-Flop with Reset                                                 | LS73,LS73A,<br>LS107,LS107A                          | *4027                                                              | LS73,<br>LS73A              | 14                   |

| HC74A                         | Dual D Flip-Flop with Set and Reset                                           | LS74,LS74A                                           | *4013                                                              | LS                          | 14                   |

| HCT74A                        | Dual D Flip-Flop with Set and Reset with                                      | LS74,LS74A                                           | 4013                                                               | LS                          | 14                   |

| 1101744                       | LSTTL-Compatible Inputs                                                       | 2074,20744                                           | 4013                                                               |                             | 1-4                  |

| HC107                         | Dual J-K Flip-Flop with Reset                                                 | LS73,LS73A,<br>LS107,LS107A                          | *4027                                                              | LS107,<br>LS107A            | 14                   |

| HC109                         | Dual J-K with Set and Reset                                                   | LS109,LS109A                                         | *4027                                                              | LS                          | 16                   |

| HC112                         | Dual J-K Flip-Flop with Set and Reset                                         | LS76,LS76A,<br>LS112,LS112A                          | *4027                                                              | LS112,<br>LS112A            | 16                   |

| HC173                         | Quad 3-State D Flip-Flop with Common Clock and Reset                          | LS173,LS173A                                         | 4076                                                               | LS/CMOS                     | 16                   |

| HC174A                        | Hex D Flip-Flop with Common Clock and Reset                                   | LS174                                                | 4174                                                               | LS/CMOS                     | 16                   |

| HCT174A                       | Hex D Flip-Flop with Common Clock and Reset with<br>LSTTL-Compatible Inputs   | LS174                                                | 4174                                                               | LS                          | 16                   |

| HC175                         | Quad D Flip-Flop with Common Clock and Reset                                  | LS175                                                | 4175                                                               | LS/CMOS                     | 16                   |

| HC273A                        | Octal D Flip-Flop with Common Clock and Reset                                 | LS273                                                |                                                                    | LS                          | 20                   |

| HCT273A                       | Octal D Flip-Flop with Common Clock and Reset with<br>LSTTL-Compatible Inputs | LS273                                                |                                                                    | LS                          | 20                   |

| HC374A                        | Octal 3-State Noninverting D Flip-Flop                                        | LS374,LS574                                          |                                                                    | LS374                       | 20                   |

| НСТ374А                       | Octal 3-State Noninverting D Flip-Flop with LSTTL-Compatible Inputs           | LS374,LS574                                          |                                                                    | LS374                       | 20                   |

| HC534A                        | Octal 3-State Inverting D Flip-Flop                                           | LS534,LS564                                          |                                                                    | LS534                       | 20                   |

| HC564                         | Octal 3-State Inverting D Flip-Flop                                           | LS534,LS564                                          |                                                                    | LS564                       | 20                   |

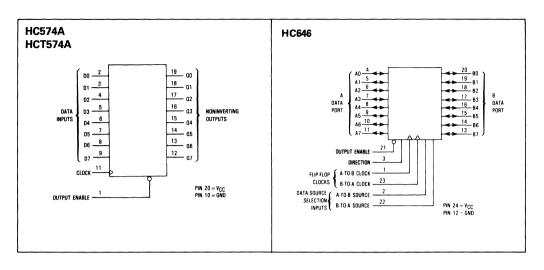

| HC574A                        | Octal 3-State Noninverting D Flip-Flop                                        | LS374,LS574                                          |                                                                    | LS574                       | 20                   |

| HCT574A                       | Octal 3-State Noninverting D Flip-Flop with LSTTL-Compatible Inputs           | LS374,LS574                                          |                                                                    | LS                          | 20                   |

| HC646                         | Octal 3-State Noninverting Bus Transceiver and<br>D Flip-Flop                 | LS646                                                |                                                                    | LS                          | 24                   |

<sup>\*</sup>Suggested alternative

#### **FLIP-FLOPS (Continued)**

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                       | HC<br>73 | HC<br>HCT<br>74A | HC<br>107 | HC<br>109 | HC<br>112 | HC<br>173 | HC<br>HCT<br>174A | HC<br>175 |

|------------------------------------------------------------------------------|----------|------------------|-----------|-----------|-----------|-----------|-------------------|-----------|

| # Pins                                                                       | 14       | 14               | 14        | 16        | 16        | 16        | 16                | 16        |

| Туре                                                                         | J-K      | D                | J-K       | J-K       | J-K       | D         | D                 | D         |

| Dual Device<br>Quad Device<br>Hex Device<br>Octal Device                     | •        | •                | •         | •         | •         | •         | •                 | •         |

| Common Clock<br>Negative-Transition Clocking<br>Positive-Transition Clocking | •        |                  | •         |           | •         | •         | •                 | •         |

| Common, Active-Low Data Enables                                              |          |                  |           |           |           | •         |                   |           |

| Noninverting Outputs<br>Inverting Outputs                                    | :        | :                | :         | :         | :         | •         | •                 |           |

| 3-State Outputs Common, Active-Low Output Enables                            |          |                  |           |           |           | :         |                   |           |

| Common Reset<br>Active-Low Reset<br>Active-High Reset                        | •        | •                | •         | •         | •         | •         | :                 | :         |

| Active-Low Set                                                               |          | •                |           | •         | •         |           |                   |           |

| Transceiver Direction Control                                                |          |                  |           |           |           |           |                   |           |

HC Devices Have CMOS-Compatible Inputs. HCT Devices Have LSTTL-Compatible Inputs.

| Device                                                                       | HC<br>HCT<br>273A | HC<br>HCT<br>374A | HC<br>534A | HC<br>564 | HC<br>HCT<br>574A | HC<br>646 |

|------------------------------------------------------------------------------|-------------------|-------------------|------------|-----------|-------------------|-----------|

| # Pins                                                                       | 20                | 20                | 20         | 20        | 20                | 24        |

| Туре                                                                         | D                 | D                 | D          | D         | D                 | D         |

| Dual Device<br>Quad Device<br>Hex Device<br>Octal Device                     | •                 | •                 | •          | •         | •                 | •         |

| Common Clock<br>Negative-Transition Clocking<br>Positive-Transition Clocking | •                 | •                 | •          | •         | :                 | •         |

| Common, Active-Low Data Enables                                              |                   |                   |            |           |                   |           |

| Noninverting Outputs<br>Inverting Outputs                                    | •                 | •                 | •          | •         | •                 | •         |

| 3-State Outputs<br>Common, Active-Low Output Enables                         |                   | :                 | :          | :         | :                 | :         |

| Common Reset<br>Active-Low Reset<br>Active-High Reset                        | :                 |                   |            |           |                   |           |

| Active-Low Set                                                               |                   |                   |            |           |                   |           |

| Transceiver Direction Control                                                |                   |                   |            |           |                   | :         |

These devices are identical in function and are different in pinout only: HC33 and HC107

HC374 and HC574

HC534 and HC564

#### **FLIP-FLOPS (Continued)**

#### **FLIP-FLOPS (Continued)**

#### **DIGITAL DATA SELECTORS/MULTIPLEXERS**

| Device<br>Number<br>MC54/MC74 | Function                                                               | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

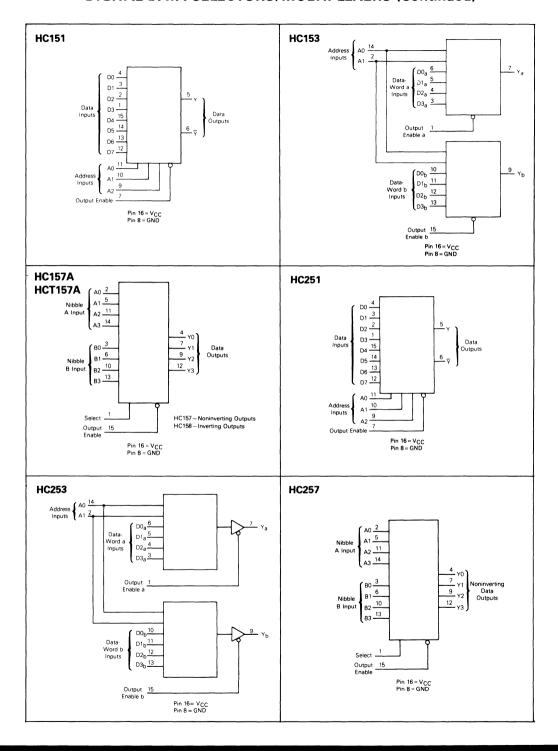

| HC151                         | 8-Input Data Selector/Multiplexer                                      | LS151                                                | *4512                                               | LS                          | 16                   |

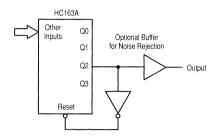

| HC153                         | Dual 4-Input Data Selector/Multiplexer                                 | LS153                                                | 4539                                                | LS/CMOS                     | 16                   |

| HC157A                        | Quad 2-Input Noninverting Data Selector/Multiplexer                    | LS157                                                | *4519                                               | LS                          | 16                   |

| HCT157A                       | Quad 2-Input Data Selector/Multiplexer with<br>LSTTL-Compatible Inputs | LS157                                                | *4519                                               | LS                          | 16                   |

| HC251                         | 8-Input Data Selector/Multiplexer with 3-State Outputs                 | LS251                                                | *4512                                               | LS                          | 16                   |

| HC253                         | Dual 4-Input Data Selector/Multiplexer with 3-State<br>Outputs         | LS253                                                | *4539                                               | LS/CMOS                     | 16                   |

| HC257                         | Quad 2-Input Data Selector/Multiplexer with 3-State<br>Outputs         | LS257                                                | *4519                                               | LS                          | 16                   |

<sup>\*</sup>Suggested alternative

#### HC Devices Have CMOS-Compatible Inputs.

| Device                                                                                      | HC<br>151                         | HC<br>153                         | HC<br>HCT<br>157A                           | HC<br>251                         | HC<br>253                         | HC<br>257                                   |

|---------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|---------------------------------------------|-----------------------------------|-----------------------------------|---------------------------------------------|

| # Pins                                                                                      | 16                                | 16                                | 16                                          | 16                                | 16                                | 16                                          |

| Description                                                                                 | One of<br>8 inputs is<br>selected | One of<br>4 inputs is<br>selected | One of<br>two 4-bit<br>words is<br>selected | One of<br>8 inputs is<br>selected | One of<br>4 inputs is<br>selected | One of<br>two 4-bit<br>words is<br>selected |

| Single Device<br>Dual Device<br>Quad Device                                                 | •                                 | •                                 | •                                           | •                                 | •                                 | •                                           |

| Data Latch with Active-Low<br>Latch Enable                                                  |                                   |                                   |                                             |                                   |                                   |                                             |

| Common Address 1-Bit Binary Address 2-Bit Binary Address 3-Bit Binary Address               | •                                 | •                                 | •                                           | •                                 | •                                 | •                                           |

| Address Latch (Transparent) Address Latch (Non-transparent) Active-Low Address Latch Enable |                                   |                                   |                                             |                                   |                                   | •                                           |

| Noninverting Output<br>Inverting Output                                                     | :                                 | •                                 | •                                           | •                                 | •                                 | •                                           |

| 3-State Outputs                                                                             |                                   |                                   |                                             | •                                 | •                                 | •                                           |

| Common Output Enable<br>Active-High Output Enable<br>Active-Low Output Enable               | •                                 | •                                 | •                                           | •                                 | •                                 | •                                           |

implies the device has two such enables

#### **DIGITAL DATA SELECTORS/MULTIPLEXERS (Continued)**

#### **DECODERS/DEMULTIPLEXERS/DISPLAY DRIVERS**

| Device<br>Number<br>MC54/MC74 | Function                                                     | Functional<br>Equivalent<br>LSTTL<br>Device<br>54/74 | Functional Equivalent CMOS Device MC1XXXX or CDXXXX | Direct Pin<br>Compatibility | Number<br>of<br>Pins |

|-------------------------------|--------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------|-----------------------------|----------------------|

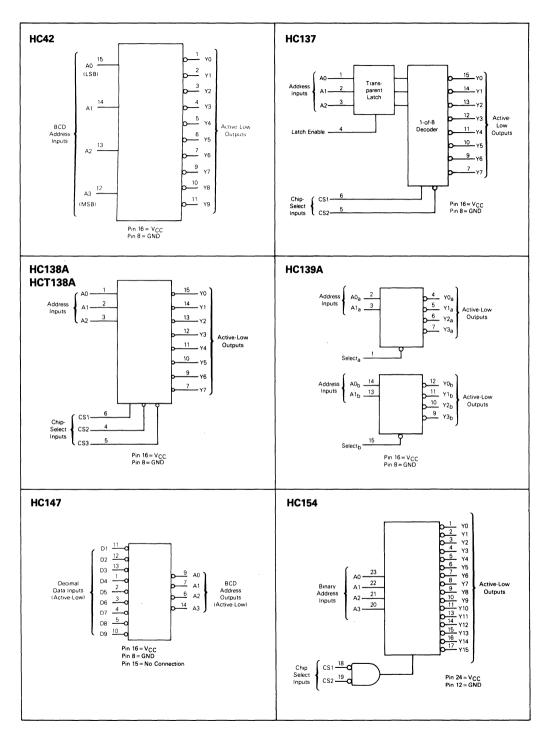

| HC42                          | 1-of-10 Decoder                                              | LS42                                                 | *4028                                               | LS                          | 16                   |

| HC137                         | 1-of-8 Decoder/Demultiplexer with Address Latch              | LS137                                                | *4028                                               | LS                          | 16                   |

| HC138A                        | 1-of-8 Decoder/Demultiplexer                                 | LS138                                                | *4028                                               | LS                          | 16                   |

| HCT138A                       | 1-of-8 Decoder/Demultiplexer with LSTTL-Compatible<br>Inputs | LS138                                                | *4028                                               | LS                          | 16                   |

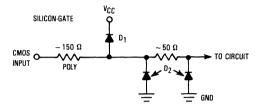

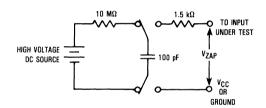

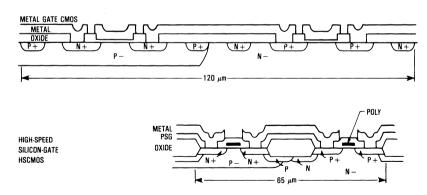

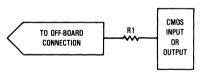

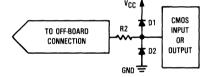

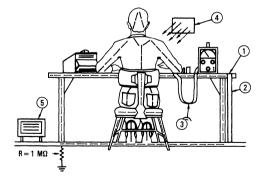

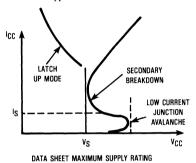

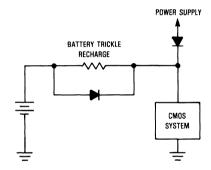

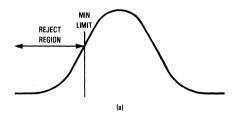

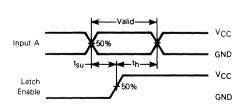

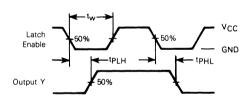

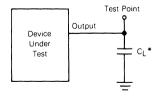

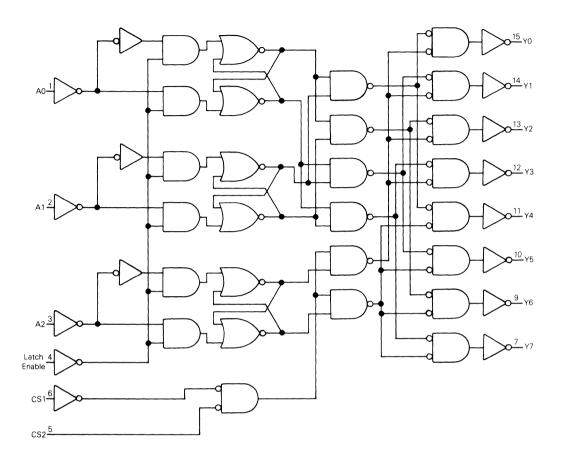

| HC139A                        | Dual 1-of-4 Decoder/Demultiplexer                            | LS139                                                | 4556                                                | LS/CMOS                     | 16                   |