# INTERFACING MULTIPLEXED BUS PERIPHERALS WITH NON-MULTIPLEXED MPUs

Prepared by

Rex Davis

Microprocessor Application Engineering

Austin, Texas

## INTRODUCTION

In general, 8-bit microprocessor buses may be divided into two major groups: multiplexed and non-multiplexed. A microprocessor (MPU) which has a non-multiplexed bus configuration requires two separate buses: an address bus and a data bus. However, an MPU which has a multiplexed bus configuration shares one bus for both address and data; i.e., the lower eight bits of address are output on the same lines that are used for the data bus. To accomplish this, a multiplexed bus cycle must be divided in two parts. During the first part of the cycle, the lower eight bits of address are output on the multiplexed bus pins. During the second part of the cycle, data is input or output via the multiplexed bus pins.

It is important that the two parts of the cycle be identified by both the multiplexed and non-multiplexed MPUs. For this reason, an address strobe line (AS or ALE) is used to indicate when the address is valid. During the second part of the cycle, the multiplexed bus lines are used to transfer data, and a data strobe line (DS) is used to indicate this.

Interfacing a multiplexed bus MPU (such as MC6803 or MC146805E2) with non-multiplexed bus peripherals is relatively straightforward. The interface can be accomplished by simply providing an external latch to capture the multiplexed address for the entire bus cycle. However, providing an interface between a non-multiplexed bus MPU (such as the MC6800 and the MC6809) and multiplexed bus peripherals is more difficult.

Generating the required address and data strobes, while also guaranteeing that the address and data are on and off the multiplexed bus at the required times, is not possible with most non-multiplexed MPUs. Methods for providing an interface between non-multiplexed bus MPUs and multiplexed bus peripherals are discussed below.

### SUGGESTED INTERFACING METHODS

One method that is often used, but is not too efficient, employs the I/O lines of a peripheral interface adapter (PIA) to provide the multiplexed bus signals to the peripherals. This method, while fine for single-chip computers, requires excessive software, I/O lines, and execution time.

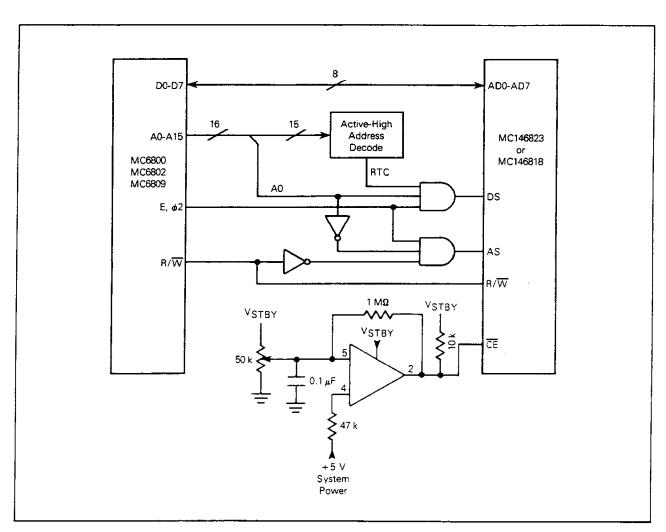

Another method, for allowing a non-multiplexed bus MPU to read or write multiplexed bus peripherals, is to consider the multiplexed bus as a two-register device. One register could be the address latch and the other could be the data register. By connecting the non-multiplexed bus to the multiplexed bus, as shown in Figure 1, the address strobe (AS) is generated by any MPU write to an even address (A0 is low). Although AS causes the state of the multiplexed pins to be captured in the address latch, no data is transferred until the data strobe (DS, RD, or WR) is generated. The data strobe is not generated until a specific decoded, odd address occurs; i.e., A0 is high. Thus, a valid access can only be made by first writing to the location (\$00-\$3F) of the byte to be accessed at an even address, and then by either reading from or writing to the decoded odd address. The software subroutine required to generate the address strobe (AS) and data strobe (DS) signals for the interface shown in Figure 1 is listed in Figure 2. The location to be accessed is contained in accumulator A and data is transferred via accumulator B. The following example clears register A (location \$0A) and then reads the data at location \$25.

| LDAA | #\$0A | Load \$0A into accumulator A for location   |

|------|-------|---------------------------------------------|

| CLRB |       | Load \$00 into accumulator B for data       |

| BSR  | WRITE | Call subroutine to write data               |

| CLRA |       | Load \$00 into accumulator A for location   |

| BSR  | READ  | Call subroutine to read data                |

| STAB | DATA  | Data is returned to accumulator B and saved |

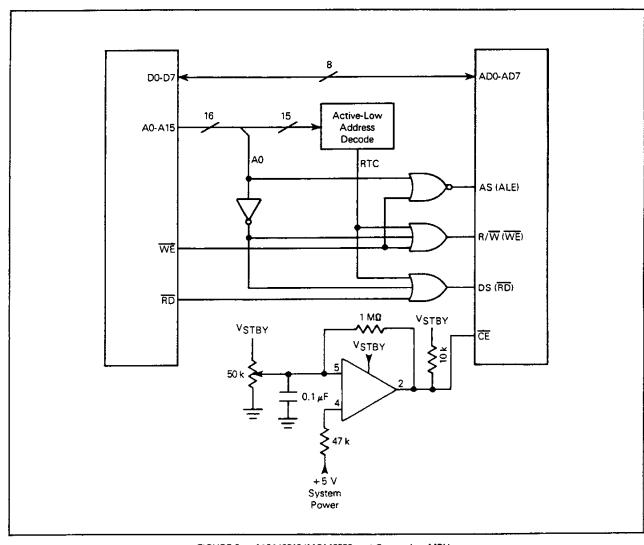

The schematic diagram shown in Figure 1 provides an interface between Motorola devices: MC6800/MC6802/MC6809 MPU interfaced with an MC146818 Real Time Clock or MC146823 CMOS Parallel Interface. Since both the MC146818 and the MC146823 are implemented with the Motorola MOTEL circuit (for MOTorola and IntEL bus compatibility), they can be interfaced with either of the two most common multiplexed bus structures. The hardware required for interfacing a competitor's non-multiplexed MPU with either the MC146818 or MC146823 is shown in Figure 3.

Both the MC146818 and MC146823 are CMOS devices and may be used with a battery back-up; however, power-

down is different for each device. Also, on both devices CE is used to isolate the device from the bus except as follows: (1) when AS is high on the MC146823 and (2) on the MC146818 CE must be valid before the falling edge of AS and it must remain valid until the training edge of DS. For these reasons, the comparator circuit shown in Figures 1 and 3, is used to provide CE. One input to the comparator is connected to the +5 V system power source. The other comparator input is connected to a reference voltage (assume +4 V). The battery backup voltage, used to provide the reference source, should approximate the system +5 V supply. When the system voltage fails below the reference level, the comparator toggles and deselects the MC146818 (CE goes high). This isolates the RTC from the bus. The comparator toggling action precludes spurious writes to the MC146818 RAM or other registers during the time between system power loss and trigger output. The comparator configuration shown provides some hysteresis. This ensures that there is no input voltage which would cause a bouncing effect at the CE pin.

### NOTE

If a battery back-up for the MC146818 or MC146823 is not used, the  $\overline{\text{CE}}$  pin can be grounded.

FIGURE 1 — MC146818/MC146823 and Motorola MPU Non-Multiplexed Bus Interface Schematic Diagram

| READ  | STAA | RTC   | Generate AS and latch data from ACCA     |

|-------|------|-------|------------------------------------------|

|       | LDAB | RTC+1 | Generate DS and load ACCB with data read |

|       | RTS  |       | Return                                   |

| WRITE | STAA | RTC   | Generate AS and latch data from ACCA     |

| 1     | STAB | RTC+1 | Generate DS and store data from ACCB     |

|       | RTS  |       | Return                                   |

|       |      |       |                                          |

FIGURE 2 — Subroutine for Controlling Interface Between Non-Multiplexed Bus and MC146818/MC146823

Figure 3 — MC146818/MC146823 and Competitor MPU Non-Multiplexed Bus Interface Schematic Diagram

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

# Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.