# **PowerPC Virtual Environment Architecture**

## **Book II**

Version 2.01

December 2003

Manager:

Joe Wetzel/Poughkeepsie/IBM

**Technical Content:**

Ed Silha/Austin/IBM Cathy May/Watson/IBM

Brad Frey/Austin/IBM

The following paragraph does not apply to the United Kingdom or any country or state where such provisions are inconsistent with local law.

The specifications in this manual are subject to change without notice. This manual is provided "AS IS". International Business Machines Corp. makes no warranty of any kind, either expressed or implied, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose.

International Business Machines Corp. does not warrant that the contents of this publication or the accompanying source code examples, whether individually or as one or more groups, will meet your requirements or that the publication or the accompanying source code examples are error-free.

This publication could include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new editions of the publication.

Address comments to IBM Corporation, Internal Zip 9630, 11400 Burnett Road, Austin, Texas 78758-3493. IBM may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

The following terms are trademarks of the International Business Machines Corporation in the United States and/or other countries:

IBM PowerPC RISC/System 6000 POWER POWER2 POWER4 POWER4+ IBM System/370

Notice to U.S. Government Users—Documentation Related to Restricted Rights—Use, duplication or disclosure is subject to restrictions set fourth in GSA ADP Schedule Contract with IBM Corporation.

© Copyright International Business Machines Corporation, 1994, 2003. All rights reserved.

## **Preface**

This document defines the additional instructions and facilities, beyond those of the PowerPC User Instruction Set Architecture, that are provided by the PowerPC Virtual Environment Architecture. It covers the storage model and related instructions and facilities available to the application programmer, and the Time Base as seen by the application programmer.

Other related documents define the PowerPC User Instruction Set Architecture, the PowerPC Operating Environment Architecture, and PowerPC Implementation Features. Book I, *PowerPC User Instruction Set Architecture* defines the base instruction set and related facilities available to the application pro-

grammer. Book III, PowerPC Operating Environment Architecture defines the system (privileged) instructions and related facilities. Book IV, PowerPC Implementation Features defines the implementation-dependent aspects of a particular implementation.

As used in this document, the term "PowerPC Architecture" refers to the instructions and facilities described in Books I, II, and III. The description of the instantiation of the PowerPC Architecture in a given implementation includes also the material in Book IV for that implementation.

# **Table of Contents**

| Chapter 1. Storage Model                    | 1 4.3 Computing Time of Day from the      |

|---------------------------------------------|-------------------------------------------|

|                                             | 1 Time Base                               |

| 1.2 Introduction                            | 2                                         |

| 1.3 Virtual Storage                         | 2 Chapter 5. Optional Facilities and      |

| 1.4 Single-Copy Atomicity                   | 3 Instructions                            |

| 1.5 Cache Model                             | 3 5.1 External Control                    |

| 1.6 Storage Control Attributes              | 4 5.1.1 External Access Instructions 34   |

|                                             | 4 5.2 Storage Control Instructions 35     |

| 1.6.2 Caching Inhibited                     | 4 5.2.1 Cache Management Instructions 35  |

| 1.6.3 Memory Coherence Required             | 5 5.3 Little-Endian                       |

|                                             | 5                                         |

| 1.7 Shared Storage                          | 6 Appendix A. Assembler Extended          |

|                                             | 6 Mnemonics                               |

| =                                           | 8 A.1 Synchronize Mnemonics 37            |

|                                             | 8                                         |

| 1.8 Instruction Storage 1                   | O Appendix B. Programming Examples        |

| 1.8.1 Concurrent Modification and           | for Charina Storago                       |

| Execution of Instructions 1                 | B.1 Atomic Update Primitives 39           |

|                                             | B.2 Lock Acquisition and Release, and     |

| Chapter 2. Effect of Operand                | Related Techniques 41                     |

| Placement on Performance 1                  | B.2.1 Lock Acquisition and Import         |

| 2.1 Instruction Restart 1                   | Barriers 41                               |

|                                             | B.2.2 Lock Release and Export Barriers 42 |

| Chapter 3. Storage Control                  | B.2.3 Safe Fetch 42                       |

| Instructions                                |                                           |

| 3.1 Parameters Useful to Application        | B.4 Notes                                 |

| Programs1                                   |                                           |

| 3.2 Cache Management Instructions . 1       |                                           |

| 3.2.1 Instruction Cache Instruction 1       |                                           |

| 3.2.2 Data Cache Instructions 1             | Changed LOWEN Milenbilles 43              |

| 3.3 Synchronization Instructions 2          | Appendix D. New Instructions 47           |

| 3.3.1 Instruction Synchronize Instruction 2 |                                           |

| 3.3.2 Load And Reserve and Store            |                                           |

| Conditional Instructions 2                  | Appendix E. PowerPC Virtual               |

| 3.3.3 Memory Barrier Instructions 2         | Environment Instruction Set 49            |

|                                             | Indov 54                                  |

| Chapter 4. Time Base                        |                                           |

| 4.1 Time Base Instructions 3                | Loot Dono Find of Doormont                |

| 4.2 Reading the Time Base 3                 | Last Page - End of Document 53            |

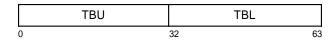

# **Figures**

| 1. | Performance effects of storage operand |    |

|----|----------------------------------------|----|

|    | placement                              | 13 |

| 2. | Time Base                              | 29 |

| 3. | Performance effects of storage operand |    |

|    | placement, Little-Endian mode          | 36 |

## Chapter 1. Storage Model

| 1.1 Definitions and Notation    | 1 | 1.7 Shared Storage                     | 6  |

|---------------------------------|---|----------------------------------------|----|

| 1.2 Introduction                | 2 | 1.7.1 Storage Access Ordering          | 6  |

| 1.3 Virtual Storage             | 2 | 1.7.2 Storage Ordering of I/O Accesses | 8  |

| 1.4 Single-Copy Atomicity       | 3 | 1.7.3 Atomic Update                    | 8  |

| 1.5 Cache Model                 |   | 1.7.3.1 Reservations                   | 8  |

| 1.6 Storage Control Attributes  | 4 | 1.7.3.2 Forward Progress               | 10 |

| 1.6.1 Write Through Required    | 4 | 1.8 Instruction Storage                | 10 |

| 1.6.2 Caching Inhibited         | 4 | 1.8.1 Concurrent Modification and      |    |

| 1.6.3 Memory Coherence Required |   | Execution of Instructions              | 12 |

| 1.6.4 Guarded                   | 5 |                                        |    |

## 1.1 Definitions and Notation

The following definitions, in addition to those specified in Book I, are used in this Book. In these definitions, "Load instruction" includes the Cache Management and other instructions that are stated in the instruction descriptions to be "treated as a Load", and similarly for "Store instruction".

#### processor

A hardware component that executes the instructions specified in a program.

#### system

A combination of processors, storage, and associated mechanisms that is capable of executing programs. Sometimes the reference to system includes services provided by the operating system.

#### main storage

The level of the storage hierarchy in which all storage state is visible to all processors and mechanisms in the system.

#### ■ instruction storage

The view of storage as seen by the mechanism that fetches instructions.

#### data storage

The view of storage as seen by a *Load* or *Store* instruction.

#### program order

The execution of instructions in the order required by the sequential execution model. (See the section entitled "Instruction Execution Order" in Book I. A *dcbz* instruction that modifies

storage which contains instructions has the same effect with respect to the sequential execution model as a *Store* instruction as described there.)

#### storage location

A contiguous sequence of bytes in storage. When used in association with a specific instruction or the instruction fetching mechanism, the length of the sequence of bytes is typically implied by the operation. In other uses, it may refer more abstractly to a group of bytes which share common storage attributes.

#### storage access

An access to a storage location. There are three (mutually exclusive) kinds of storage access.

#### data access

An access to the storage location specified by a *Load* or *Store* instruction, or, if the access is performed "out-of-order" (see Book III), an access to a storage location as if it were the storage location specified by a *Load* or *Store* instruction.

#### instruction fetch

An access for the purpose of fetching an instruction.

#### implicit access

An access by the processor for the purpose of address translation or reference and change recording (see Book III).

#### caused by, associated with

#### caused by

A storage access is said to be caused by an instruction if the instruction is a *Load* or *Store* and the access (data access) is to the storage location specified by the instruction.

#### associated with

A storage access is said to be associated with an instruction if the access is for the purpose of fetching the instruction (instruction fetch), or is a data access caused by the instruction, or is an implicit access that occurs as a side effect of fetching or executing the instruction.

#### prefetched instructions

Instructions for which a copy of the instruction has been fetched from instruction storage, but the instruction has not yet been executed.

#### uniprocessor

A system that contains one processor.

#### multiprocessor

A system that contains two or more processors.

#### shared storage multiprocessor

A multiprocessor that contains some common storage, which all the processors in the system can access.

#### performed

A load or instruction fetch by a processor or mechanism (P1) is performed with respect to any processor or mechanism (P2) when the value to be returned by the load or instruction fetch can no longer be changed by a store by P2. A store by P1 is performed with respect to P2 when a load by P2 from the location accessed by the store will return the value stored (or a value stored subsequently). An instruction cache block invalidation by P1 is performed with respect to P2 when an instruction fetch by P2 will not be satisfied from the copy of the block that existed in its instruction cache when the instruction causing the invalidation was executed, and similarly for a data cache block invalidation. The preceding definitions apply regardless of whether P1 and P2 are the same entity.

#### page

An aligned unit of storage for which protection control attributes are independently specifiable and for which reference and change status are independently recorded. Two virtual page sizes are supported simultaneously, 4 KB and a larger size. The larger size is an implementation-dependent power of 2 (bytes). Real pages are always 4 KB.

#### block

The aligned unit of storage operated on by each Cache Management instruction. The size of a block can vary by instruction and by implementation. The maximum block size is 4 KB.

#### aligned storage access

A load or store is aligned if the address of the target storage location is a multiple of the size of the transfer effected by the instruction.

## 1.2 Introduction

The PowerPC User Instruction Set Architecture, discussed in Book I, defines storage as a linear array of bytes indexed from 0 to a maximum of  $2^{64} - 1$ . Each byte is identified by its index, called its address, and each byte contains a value. This information is sufficient to allow the programming of applications that require no special features of any particular system environment. The PowerPC Virtual Environment Architecture, described herein, expands this simple storage model to include caches, virtual storage, and shared storage multiprocessors. The PowerPC Virtual Environment Architecture, in conjunction with services based on the PowerPC Operating Environment Architecture (see Book III) and provided by the operating system, permits explicit control of this expanded storage model. A simple model for sequential execution allows at most one storage access to be performed at a time and requires that all storage accesses appear to be performed in program order. In contrast to this simple model, the PowerPC Architecture specifies a relaxed model of storage consistency. In a multiprocessor system that allows multiple copies of a storage location, aggressive implementations of the architecture can permit intervals of time during which different copies of a storage location have different values. This chapter describes features of the PowerPC Architecture that enable programmers to write correct programs for this storage model.

## 1.3 Virtual Storage

The PowerPC system implements a virtual storage model for applications. This means that a combination of hardware and software can present a storage model that allows applications to exist within a "virtual" address space larger than either the effective address space or the real address space.

Each program can access 264 bytes of "effective address" (EA) space, subject to limitations imposed by the operating system. In a typical PowerPC system, each program's EA space is a subset of a larger "virtual address" (VA) space managed by the operating system.

Each effective address is translated to a real address (i.e., to an address of a byte in real storage or on an I/O device) before being used to access storage. The hardware accomplishes this, using the address translation mechanism described in Book III. The operating system manages the real (physical) storage resources of the system, by setting up the tables and other information used by the hardware address translation mechanism.

Book II deals primarily with effective addresses that are in "segments" translated by the "address translation mechanism" (see Book III). Each such effective address lies in a "virtual page", which is mapped to a "real page" (4 KB virtual page) or to a contiguous sequence of real pages (large virtual page) before data or instructions in the virtual page are accessed.

In general, real storage may not be large enough to map all the virtual pages used by the currently active applications. With support provided by hardware, the operating system can attempt to use the available real pages to map a sufficient set of virtual pages of the applications. If a sufficient set is maintained, "paging" activity is minimized. If not, performance degradation is likely.

The operating system can support restricted access to virtual pages (including read/write, read only, and no access; see Book III), based on system standards (e.g., program code might be read only) and application requests.

## 1.4 Single-Copy Atomicity

An access is *single-copy atomic*, or simply *atomic*, if it is always performed in its entirety with no visible fragmentation. Atomic accesses are thus *serialized*: each happens in its entirety in some order, even when that order is not specified in the program or enforced between processors.

In PowerPC the following single-register accesses are always atomic:

- byte accesses (all bytes are aligned on byte boundaries)

- halfword accesses aligned on halfword boundaries

- word accesses aligned on word boundaries

- doubleword accesses aligned on doubleword boundaries

No other accesses are guaranteed to be atomic. For example, the access caused by the following instructions is not guaranteed to be atomic.

- any Load or Store instruction for which the operand is unaligned

- Imw, stmw, Iswi, Iswx, stswi, stswx

- any Cache Management instruction

An access that is not atomic is performed as a set of smaller disjoint atomic accesses. The number and alignment of these accesses are implementation-dependent, as is the relative order in which they are performed.

The results for several combinations of loads and stores to the same or overlapping locations are described below.

- When two processors execute atomic stores to locations that do not overlap, and no other stores are performed to those locations, the contents of those locations are the same as if the two stores were performed by a single processor.

- When two processors execute atomic stores to the same storage location, and no other store is performed to that location, the contents of that location are the result stored by one of the processors.

- When two processors execute stores that have the same target location and are not guaranteed to be atomic, and no other store is performed to that location, the result is some combination of the bytes stored by both processors.

- 4. When two processors execute stores to overlapping locations, and no other store is performed to those locations, the result is some combination of the bytes stored by the processors to the overlapping bytes. The portions of the locations that do not overlap contain the bytes stored by the processor storing to the location.

- 5. When a processor executes an atomic store to a location, a second processor executes an atomic load from that location, and no other store is performed to that location, the value returned by the load is the contents of the location before the store or the contents of the location after the store

- 6. When a load and a store with the same target location can be executed simultaneously, and no other store is performed to that location, the value returned by the load is some combination of the contents of the location before the store and the contents of the location after the store.

### 1.5 Cache Model

A cache model in which there is one cache for instructions and another cache for data is called a "Harvard-style" cache. This is the model assumed by the PowerPC Architecture, e.g., in the descriptions of the *Cache Management* instructions in Section 3.2, "Cache Management Instructions" on page 16. Alternative cache models may be implemented (e.g., a "combined cache" model, in which a single cache is used for both instructions and data, or a model in which there are several levels of caches), but they support the programming model implied by a Harvard-style cache.

The processor is not required to maintain copies of storage locations in the instruction cache consistent with modifications to those storage locations (e.g., modifications caused by *Store* instructions).

A location in the data cache is considered to be modified in that cache if the location has been modified (e.g., by a *Store* instruction) and the modified data have not been been written to main storage.

Cache Management instructions are provided so that programs can manage the caches when needed. For example, program management of the caches is needed when a program generates or modifies code that will be executed (i.e., when the program modifies data in storage and then attempts to execute the modified data as instructions). The Cache Management instructions are also useful in optimizing the use of memory bandwidth in such applications as graphics and numerically intensive computing. The functions performed by these instructions depend on the storage control attributes associated with the specified storage location (see Section 1.6, "Storage Control Attributes").

The Cache Management instructions allow the program to do the following.

- invalidate the copy of storage in an instruction cache block (*icbi*)

- provide a hint that the program will probably soon access a specified data cache block (dcbt, dcbtst)

- set the contents of a data cache block to zeros (dcbz)

- copy the contents of a modified data cache block to main storage (dcbst)

- copy the contents of a modified data cache block to main storage and make the copy of the block in the data cache invalid (dcbf)

## 1.6 Storage Control Attributes

Some operating systems may provide a means to allow programs to specify the storage control attributes described in this section. Because the support provided for these attributes by the operating system may vary between systems, the details of the specific system being used must be known before these attributes can be used.

Storage control attributes are associated with units of storage that are multiples of the page size. Each storage access is performed according to the storage control attributes of the specified storage location, as described below. The storage control attributes are the following.

- Write Through Required

- Caching Inhibited

- Memory Coherence Required

- Guarded

These attributes have meaning only when an effective address is translated by the processor performing the storage access. All combinations of these attributes

are supported except Write Through Required with Caching Inhibited.

#### **Programming Note**

The Write Through Required and Caching Inhibited attributes are mutually exclusive because, as described below, the Write Through Required attribute permits the storage location to be in the data cache while the Caching Inhibited attribute does not.

Storage that is Write Through Required or Caching Inhibited is not intended to be used for general-purpose programming. For example, the *Iwarx*, *Idarx*, *stwcx.*, and *stdcx.* instructions may cause the system data storage error handler to be invoked if they specify a location in storage having either of these attributes.

In the remainder of this section, "Load instruction" includes the Cache Management and other instructions that are stated in the instruction descriptions to be "treated as a Load", and similarly for "Store instruction".

## 1.6.1 Write Through Required

A store to a Write Through Required storage location is performed in main storage. A *Store* instruction that specifies a location in Write Through Required storage may cause additional locations in main storage to be accessed. If a copy of the block containing the specified location is retained in the data cache, the store is also performed in the data cache. The store does not cause the block to be considered to be modified in the data cache.

In general, accesses caused by separate *Store* instructions that specify locations in Write Through Required storage may be combined into one access. Such combining does not occur if the *Store* instructions are separated by a *sync* instruction or by an *eieio* instruction.

## 1.6.2 Caching Inhibited

An access to a Caching Inhibited storage location is performed in main storage. A Load instruction that specifies a location in Caching Inhibited storage may cause additional locations in main storage to be accessed unless the specified location is also Guarded. An instruction fetch from Caching Inhibited storage may cause additional words in main storage to be accessed. No copy of the accessed locations is placed into the caches.

In general, non-overlapping accesses caused by separate *Load* instructions that specify locations in Caching Inhibited storage may be combined into one

access, as may non-overlapping accesses caused by separate Store instructions that specify locations in Caching Inhibited storage. Such combining does not occur if the Load or Store instructions are separated by a sync instruction, or by an eieio instruction if the storage is also Guarded.

## 1.6.3 Memory Coherence Required

An access to a Memory Coherence Required storage location is performed coherently, as follows.

Memory coherence refers to the ordering of stores to a single location. Atomic stores to a given location are coherent if they are serialized in some order, and no processor or mechanism is able to observe any subset of those stores as occurring in a conflicting order. This serialization order is an abstract sequence of values; the physical storage location need not assume each of the values written to it. For example, a processor may update a location several times before the value is written to physical storage. The result of a store operation is not available to every processor or mechanism at the same instant, and it may be that a processor or mechanism observes only some of the values that are written to a location. However, when a location is accessed atomically and coherently by all processor and mechanisms, the sequence of values loaded from the location by any processor or mechanism during any interval of time forms a subsequence of the sequence of values that the location logically held during that interval. That is, a processor or mechanism can never load a "newer" value first and then, later, load an "older" value.

Memory coherence is managed in blocks called coherence blocks. Their size is implementation-dependent (see the Book IV, PowerPC Implementation Features document for the implementation), but is usually larger than a word and often the size of a cache block.

For storage that is not Memory Coherence Required, software must explicitly manage memory coherence to the extent required by program correctness. The operations required to do this may be systemdependent.

Because the Memory Coherence Required attribute for a given storage location is of little use unless all processors that access the location do so coherently, in statements about Memory Coherence Required storage elsewhere in Books I - III it is generally assumed that the storage has the Memory Coherence Required attribute for all processors that access it.

#### **Programming Note**

Operating systems that allow programs to request that storage not be Memory Coherence Required should provide services to assist in managing memory coherence for such storage, including all system-dependent aspects thereof.

In most systems the default is that all storage is Memory Coherence Required. For some applications in some systems, software management of coherence may yield better performance. In such cases, a program can request that a given unit of storage not be Memory Coherence Required, and can manage the coherence of that storage by using the sync instruction, the Cache Management instructions, and services provided by the operating system.

#### 1.6.4 Guarded

A data access to a Guarded storage location is performed only if either (a) the access is caused by an instruction that is known to be required by the sequential execution model, or (b) the access is a load and the storage location is already in a cache. If the storage is also Caching Inhibited, only the storage location specified by the instruction is accessed; otherwise any storage location in the cache block containing the specified storage location may be accessed.

Instructions are not fetched from virtual storage that is Guarded. If the effective address of the current instruction is in such storage, the system instruction storage error handler is invoked.

#### Programming Note -

In some implementations, instructions may be executed before they are known to be required by the sequential execution model. Because the results of instructions executed in this manner are discarded if it is later determined that those instructions would not have been executed in the sequential execution model, this behavior does not affect most programs.

This behavior does affect programs that access storage locations that are not "well-behaved" (e.g., a storage location that represents a control register on an I/O device that, when accessed, causes the device to perform an operation). To avoid unintended results, programs that access such storage locations should request that the storage be Guarded, and should prevent such storage locations from being in a cache (e.g., by requesting that the storage also be Caching Inhibited).

## 1.7 Shared Storage

This architecture supports the sharing of storage between programs, between different instances of the same program, and between processors and other mechanisms. It also supports access to a storage location by one or more programs using different effective addresses. All these cases are considered storage sharing. Storage is shared in blocks that are an integral number of pages.

When the same storage location has different effective addresses, the addresses are said to be *aliases*. Each application can be granted separate access privileges to aliased pages.

## 1.7.1 Storage Access Ordering

The storage model for the ordering of storage accesses is *weakly consistent*. This model provides an opportunity for improved performance over a model that has stronger consistency rules, but places the responsibility on the program to ensure that ordering or synchronization instructions are properly placed when storage is shared by two or more programs.

The order in which the processor performs storage accesses, the order in which those accesses are performed with respect to another processor or mechanism, and the order in which those accesses are performed in main storage may all be different. Several means of enforcing an ordering of storage accesses are provided to allow programs to share storage with other programs, or with mechanisms such as I/O devices. These means are listed below. The phrase "to the extent required by the associated Memory Coherence Required attributes" refers to the Memory Coherence Required attribute, if any, associated with each access.

If two Store instructions specify storage locations that are both Caching Inhibited and Guarded, the corresponding storage accesses are performed in program order with respect to any processor or mechanism.

- If a Load instruction depends on the value returned by a preceding Load instruction (because the value is used to compute the effective address specified by the second Load), the corresponding storage accesses are performed in program order with respect to any processor or mechanism to the extent required by the associated Memory Coherence Required attributes. This applies even if the dependency has no effect on program logic (e.g., the value returned by the first Load is ANDed with zero and then added to the effective address specified by the second Load).

- When a processor (P1) executes a Synchronize or eieio instruction a memory barrier is created, which orders applicable storage accesses pairwise, as follows. Let A be a set of storage accesses that includes all storage accesses associated with instructions preceding the barriercreating instruction, and let B be a set of storage accesses that includes all storage accesses associated with instructions following the barriercreating instruction. For each applicable pair a<sub>i</sub>,b<sub>i</sub> of storage accesses such that ai is in A and bi is in B, the memory barrier ensures that a; will be performed with respect to any processor or mechanism, to the extent required by the associated Memory Coherence Required attributes, before bi is performed with respect to that processor or mechanism.

The ordering done by a memory barrier is said to be "cumulative" if it also orders storage accesses that are performed by processors and mechanisms other than P1, as follows.

- A includes all applicable storage accesses by any such processor or mechanism that have been performed with respect to P1 before the memory barrier is created.

- B includes all applicable storage accesses by any such processor or mechanism that are performed after a Load instruction executed by that processor or mechanism has returned the value stored by a store that is in B.

No ordering should be assumed among the storage accesses caused by a single instruction (i.e, by an instruction for which the access is not atomic), and no means are provided for controlling that order.

#### Programming Note

Because stores cannot be performed "out-of-order" (see Book III, PowerPC Operating Environment Architecture), if a Store instruction depends on the value returned by a preceding Load instruction (because the value returned by the Load is used to compute either the effective address specified by the Store or the value to be stored), the corresponding storage accesses are performed in program order. The same applies if whether the Store instruction is executed depends on a conditional Branch instruction that in turn depends on the value returned by a preceding Load instruction.

Because an isync instruction prevents the execution of instructions following the isync until instructions preceding the isync have completed, if an isync follows a conditional Branch instruction that depends on the value returned by a preceding Load instruction, the load on which the Branch depends is performed before any loads caused by instructions following the isync. This applies even if the effects of the "dependency" are independent of the value loaded (e.g., the value is compared to itself and the Branch tests the EQ bit in the selected CR field), and even if the branch target is the sequentially next instruction.

With the exception of the cases described above and earlier in this section, data dependencies and control dependencies do not order storage accesses. Examples include the following.

- If a Load instruction specifies the same storage location as a preceding Store instruction and the location is in storage that is not Caching Inhibited, the load may be satisfied from a "store queue" (a buffer into which the processor places stored values before presenting them to the storage subsystem), and not be visible to other processors and mechanisms. A consequence is that if a subsequent Store depends on the value returned by the Load, the two stores need not be performed in program order with respect to other processors and mechanisms.

- Because a Store Conditional instruction may complete before its store has been performed, a conditional Branch instruction that depends on the CR0 value set by a Store Conditional instruction does not order the Conditional's store with respect to storage accesses caused by instructions that follow the Branch.

Because processors may predict branch target addresses and branch condition resolution, control dependencies (e.g., branches) do not order storage accesses except as described above. For example, when a subroutine returns to its caller the return address may be predicted, with the result that loads caused by instructions at or after the return address may be performed before the load that obtains the return address is performed.

Because processors may implement nonarchitected duplicates of architected resources (e.g., GPRs, CR fields, and the Link Register), resource dependencies (e.g., specification of the same target register for two Load instructions) do not order storage accesses.

Examples of correct uses of dependencies, sync, lwsync, and eieio to order storage accesses can be found in Appendix B, "Programming Examples for Sharing Storage" on page 39.

Because the storage model is weakly consistent, the sequential execution model as applied instructions that cause storage accesses guarantees only that those accesses appear to be performed in program order with respect to the processor executing the instructions. For example, an instruction may complete, and subsequent instructions may be executed, before storage accesses caused by the first instruction have been performed. However, for a sequence of atomic accesses to the same storage location, if the location is in storage that is Memory Coherence Required the definition of coherence guarantees that the accesses are performed in program order with respect to any processor or mechanism that accesses the location coherently, and similarly if the location is in storage that is Caching Inhibited.

Because accesses to storage that is Caching Inhibited are performed in main storage, memory barriers and dependencies on Load instructions order such accesses with respect to any processor or mechanism even if the storage is not Memory Coherence Required.

#### **Programming Note**

The first example below illustrates cumulative ordering of storage accesses preceding a memory barrier, and the second illustrates cumulative ordering of storage accesses following a memory barrier. Assume that locations X, Y, and Z initially contain the value 0.

#### Example 1:

Processor A: stores the value 1 to location X

Processor B: loads from location X obtaining the

value 1, executes a **sync** instruction, then stores the value 2 to

location Y

Processor C: loads from location Y obtaining the

value 2, executes a **sync** instruction, then loads from location X

#### Example 2:

Processor A: stores the value 1 to location X,

executes a **sync** instruction, then stores the value 2 to location Y

Processor B: loops loading from location Y until

the value 2 is obtained, then stores

the value 3 to location Z

Processor C: loads from location Z obtaining the value 3, executes a **sync** instruc-

tion, then loads from location X

In both cases, cumulative ordering dictates that the value loaded from location X by processor C is 1.

## 1.7.2 Storage Ordering of I/O Accesses

A "coherence domain" consists of all processors and all interfaces to main storage. Memory reads and writes initiated by mechanisms outside the coherence domain are performed within the coherence domain in the order in which they enter the coherence domain and are performed as coherent accesses.

## 1.7.3 Atomic Update

The Load And Reserve and Store Conditional instructions together permit atomic update of a storage location. There are word and doubleword forms of each of these instructions. Described here is the operation of the word forms *lwarx* and *stwcx.*; operation of the doubleword forms *ldarx* and *stdcx.* is the same except for obvious substitutions.

The *Iwarx* instruction is a load from a word-aligned location that has two side effects. Both of these side effects occur at the same time that the load is performed.

- A reservation for a subsequent stwcx. instruction is created.

- The storage coherence mechanism is notified that a reservation exists for the storage location specified by the *Iwarx*.

The **stwcx.** instruction is a store to a word-aligned location that is conditioned on the existence of the reservation created by the **Iwarx** and on whether the same storage location is specified by both instructions. To emulate an atomic operation with these instructions, it is necessary that both the **Iwarx** and the **stwcx.** specify the same storage location.

A **stwcx.** performs a store to the target storage location only if the storage location specified by the **Iwarx** that established the reservation has not been stored into by another processor or mechanism since the reservation was created. If the storage locations specified by the two instructions differ, the store is not necessarily performed.

A stwcx. that performs its store is said to "succeed".

Examples of the use of *Iwarx* and *stwcx*. are given in Appendix B, "Programming Examples for Sharing Storage" on page 39.

A successful **stwcx.** to a given location may complete before its store has been performed with respect to other processors and mechanisms. As a result, a subsequent load or **Iwarx** from the given location by another processor may return a "stale" value. However, a subsequent **Iwarx** from the given location by the other processor followed by a successful **stwcx.** by that processor is guaranteed to have returned the value stored by the first processor's **stwcx.** (in the absence of other stores to the given location).

#### Programming Note —

The store caused by a successful **stwcx**. is ordered, by a dependence on the reservation, with respect to the load caused by the **lwarx** that established the reservation, such that the two storage accesses are performed in program order with respect to any processor or mechanism.

#### 1.7.3.1 Reservations

The ability to emulate an atomic operation using *lwarx* and *stwcx*. is based on the conditional behavior of *stwcx*., the reservation created by *lwarx*, and the clearing of that reservation if the target location is modified by another processor or mechanism before the *stwcx*. performs its store.

A reservation is held on an aligned unit of real storage called a *reservation granule*. The size of the reservation granule is 2<sup>n</sup> bytes, where n is implemen-

tation-dependent but is always at least 4 (thus the minimum reservation granule size is a quadword). The reservation granule associated with effective address EA contains the real address to which EA maps. ("real\_addr(EA)" in the RTL for the Load And Reserve and Store Conditional instructions stands for "real address to which EA maps".)

A processor has at most one reservation at any time. A reservation is established by executing a *lwarx* or Idarx instruction, and is lost (or may be lost, in the case of the fourth bullet) if any of the following occur.

- The processor holding the reservation executes another Iwarx or Idarx: this clears the first reservation and establishes a new one.

- The processor holding the reservation executes any stwcx. or stdcx., regardless of whether the specified address matches the address specified by the Iwarx or Idarx that established the reservation.

- Some other processor executes a Store or dcbz to the same reservation granule, or modifies a Reference or Change bit (see Book III, PowerPC Operating Environment Architecture) in the same reservation granule.

- Some other processor executes a dcbtst, dcbst, or dcbf to the same reservation granule: whether the reservation is lost is undefined.

- Some other mechanism modifies a storage location in the same reservation granule.

Interrupts (see Book III, PowerPC Operating Environment Architecture) do not clear reservations (however, system software invoked by interrupts may clear reservations).

#### Programming Note -

One use of Iwarx and stwcx. is to emulate a "Compare and Swap" primitive like that provided by the IBM System/370 Compare and Swap instruction; see Section B.1, "Atomic Update A System/370-style Primitives" on page 39. Compare and Swap checks only that the old and current values of the word being tested are equal, with the result that programs that use such a Compare and Swap to control a shared resource can err if the word has been modified and the old value subsequently restored. The combination of Iwarx and stwcx. improves on such a Compare and Swap, because the reservation reliably binds the Iwarx and stwcx. together. The reservation is always lost if the word is modified by another processor or mechanism between the Iwarx and stwcx., so the stwcx. never succeeds unless the word has not been stored into (by another processor or mechanism) since the Iwarx.

#### Programming Note -

Warning: The architecture is likely to be changed in the future to permit the reservation to be lost if a dcbf instruction is executed on the processor holding the reservation. Therefore dcbf instructions should not be placed between a Load And Reserve instruction and the subsequent Store Conditional instruction.

#### Programming Note

In general, programming conventions must ensure that Iwarx and stwcx. specify addresses that match; a stwcx. should be paired with a specific Iwarx to the same storage location. Situations in which a stwcx. may erroneously be issued after some Iwarx other than that with which it is intended to be paired must be scrupulously avoided. For example, there must not be a context switch in which the processor holds a reservation in behalf of the old context, and the new context resumes after a Iwarx and before the paired stwcx. The stwcx. in the new context might succeed, which is not what was intended by the programmer. Such a situation must be prevented by executing a stwcx. or stdcx. that specifies a dummy writable aligned location as part of the context switch; see the section entitled "Interrupt Processing" in Book III.

#### Programming Note

Because the reservation is lost if another processor stores anywhere in the reservation granule, lock words (or doublewords) should be allocated such that few such stores occur, other than perhaps to the lock word itself. (Stores by other processors to the lock word result from contention for the lock, and are an expected consequence of using locks to control access to shared storage; stores to other locations in the reservation granule can cause needless reservation loss.) Such allocation can most easily be accomplished by allocating an entire reservation granule for the lock and wasting all but one word. Because resgranule ervation size is implementation-dependent, portable code must do such allocation dynamically.

Similar considerations apply to other data that are shared directly using Iwarx and stwcx. (e.g., pointers in certain linked lists; see Section B.3, "List Insertion" on page 43).

#### 1.7.3.2 Forward Progress

Forward progress in loops that use *Iwarx* and *stwcx*. is achieved by a cooperative effort among hardware, system software, and application software.

The architecture guarantees that when a processor executes a *Iwarx* to obtain a reservation for location X and then a *stwcx*. to store a value to location X, either

- the stwcx. succeeds and the value is written to location X, or

- the stwcx. fails because some other processor or mechanism modified location X, or

- 3. the **stwcx**. fails because the processor's reservation was lost for some other reason.

In Cases 1 and 2, the system as a whole makes progress in the sense that some processor successfully modifies location X. Case 3 covers reservation loss required for correct operation of the rest of the system. This includes cancellation caused by some other processor writing elsewhere in the reservation granule for X, as well as cancellation caused by the operating system in managing certain limited resources such as real storage. It may also include implementation-dependent causes of reservation loss.

An implementation may make a forward progress guarantee, defining the conditions under which the system as a whole makes progress. Such a guarantee must specify the possible causes of reservation loss in Case 3. While the architecture alone cannot provide such a guarantee, the characteristics listed in Cases 1 and 2 are necessary conditions for any forward progress guarantee. An implementation and operating system can build on them to provide such a guarantee.

#### Programming Note -

The architecture does not include a "fairness guarantee". In competing for a reservation, two processors can indefinitely lock out a third.

## 1.8 Instruction Storage

The instruction execution properties and requirements described in this section, including its subsections, apply only to instruction execution that is required by the sequential execution model.

In this section, including its subsections, it is assumed that all instructions for which execution is attempted are in storage that is not Caching Inhibited and (unless instruction address translation is disabled; see Book III) is not Guarded, and from which instruction fetching does not cause the system error handler to be invoked (e.g., from which instruction fetching is not prohibited by the "address translation mechanism" or the "storage protection mechanism"; see Book III).

#### Programming Note -

The results of attempting to execute instructions from storage that does not satisfy this assumption are described in Sections 1.6.2 and 1.6.4 of this Book and in Book III.

For each instance of executing an instruction from location X, the instruction may be fetched multiple times.

The instruction cache is not necessarily kept consistent with the data cache or with main storage. It is the responsibility of software to ensure that instruction storage is consistent with data storage when such consistency is required for program correctness. After one or more bytes of a storage location have been modified and before an instruction located in that storage location is executed, software must execute the appropriate sequence of instructions to make instruction storage consistent with data storage. Otherwise the result of attempting to execute the instruction is boundedly undefined except as described in Section 1.8.1, "Concurrent Modification and Execution of Instructions" on page 12.

#### - Programming Note

Following are examples of how to make instruction storage consistent with data storage. Because the optimal instruction sequence to make instruction storage consistent with data storage may vary between systems, many operating systems will provide a system service to perform this function.

Case 1: The program has a single thread.

Assume that location X previously contained the instruction A0; the program modified one of more bytes of that location such that, in data storage, the location contains the instruction A1; and location X is wholly contained in a single cache block. The following instruction sequence will make instruction storage consistent with data storage such that if the *isync* was in location X-4, the instruction A1 in location X would be executed immediately after the *isync*.

```

dcbst X  #copy the block to main storage

sync  #order copy before invalidation

icbi X  #invalidate copy in instr cache

isync  #discard prefetched instructions

```

Case 2: The program has two or more threads.

Assume thread A has modified the instruction at location X and other threads are waiting for thread A to signal that the new instruction is ready to execute. The following instruction sequence will make instruction storage consistent with data storage and then set a flag to indicate to the waiting threads that the new instruction can be executed.

```

dcbst X  #copy the block in main storage

sync  #order copy before invalidation

icbi X  #invalidate copy in instr cache

sync  #order invalidation before store

# to flag

stw r0,flag(3) #set flag indicating instruction

# storage is now consistent

```

The following instruction sequence, executed by the waiting threads, will prevent the waiting threads from executing the instruction at location X until location X in instruction storage is consistent with data storage, and then will cause any prefetched instructions to be discarded.

In the preceding instruction sequence any context synchronizing instruction (e.g., *rfid*) can be used instead of *isync*. (For Case 1 only *isync* can be used.)

For both cases, if two or more instructions in separate data cache blocks have been modified, the *dcbst* instruction in the examples must be replaced by a sequence of *dcbst* instructions such that each block containing the modified instructions is copied back to main storage. Similarly, for *icbi* the sequence must invalidate each instruction cache block containing a location of an instruction that was modified. The *sync* instruction that appears above between "*dcbst* X" and "*icbi* X" would be placed between the sequence of *dcbst* instructions and the sequence of *icbi* instructions.

### 1.8.1 Concurrent Modification and **Execution of Instructions**

The phrase "concurrent modification and execution of instructions" (CMODX) refers to the case in which a processor fetches and executes an instruction from instruction storage which is not consistent with data storage or which becomes inconsistent with data storage prior to the completion of its processing. This section describes the only case in which executing this instruction under these conditions produces defined results.

In the remainder of this section the following terminology is used.

- Location X is an arbitrary word-aligned storage location.

- $\blacksquare$  X<sub>0</sub> is the value of the contents of location X for which software has made the location X in instruction storage consistent with data storage.

- $\blacksquare$   $X_1$ ,  $X_2$ , ...,  $X_n$  are the sequence of the first n values occupying location X after X<sub>0</sub>.

- $X_n$  is the first value of X subsequent to  $X_0$  for which software has again made instruction storage consistent with data storage.

- The "patch class" of instructions consists of the I-form Branch instruction (b[I][a]) and the preferred no-op instruction (ori 0,0,0).

If the instruction from location X is executed after the copy of location X in instruction storage is made consistent for the value X<sub>0</sub> and before it is made consistent for the value  $X_n$ , the results of executing the instruction are defined if and only if the following conditions are satisfied.

- 1. The stores that place the values  $X_1$ , ...,  $X_n$  into location X are atomic stores that modify all four bytes of location X.

- 2. Each  $X_i$ ,  $0 \le i \le n$ , is a patch class instruction.

- 3. Location X is in storage that is Memory Coherence Required.

If these conditions are satisfied, the result of each execution of an instruction from location X will be the execution of some  $X_i$ ,  $0 \le i \le n$ . The value of the ordinate i associated with each value executed may be different and the sequence of ordinates i associated with a sequence of values executed is not constrained, (e.g., a valid sequence of executions of the instruction at location X could be the sequence Xi,  $X_{i+2}$ , then  $X_{i-1}$ ). If these conditions are not satisfied, the results of each such execution of an instruction from location X are boundedly undefined, and may

include causing inconsistent information to be presented to the system error handler.

#### **Programming Note -**

An example of how failure to satisfy the requirements given above can cause inconsistent information to be presented to the system error handler is as follows. If the value  $X_0$  (an illegal instruction) is executed, causing the system illegal instruction handler to be invoked, and before the error handler can load  $X_0$  into a register,  $X_0$  is replaced with X<sub>1</sub>, an Add Immediate instruction, it will appear that a legal instruction caused an illegal instruction exception.

#### Programming Note -

It is possible to apply a patch or to instrument a given program without the need to suspend or halt the program. This can be accomplished by modifying the example shown above where one thread is creating instructions to be executed by one or more other threads.

In place of the Store to a flag to indicate to the other threads that the code is ready to be executed, the program that is applying the patch would replace a patch class instruction in the original program with a Branch instruction that would cause any thread executing the Branch to branch to the newly created code. The first instruction in the newly created code must be an isync, which will cause any prefetched instructions to be discarded, ensuring that the execution is consistent with the newly created code. instruction storage location containing the isync instruction in the patch area must be consistent with data storage with respect to the processor that will execute the patched code before the Store which stores the new Branch instruction is performed.

#### Programming Note -

It is believed that all processors that comply with versions of the architecture that precede Version 2.01 support concurrent modification and execution of instructions as described in this section if the requirements given above are satisfied, and that most such processors yield boundedly undefined results if the requirements given above are not satisfied. However, in general such support has not been verified by processor testing. Also, one such processor is known to yield undefined results in certain cases if the requirements given above are not satisfied.

## Chapter 2. Effect of Operand Placement on Performance

The placement (location and alignment) of operands in storage affects relative performance of storage accesses, and may affect it significantly. The best performance is guaranteed if storage operands are aligned. In order to obtain the best performance across the widest range of implementations, the programmer should assume the performance model described in Figure 1 with respect to the placement of storage operands. Performance of accesses varies depending on the following:

- 1. Operand Size

- 2. Operand Alignment

- 3. Crossing no boundary

- 4. Crossing a cache block boundary

- 5. Crossing a virtual page boundary

- Crossing a segment boundary (see Book III, *PowerPC Operating Environment Architecture* for a description of storage segments)

The *Move Assist* instructions have no alignment requirements.

| Operand      |                | Boundary Crossing       |                   |                              |                   |

|--------------|----------------|-------------------------|-------------------|------------------------------|-------------------|

| Size         | Byte<br>Align. | None                    | Cache<br>Block    | Virtual<br>Page <sup>2</sup> | Seg.              |

| Inte         | Integer        |                         |                   |                              |                   |

| 8 Byte       | 8<br>4<br>< 4  | optimal<br>good<br>good | –<br>good<br>good | -<br>good<br>good            | –<br>poor<br>poor |

| 4 Byte       | 4 < 4          | optimal<br>good         | –<br>good         | -<br>good                    | –<br>poor         |

| 2 Byte       | 2 < 2          | optimal<br>good         | _<br>good         | -<br>good                    | –<br>poor         |

| 1 Byte       | 1              | optimal                 | -                 | _                            | _                 |

| lmw,<br>stmw | 4 < 4          | good<br>poor            | good<br>poor      | good<br>poor                 | poor<br>poor      |

| string       |                | good                    | good              | good                         | poor              |

| Flo          | at             |                         |                   |                              |                   |

| 8 Byte       | 8<br>4<br>< 4  | optimal<br>good<br>poor | –<br>good<br>poor | –<br>poor<br>poor            | –<br>poor<br>poor |

| 4 Byte       | 4 < 4          | optimal<br>poor         | –<br>poor         | poor                         | –<br>poor         |

If an instruction causes an access that is not atomic and any portion of the operand is in storage that is Write Through Required or Caching Inhibited, performance is likely to be poor.

Figure 1. Performance effects of storage operand placement

If the storage operand spans two virtual pages that have different storage control attributes, performance is likely to be poor.

### 2.1 Instruction Restart

In this section, "Load instruction" includes the Cache Management and other instructions that are stated in the instruction descriptions to be "treated as a Load", and similarly for "Store instruction".

The following instructions are never restarted after having accessed any portion of the storage operand (unless the instruction causes a "Data Address Compare match" or a "Data Address Breakpoint match", for which the corresponding rules are given in Book III).

- 1. A Store instruction that causes an atomic access

- 2. A Load instruction that causes an atomic access to storage that is both Caching Inhibited and Guarded

Any other Load or Store instruction may be partially executed and then aborted after having accessed a portion of the storage operand, and then re-executed (i.e., restarted, by the processor or the operating system). If an instruction is partially executed, the contents of registers are preserved to the extent that the correct result will be produced when the instruction is re-executed.

#### **Programming Note**

There are many events that might cause a Load or Store instruction to be restarted. For example, a hardware error may cause execution of the instruction to be aborted after part of the access has been performed, and the recovery operation could then cause the aborted instruction to be reexecuted.

When an instruction is aborted after being partially executed, the contents of the instruction pointer indicate that the instruction has not been executed, however, the contents of some registers may have been altered and some bytes within the storage operand may have been accessed. The following are examples of an instruction being partially executed and altering the program state even though it appears that the instruction has not been executed.

- 1. Load Multiple, Load String: Some registers in the range of registers to be loaded may have been altered.

- 2. Any Store instruction, dcbz: Some bytes of the storage operand may have been altered.

- 3. Any floating-point Load instruction: target register (FRT) may have been altered.

## **Chapter 3. Storage Control Instructions**

| 3.1 Parameters Useful to Application   | 3.3 Synchronization Instructions 2          |

|----------------------------------------|---------------------------------------------|

| Programs                               | 3.3.1 Instruction Synchronize Instruction 2 |

| 3.2 Cache Management Instructions . 16 | 3.3.2 Load And Reserve and Store            |

| 3.2.1 Instruction Cache Instruction 17 | Conditional Instructions                    |

| 3.2.2 Data Cache Instructions 18       | 3.3.3 Memory Barrier Instructions 25        |

## 3.1 Parameters Useful to Application Programs

It is suggested that the operating system provide a service that allows an application program to obtain the following information.

- 1. The two virtual page sizes

- 2. Coherence block size

- 3. Granule sizes for reservations

- 4. An indication of the cache model implemented (e.g., Harvard-style cache, combined cache)

- 5. Instruction cache size

- 6. Data cache size

- 7. Instruction cache line size (see Book IV, *PowerPC Implementation Features*)

- 8. Data cache line size (see Book IV)

- 9. Block size for icbi

- 10. Block size for dcbt and dcbtst

- 11. Block size for dcbz, dcbst, and dcbf

- 12. Instruction cache associativity

- 13. Data cache associativity

- 14. Factors for converting the Time Base to seconds

If the caches are combined, the same value should be given for an instruction cache attribute and the corresponding data cache attribute.

## 3.2 Cache Management Instructions

The Cache Management instructions obey the sequential execution model except as described in Section 3.2.1, "Instruction Cache Instruction" on page 17.

In the instruction descriptions the statements "this instruction is treated as a Load" and "this instruction is treated as a Store" mean that the instruction is

treated as a Load (Store) from (to) the addressed byte with respect to address translation, the definition of program order on page 1, storage protection, reference and change recording, and the storage access ordering described in Section 1.7.1, "Storage Access Ordering" on page 6.

#### 3.2.1 Instruction Cache Instruction

#### Instruction Cache Block Invalidate X-form

icbi RA,RB

| 31 | /// | RA | RB | 982 | /  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

If the block containing the byte addressed by EA is in storage that is Memory Coherence Required and a block containing the byte addressed by EA is in the instruction cache of any processors, the block is invalidated in those instruction caches.

If the block containing the byte addressed by EA is in storage that is not Memory Coherence Required and a block containing the byte addressed by EA is in the instruction cache of this processor, the block is invalidated in that instruction cache.

The function of this instruction is independent of whether the block containing the byte addressed by EA is in storage that is Write Through Required or Caching Inhibited.

This instruction is treated as a *Load* (see Section 3.2), except that reference and change recording need not be done.

#### Special Registers Altered:

None

#### **Programming Note**

As stated above, the effective address is translated using translation resources used for data accesses, even though the block being invalidated was copied into the instruction cache based on translation resources used for instruction fetches (see Book III, *PowerPC Operating Environment Architecture*).

#### **Programming Note** -

The invalidation of the specified instruction cache block cannot be assumed to have been performed with respect to the processor executing the instruction until a subsequent *isync* instruction has been executed by the processor. No other instruction or event has the corresponding effect.

#### 3.2.2 Data Cache Instructions

#### Data Cache Block Touch X-form

#### dcbt RA,RB

| 31 | /// | RA | RB | 278 | /  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

The dcbt instruction provides a hint that the program will probably soon load from the block containing the byte addressed by EA. The hint is ignored if the block is Caching Inhibited or Guarded.

The actions (if any) taken by the processor in response to the hint are not considered to be "caused by" or "associated with" the dcbt instruction (e.g., dcbt is considered not to cause any data accesses). No means are provided by which software can synchronize these actions with the execution of the instruction stream. For example, these actions are not ordered by memory barriers.

This instruction is treated as a *Load* (see Section 3.2), except that the system data storage error handler is not invoked, and reference and change recording need not be done.

#### Special Registers Altered:

None

#### Programming Note -

In response to the hint provided by dcbt and dcbtst, the processor may prefetch the specified block into the data cache, or take other actions that reduce the latency of subsequent Load or Store instructions that refer to the block.

Earlier implementations do not necessarily ignore the hint provided by dcbt and dcbtst if the specified block is in storage that is Guarded and not Caching Inhibited. Therefore a dcbt or dcbtst instruction should not specify an EA in such storage if the program is to be run on such implementations.

#### Data Cache Block Touch for Store X-form

dcbtst RA,RB

| 31 | /// | RA | RB | 246 | /  |

|----|-----|----|----|-----|----|

| 0  | 6   | 11 | 16 | 21  | 31 |

Let the effective address (EA) he the (RA|0)+(RB).

The dcbtst instruction provides a hint that the program will probably soon store to the block containing the byte addressed by EA. The hint is ignored if the block is Caching Inhibited or Guarded.

The actions (if any) taken by the processor in response to the hint are not considered to be "caused by" or "associated with" the dcbtst instruction (e.g., dcbtst is considered not to cause any data accesses). No means are provided by which software can synchronize these actions with the execution of the instruction stream. For example, these actions are not ordered by memory barriers.

This instruction is treated as a Load (see Section 3.2), except that the system data storage error handler is not invoked, and reference and change recording need not be done.

#### Special Registers Altered:

None

#### Data Cache Block set to Zero X-form

dcbz RA,RB [POWER mnemonic: dclz]

| 31 | /// | RA | RB | 1014 | /  |

|----|-----|----|----|------|----|

| 0  | 6   | 11 | 16 | 21   | 31 |

```

if RA = 0 then b \leftarrow 0 else b \leftarrow (RA) EA \leftarrow b + (RB) n \leftarrow block size (bytes) m \leftarrow log<sub>2</sub>(n) ea \leftarrow EA<sub>0:63-m</sub> || m<sub>0</sub> MEM(ea, n) \leftarrow nox00

```

Let the effective address (EA) be the sum (RA|0)+(RB).

All bytes in the block containing the byte addressed by EA are set to zero.

This instruction is treated as a Store (see Section 3.2).

#### Special Registers Altered:

None

#### - Programming Note -

**dcbz** does not cause the block to exist in the data cache if the block is in storage that is Caching Inhibited.

For storage that is neither Write Through Required nor Caching Inhibited, *dcbz* provides an efficient means of setting blocks of storage to zero. It can be used to initialize large areas of such storage, in a manner that is likely to consume less memory bandwidth than an equivalent sequence of *Store* instructions.

For storage that is either Write Through Required or Caching Inhibited, *dcbz* is likely to take significantly longer to execute than an equivalent sequence of *Store* instructions.

See the section entitled "Cache Management Instructions" in Book III, *PowerPC Operating Environment Architecture* for additional information about *dcbz*.

#### Data Cache Block Store X-form

dcbst RA,RB

| 31 | /// | RA | RB | 54 | /  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the sum (RA|0)+(RB).

If the block containing the byte addressed by EA is in storage that is Memory Coherence Required and a block containing the byte addressed by EA is in the data cache of any processor and any locations in the block are considered to be modified there, those locations are written to main storage, additional locations in the block may be written to main storage, and the block ceases to be considered to be modified in that data cache.

If the block containing the byte addressed by EA is in storage that is not Memory Coherence Required and a block containing the byte addressed by EA is in the data cache of this processor and any locations in the block are considered to be modified there, those locations are written to main storage, additional locations in the block may be written to main storage, and the block ceases to be considered to be modified in that data cache.

The function of this instruction is independent of whether the block containing the byte addressed by EA is in storage that is Write Through Required or Caching Inhibited.

This instruction is treated as a *Load* (see Section 3.2), except that reference and change recording need not be done.

#### Special Registers Altered:

None

#### Data Cache Block Flush X-form

dcbf RA,RB

| 31 | /// | RA | RB | 86 | /  |

|----|-----|----|----|----|----|

| 0  | 6   | 11 | 16 | 21 | 31 |

Let the effective address (EA) be the (RA|0)+(RB).

If the block containing the byte addressed by EA is in storage that is Memory Coherence Required and a block containing the byte addressed by EA is in the data cache of any processor and any locations in the block are considered to be modified there, those locations are written to main storage and additional locations in the block may be written to main storage. The block is invalidated in the data caches of all processors.

If the block containing the byte addressed by EA is in storage that is not Memory Coherence Required and a block containing the byte addressed by EA is in the data cache of this processor and any locations in the block are considered to be modified there, those locations are written to main storage and additional locations in the block may be written to main storage. The block is invalidated in the data cache of this processor.

The function of this instruction is independent of whether the block containing the byte addressed by EA is in storage that is Write Through Required or Caching Inhibited.

This instruction is treated as a Load (see Section 3.2), except that reference and change recording need not be done.

#### Special Registers Altered:

None

#### - Programming Note -

The requirements of the sequential execution model combine with the treatment of dcbf as a Load to ensure that the operation caused by a dcbf instruction is performed (i.e., complete) with respect to a subsequent Load instruction (in the same execution thread) that specifies a storage location in the cache block specified by the dcbf instruction.

## 3.3 Synchronization Instructions

## 3.3.1 Instruction Synchronize Instruction

### Instruction Synchronize XL-form

isync

[POWER mnemonic: ics]

| 19 | /// | /// | /// | 150 | /  |

|----|-----|-----|-----|-----|----|

| 0  | 6   | 11  | 16  | 21  | 31 |

Executing an isync instruction ensures that all instructions preceding the isync instruction have completed before the isync instruction completes, and that no subsequent instructions are initiated until after the isync instruction completes. It also ensures that all instruction cache block invalidations caused by icbi instructions preceding the isync instruction have been performed with respect to the processor executing the isync instruction, and then causes any prefetched instructions to be discarded.

Except as described in the preceding sentence, the isync instruction may complete before storage accesses associated with instructions preceding the isync instruction have been performed.

This instruction is context synchronizing (see Book III, PowerPC Operating Environment Architecture).

#### Special Registers Altered:

None

#### 3.3.2 Load And Reserve and Store Conditional Instructions

The Load And Reserve and Store Conditional instructions can be used to construct a sequence of instructions that appears to perform an atomic update operation on an aligned storage location. See Section 1.7.3, "Atomic Update" on page 8 for additional information about these instructions.

The Load And Reserve and Store Conditional instructions are fixed-point Storage instructions; see the section entitled "Fixed-Point Storage Access Instructions" in Book I, PowerPC User Instruction Set Architecture.

The storage location specified by the Load And Reserve and Store Conditional instructions must be in storage that is Memory Coherence Required if the location may be modified by other processors or mechanisms. If the specified location is in storage that is Write Through Required or Caching Inhibited, the system data storage error handler or the system alignment error handler is invoked.

#### **Programming Note** -

The Memory Coherence Required attribute on other processors and mechanisms ensures that their stores to the reservation granule will cause the reservation created by the Load And Reserve instruction to be lost.

#### Programming Note

Because the Load And Reserve and Store Conditional instructions have implementation dependencies (e.g., the granularity at which reservations are managed), they must be used with care. The operating system should provide system library programs that use these instructions to implement the high-level synchronization functions (Test and Set, Compare and Swap, locking, etc.; see Appendix B) that are needed by application programs. Application programs should use these library programs, rather than use the Load And Reserve and Store Conditional instructions directly.

# Load Word And Reserve Indexed X-form

Iwarx RT,RA,RB

| 31 | RT | RA | RB | 20 | /  |

|----|----|----|----|----|----|

| 0  | 6  | 11 | 16 | 21 | 31 |

```

if RA = 0 then b \leftarrow 0

else b \leftarrow (RA)

EA \leftarrow b + (RB)

RESERVE \leftarrow 1

RESERVE ADDR \leftarrow real_addr(EA)

RT \leftarrow 320 || MEM(EA, \leftarrow4)

```

Let the effective address (EA) be the sum (RA|0)+(RB). The word in storage addressed by EA is loaded into  $RT_{32:63}$ .  $RT_{0:31}$  are set to 0.

This instruction creates a reservation for use by a *Store Word Conditional* instruction. An address computed from the EA as described in Section 1.7.3.1 is associated with the reservation, and replaces any address previously associated with the reservation.

EA must be a multiple of 4. If it is not, either the system alignment error handler is invoked or the results are boundedly undefined.

#### Special Registers Altered:

None

# Load Doubleword And Reserve Indexed X-form

Idarx RT,RA,RB