# **Advanced Micro Devices**

# 1985

# **Annual Proceedings**

A Compendium of Technical Articles and Conference Papers

# Advanced Micro Devices 1985 Annual Proceedings

©1985 Advanced Micro Devices, Inc.

901 Thompson Place, P.O. Box 3453, Sunnyvale, California 94088 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

Printed in U.S.A.

ISSN 0883-1262

#### CREDITS

"Denser process gets the most out of bipolar VLSI,"

"Videotex hardware heralds another node-the home,"

"Third-generation codecs pave way for future digital networks,"

"Data-compression IC saves on storage and speeds up image transmission,"

"Protocols and network-control chips: a symbiotic relationship,"

"Protocol standardization works its way up the ladder of the OSI model,"

"New standards for local networks push upper limits for lightwave data,"

copyright 1984, McGraw-Hill Inc. All rights reserved. Reprinted by permission.

"A high performance CMOS process for the next generation EPROM," "Design of a Single-Chip Bell 212A Compatible Modern Employing Digital Signal Processing," copyright 1984 IEEE. All rights reserved. Reprinted by permission.

"Surface Mount Technology, Plastic Chip Carrier Trends" copyright 1984, Lake Publishing Corp. All rights reserved. Reprinted by permission.

"La conception d'une unité centrale microprogrammable" reprinted by permission of Electronique, Techniques et Industries.

"A new concept in backplane communication,"

"Super-minicomputer design using PALs\*" reprinted by permission of Electronic Engineering.

"Putting the speed into 12-bit A-to-D conversion" reprinted by permission of New Electronics.

"Microprogrammable chips blend top performance with 32-bit structures,"

"Bipolar building blocks deliver supermini speed to microcoded systems,"

"Single-chip accelerators speed floating-point and binary computations,"

"One-chip sequencer shapes up addressing for large FFTs,"

"Controller chips pair up in S interface for ISDN systems,"

"Monolithic color palette fills in the picture for high-speed graphics,"

"Three chips, plus palette, aid graphics designers to paint detailed pictures,"

"64-kbit EEPROM speeds in-system reprogramming, adds data polling,"

"Logic-programming language enriches design processes,"

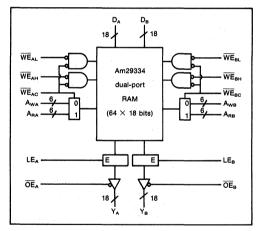

"RAM's on-chip registers build simple control stores that include self-diagnostics," reprinted with permission from *Electronic Design*; copyright Hayden Publishing Co., Inc. 1984.

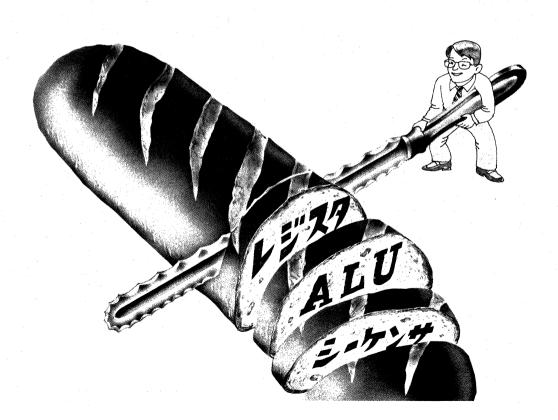

"High-performance, 32-bit building blocks address a broad spectrum of applications" reprinted by permission of Nikkei Electronics.

"Digitale Signalverarbeitung mit bipolaren LSI-Bausteinen" reprinted by permission of Elektronik Industrie.

"500-kHz single-board FFT system incorporates DSP-optimized chips,"

"Design real-time Ethernet systems by giving priority to nodes,"

"Use a CRT-controller chip to mix text and graphics," reprinted with permission from EDN; copyright 1984 Cahners Publishing Co. All rights reserved.

"Very-high-speed floating-point processor,"

"Data security with fast, high-integration circuits" reprinted by permission of Electronica.

"Data encryption: high-speed implementation of DES" reprinted by permission of Communications Engineering International.

"Standardizing upper-level network protocols,"

"Two-chip set tackles disk control problems,"

"Winchester/floppy controller eases disk interfacing," reprinted with permission from Computer Design. Copyright Pennwell Publishing Co., 1984. All rights reserved.

"VLSI and digital networking,"

"DRAM controller helps scrub errors,"

"Resettable RAMs speed cache systems," reprinted with permission. Copyright Hearst Business Communications, 1984. All rights reserved.

"Nuove architetture per accelerare la gestione dei pixel nelle applicazioni grafiche" reprinted by permission of Elettronica Oggi.

"The Role of Programmable Logic in System Design" reprinted with permission from VLSI Design. Copyright CMP Publications 1984. All rights reserved.

"Logik-Baustein kombiniert PAL- und Gate-Array-Technik," reprinted by permission of Elektronik.

"Methode de test et de conception de diagnostic," (parts 1 and 2) reprinted by permission of Minis et Micros.

\*PAL is a registered trademark of and is used under license from Monolithic Memories, Inc.

## ADVANCED MICRO DEVICES 1985 ANNUAL PROCEEDINGS

### A Compendium of Technical Articles and Conference Papers

#### CONTENTS

| Preface                                                                                                                                                                                                                             | vi  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Technology                                                                                                                                                                                                                          |     |

| "Denser process gets the most out of bipolar VLSI," by Phil Downing, Pete Gwozdz, and Bernie New, from <i>Electronics</i> , June 28, 1984. (Am2901, Am29116A, Am29517A)                                                             | 1   |

| "Bipolar and CMOS Technologies Become Partners in Digital Signal Processing," by Robert Perlman, presented at WESCON, October, 1984. (Am29517A, Am29C517, Am29501A)                                                                 | 5   |

| "A high performance CMOS process for the next generation EPROM," by Jih Lien, Steve Longcor, K.Y. Chang,<br>Lewis Shen, Pete Manos, David Chan, Tien Lee, and Sucheta Nallamothu, presented at IEDM, December, 1984.<br>(Am27C1024) | 12  |

| "Surface Mount Technology, Plastic Chip Carrier Trends," by Michael C. Lancaster, from <i>Electri-Onics</i> , December, 1984.                                                                                                       | 16  |

| Bipolar Microprocessors and Peripherals                                                                                                                                                                                             |     |

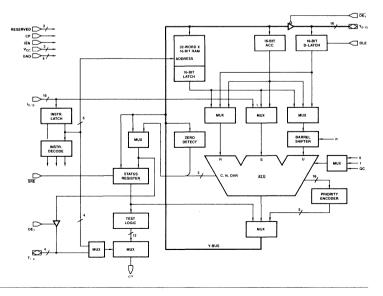

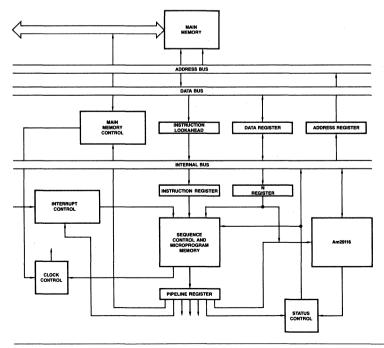

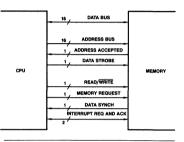

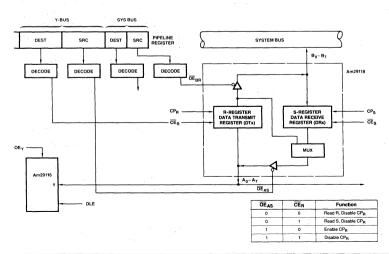

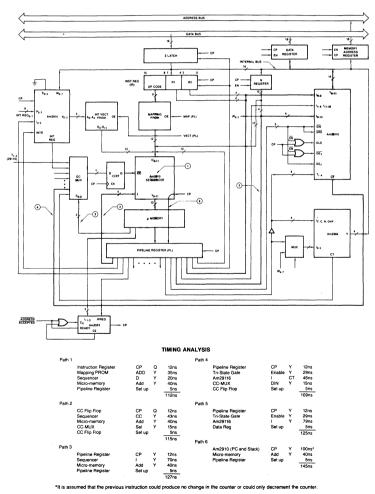

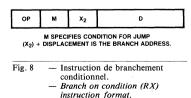

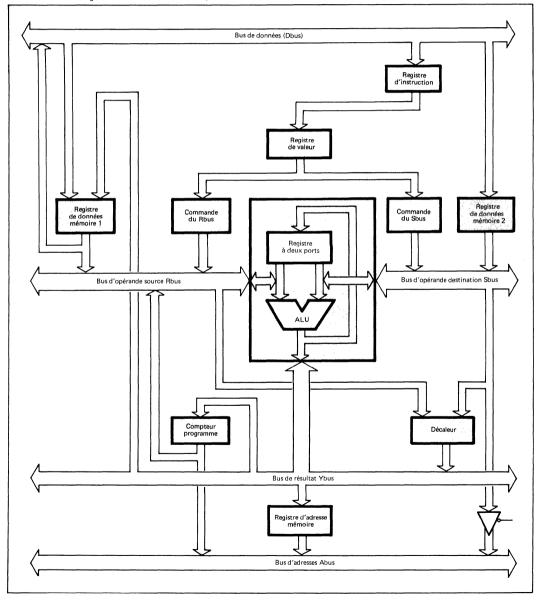

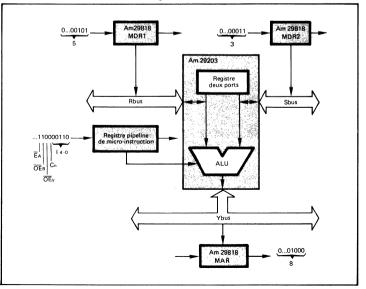

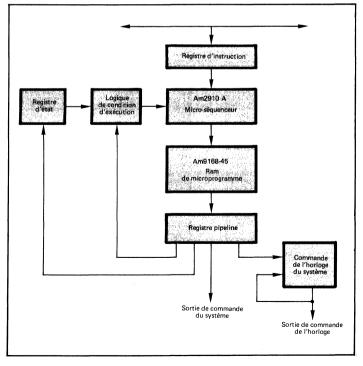

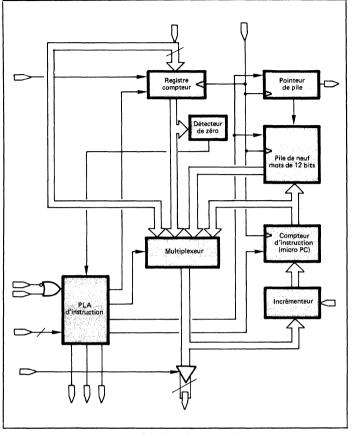

| "La conception d'une unité centrale microprogrammable," by D. Mithani, from <i>Electronique, Techniques et Indus-</i><br>tries, (France) May, 1984. (Am29116, Am2903, Am2910)                                                       | 21  |

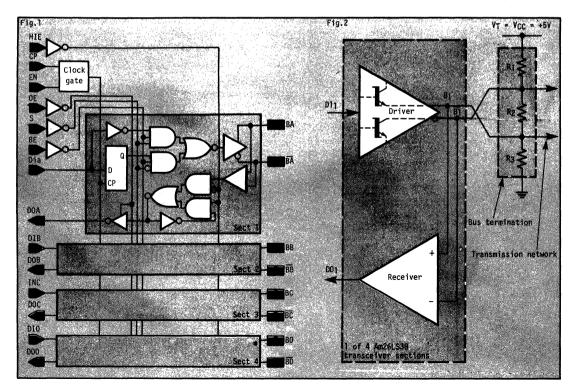

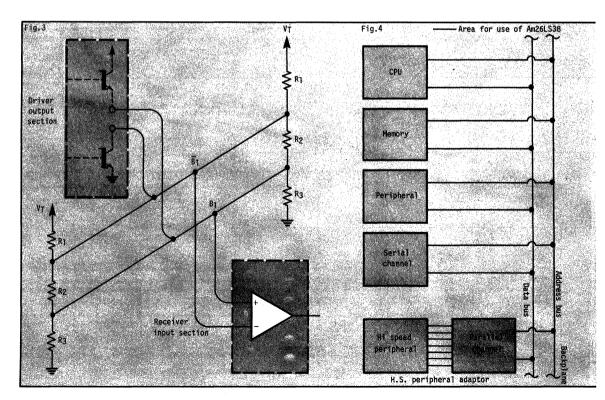

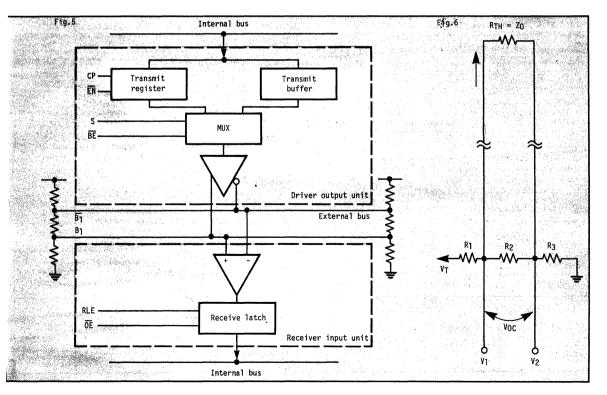

| "A new concept in backplane communication," by Eric Chou and Gary Connor, from <i>Electronic Engineering</i> , (United Kingdom) May, 1984. (Am26LS38)                                                                               | 29  |

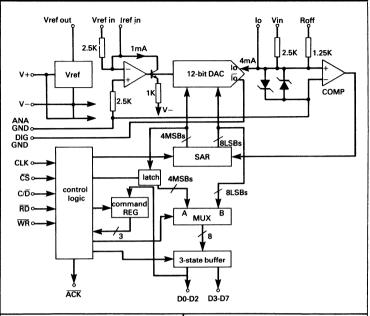

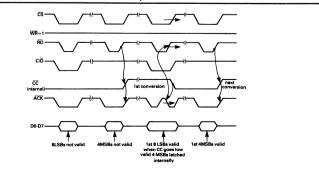

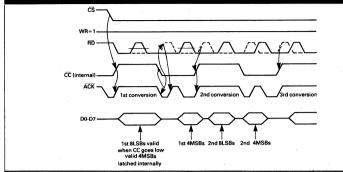

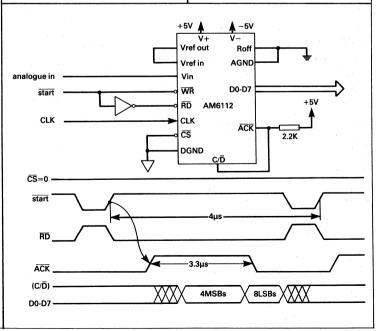

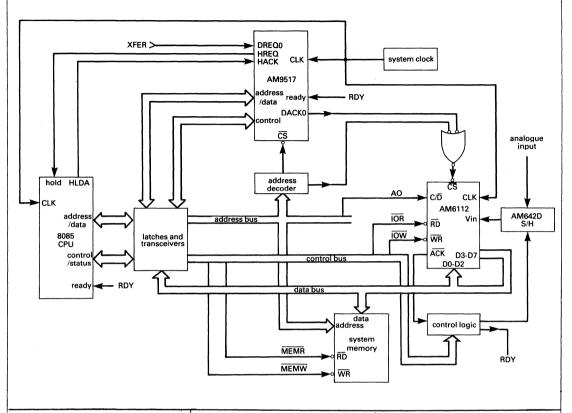

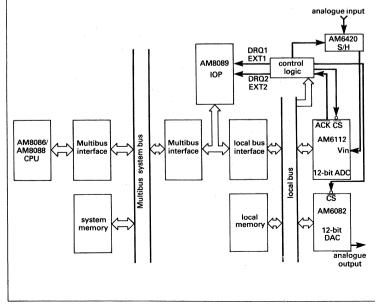

| "Putting the speed into 12-bit A-to-D conversion," by Edgar R. Macachor, from New Electronics, (United Kingdom)<br>June 12, 1984. (Am6112)                                                                                          | 32  |

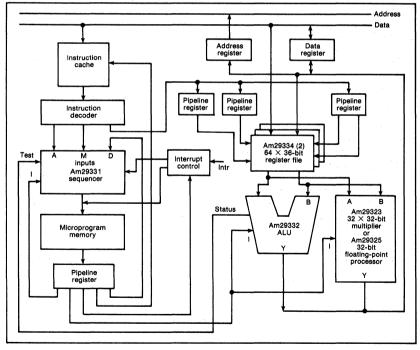

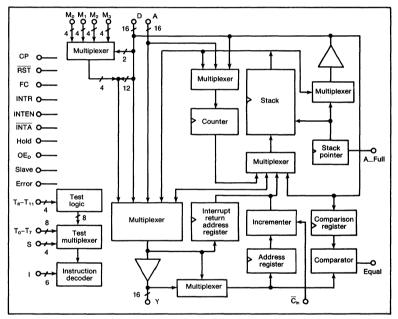

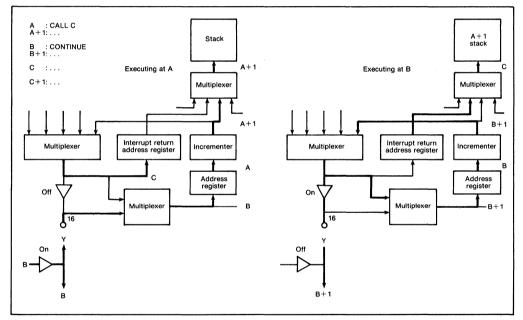

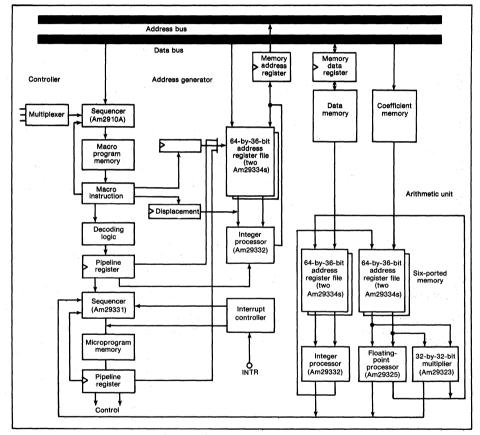

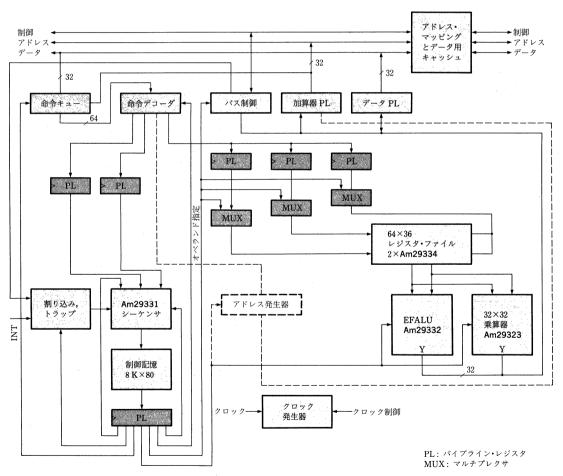

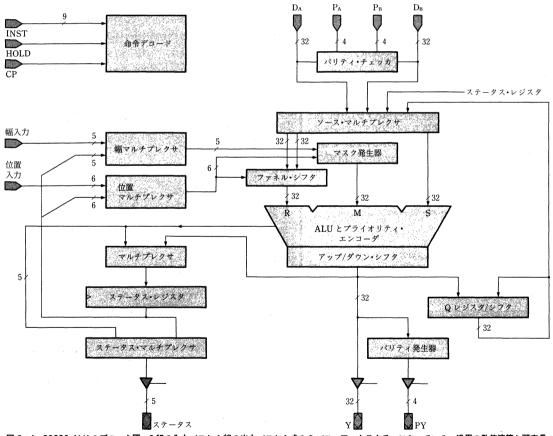

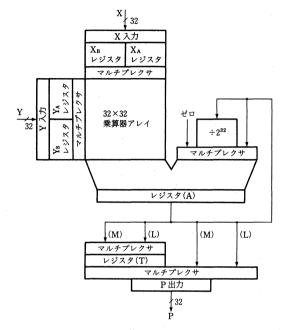

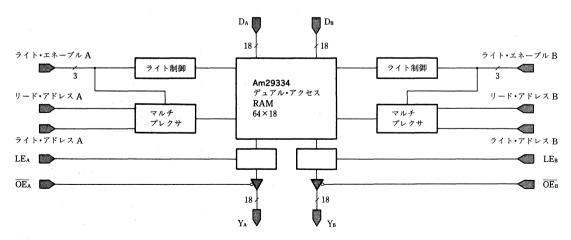

| "Microprogrammable chips blend top performance with 32-bit structures," by Paul Chu and Bernard J. New, from <i>Electronic Design</i> , November 15, 1984. (Am29300 family)                                                         | 37  |

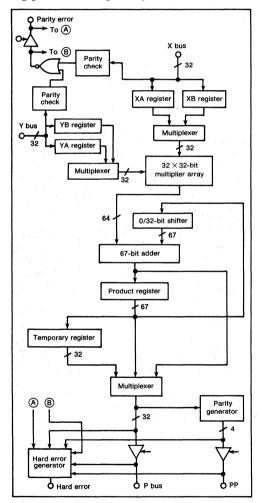

| "Bipolar building blocks deliver supermini speed to microcoded systems," by Dhaval Ajmera, Ole Moller, and David Sorenson, from <i>Electronic Design</i> , November 15, 1984. (Am29300 family)                                      | 38  |

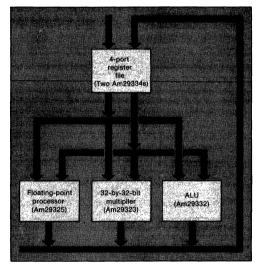

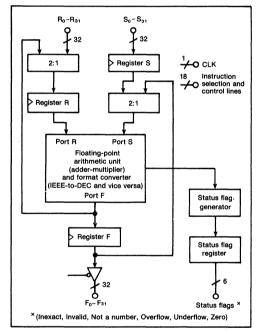

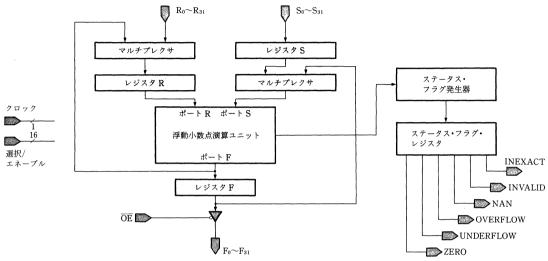

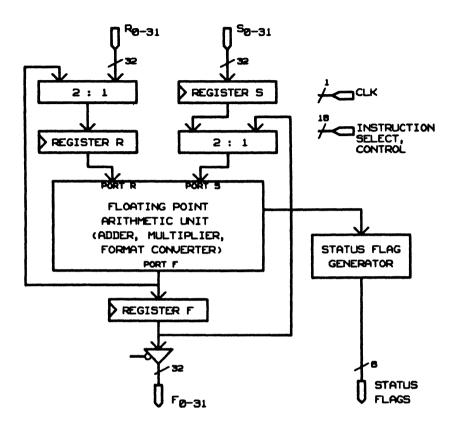

| "Single-chip accelerators speed floating-point and binary computations," by David Quong and Robert Perlman, from<br><i>Electronic Design</i> , November 15, 1984. (Am29300 family)                                                  | 48  |

| "High-performance, 32-bit building blocks address a broad spectrum of applications," by Paul Chu and Bernard J. New, from <i>Nikkei Electronics</i> , (Japan), November 19, 1984. (Am29300 family)                                  | 58  |

| Digital Signal Processing                                                                                                                                                                                                           |     |

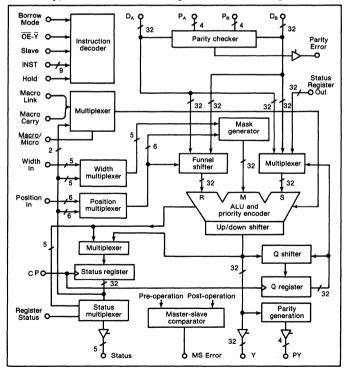

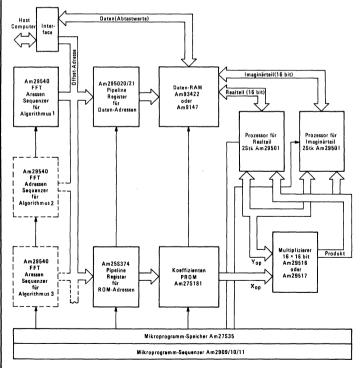

| "Digitale Signalverarbeitung mit bipolaren LSI-Bausteinen," by P. Stuhlmüller and U. Renz, from <i>Elektronik Industrie</i> ,<br>(Germany) May, 1984. (Am29500 family)                                                              | 74  |

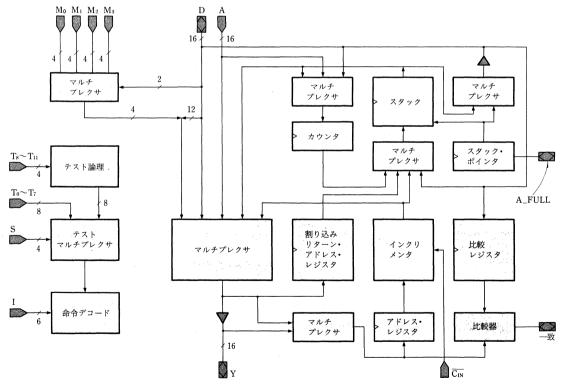

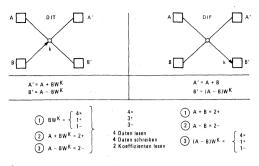

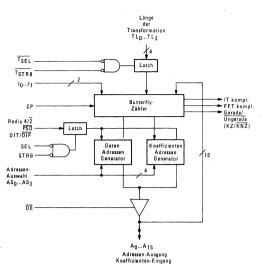

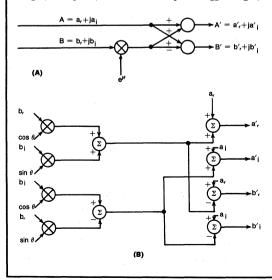

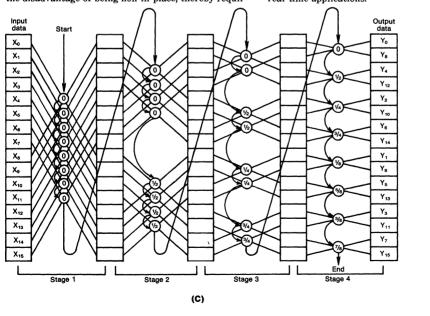

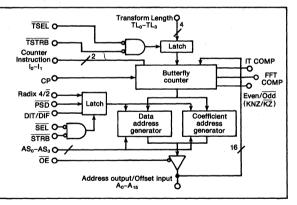

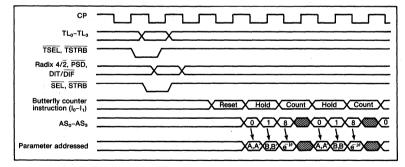

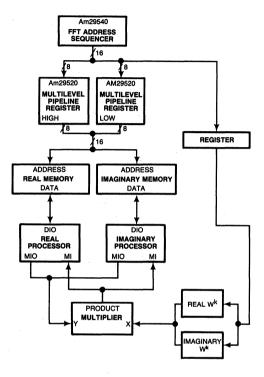

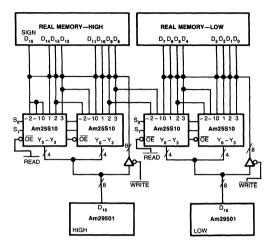

| "One-chip sequencer shapes up addressing for large FFTs," by David Quong and Robert Perlman, from <i>Electronic Design</i> , July 12, 1984. (Am29540)                                                                               | 77  |

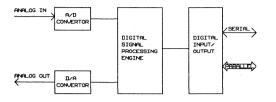

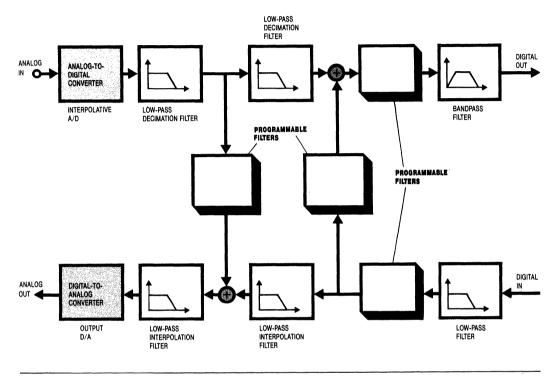

| "Customizable analog circuits using digital signal processing," by Russell J. Apfel, presented at WESCON, October, 1984. (Am7910/11, Am7901A)                                                                                       | 85  |

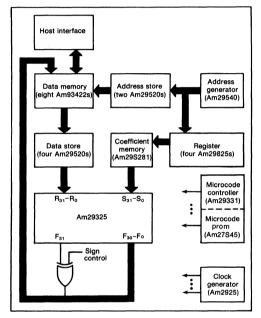

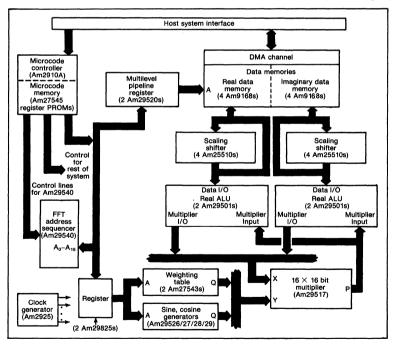

| "500-kHz single-board FFT system incorporates DSP-optimized chips," by Robert Cohen and Robert Perlman, from EDN, October 31, 1984. (Am29500 family)                                                                                | 94  |

| "Very-high-speed floating-point processor," by B.J. New, presented at ELECTRONICA, November, 1984.<br>(Am29325)                                                                                                                     | 102 |

#### CONTENTS

#### **Telecommunications/Data Communications**

| "Technology evolution towards digital systemax access?" by Hadi Ibrahim, presented at Mini/Miara Northaast, May                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

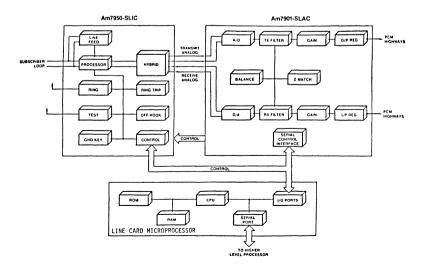

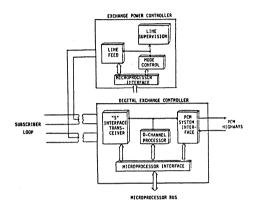

| "Technology evolution towards digital customer access," by Hadi Ibrahim, presented at Mini/Micro Northeast, May<br>1984. (Am7950, Am7901A, Am79C31, Am7938)                                                             | 111 |

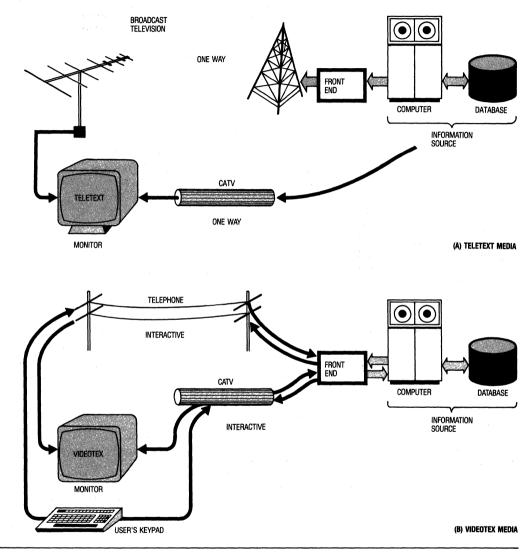

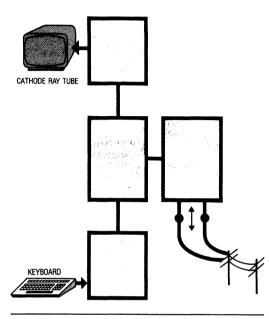

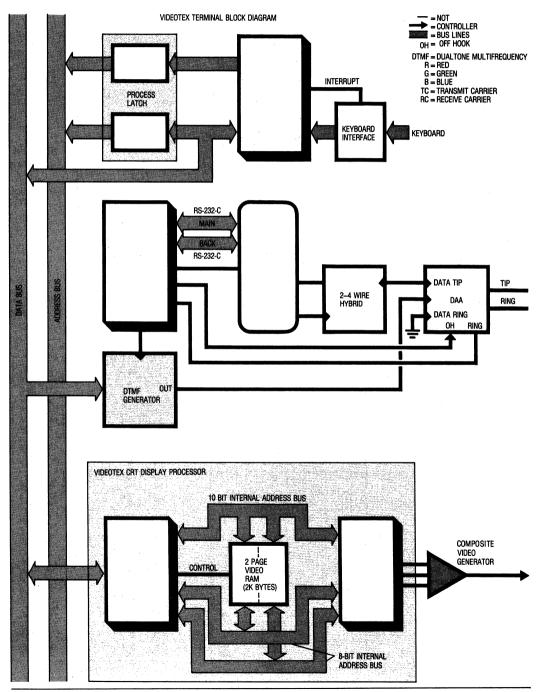

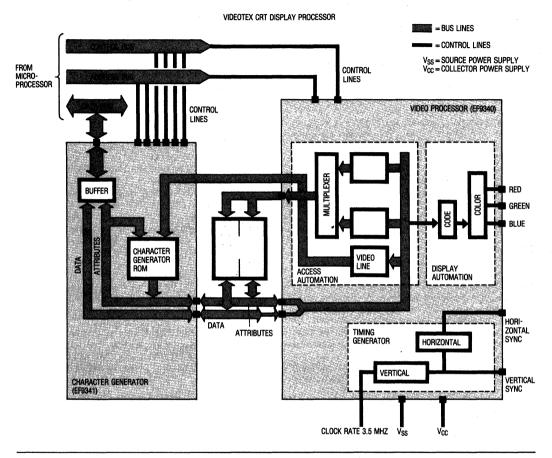

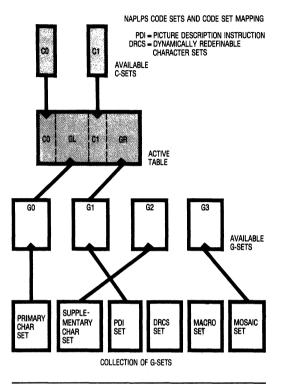

| "Videotex hardware heralds another node—the home," by Stevan Eidson, from <i>Data Communications</i> , June, 1984.<br>(Am7911)                                                                                          | 115 |

| "Third-generation codecs pave way for future digital networks," by Jeffry L. Parker, from <i>Data Communications</i> , September, 1984. (Am7901A)                                                                       | 124 |

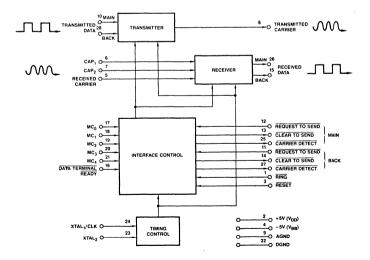

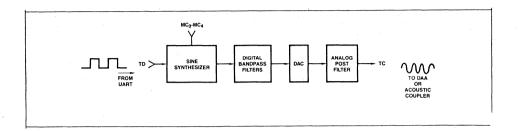

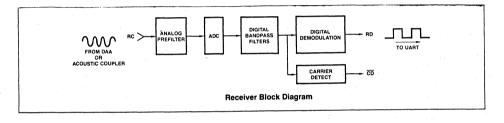

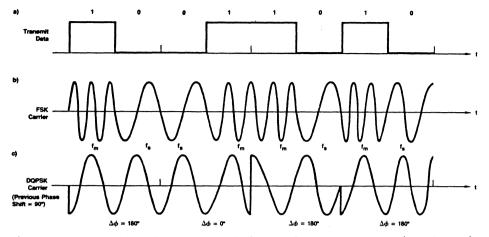

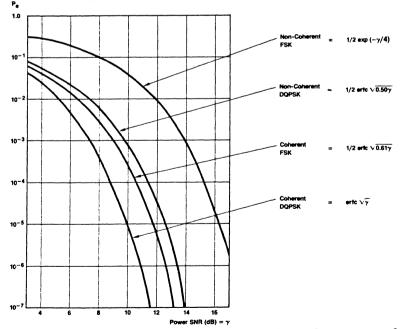

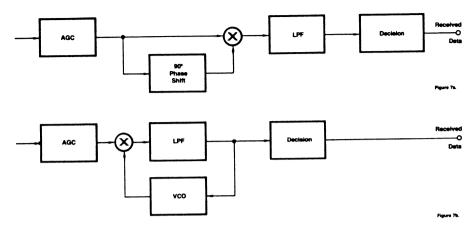

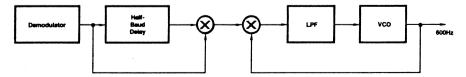

| "Design of a Single-Chip Bell 212A Compatible Modern Employing Digital Signal Processing," by Stevan Eidson, presented at the IEEE Workshop on VLSI Signal Processing, November, 1984.                                  | 130 |

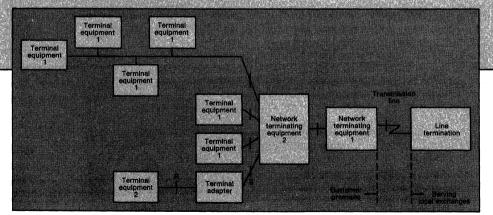

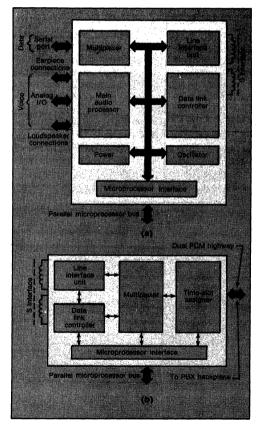

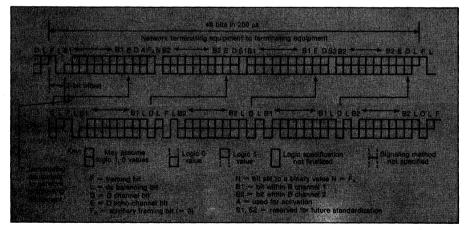

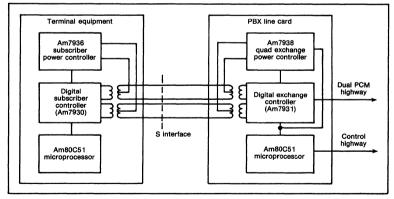

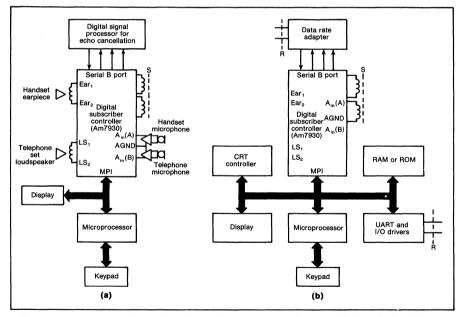

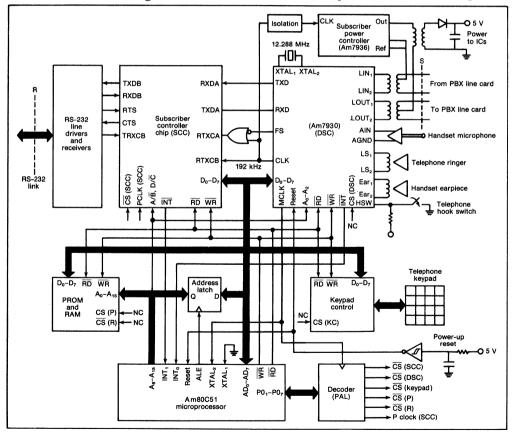

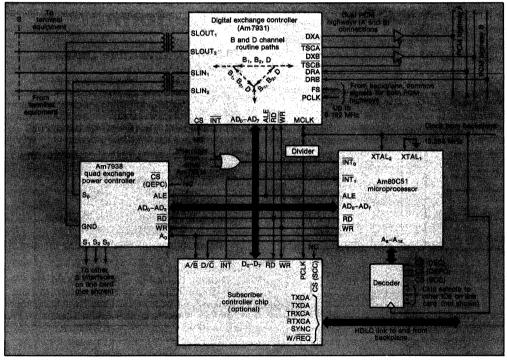

| "Controller chips pair up in S interface for ISDN systems," by Alan Clark, from <i>Electronic Design</i> , December 13, 1984. (Am79C30, Am79C31, Am7936, Am7938)                                                        | 143 |

| MOS Microprocessors and Peripherals                                                                                                                                                                                     |     |

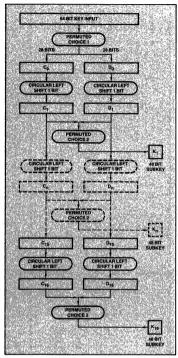

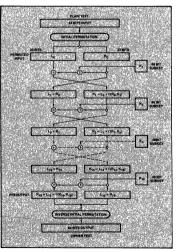

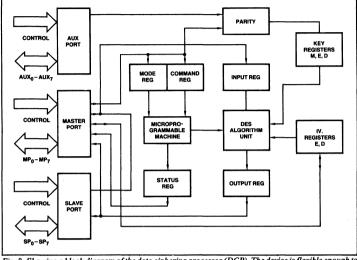

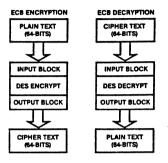

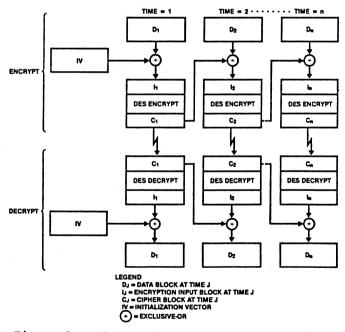

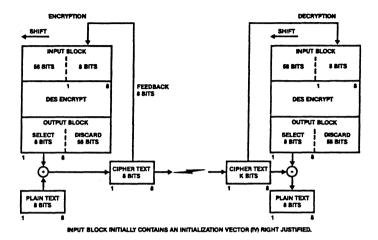

| "Data encryption: high-speed implementation of DES," by Subodh K. Banerjee, from <i>Communications Engineering International</i> , (United Kingdom) June, 1984. (AmZ8068)                                               | 153 |

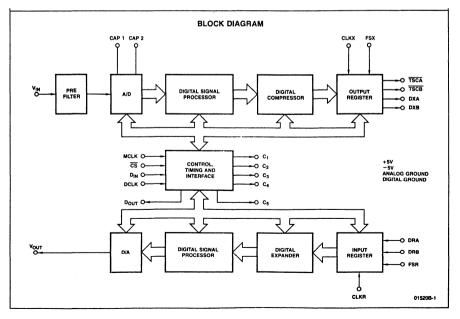

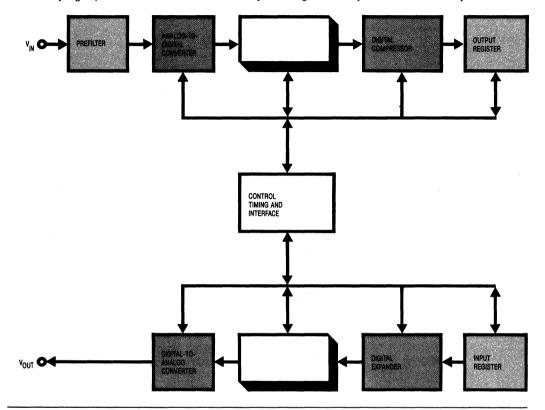

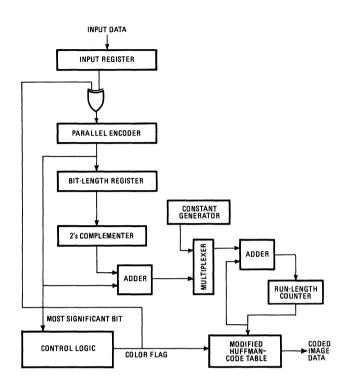

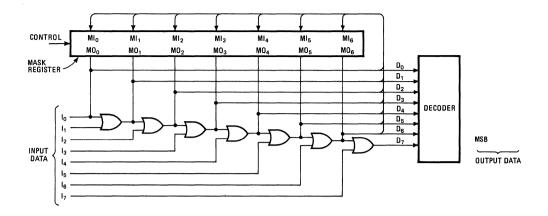

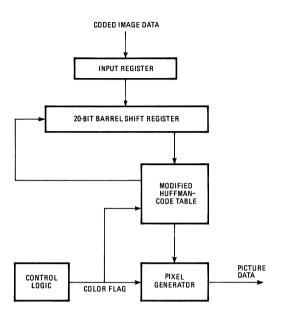

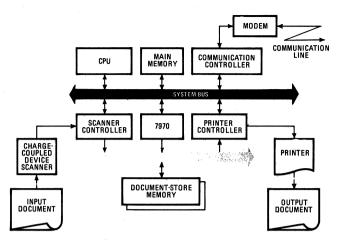

| "Data-compression IC saves on storage and speeds up image transmission," by James Williamson and Shinkyo Kaku, from <i>Communications Systems Equipment Design</i> , October, 1984. (Am7970)                            | 156 |

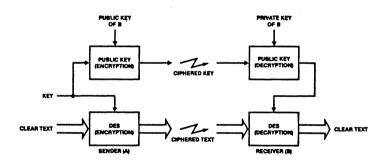

| "Data security with fast, high-integration circuits," by Juergen Stelbrink, presented at ELECTRONICA, November,<br>1984. (AmZ8068, Am9518, Am9568)                                                                      | 161 |

| Local Area Networks                                                                                                                                                                                                     |     |

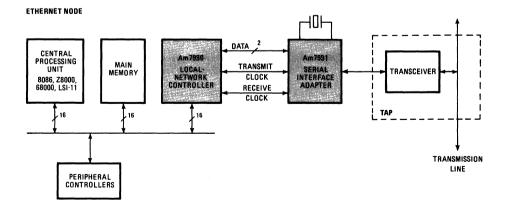

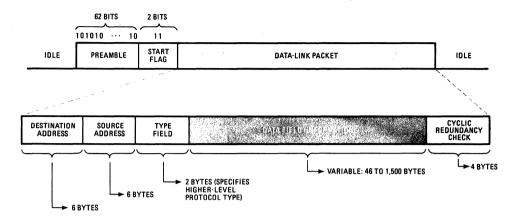

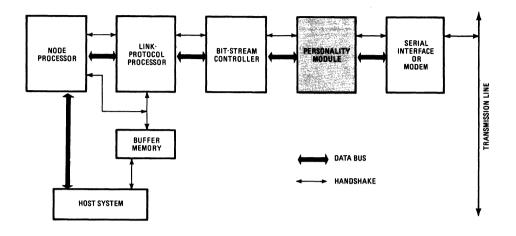

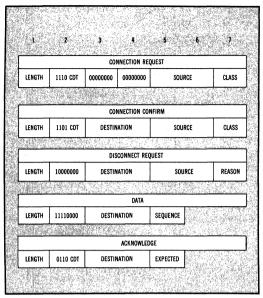

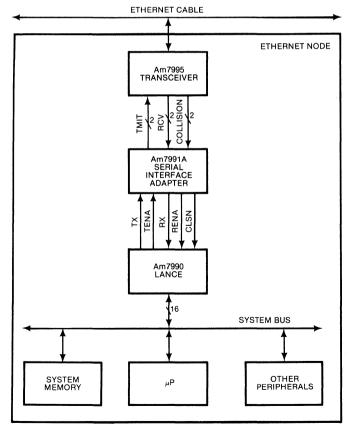

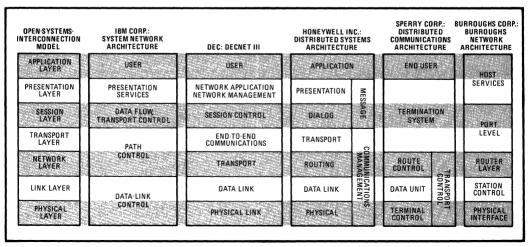

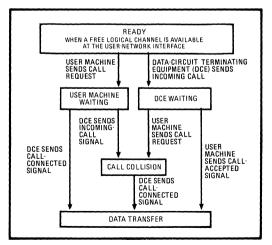

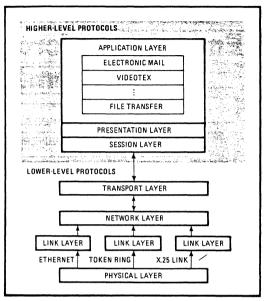

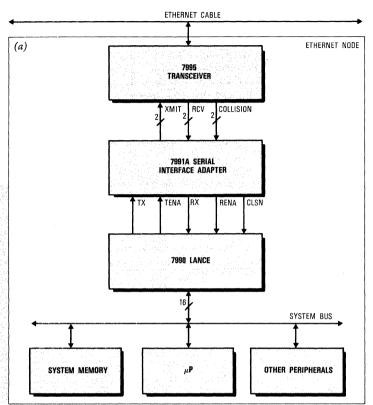

| "Protocols and network-control chips: a symbiotic relationship," by Sunil Joshi and Venkatraman lyer, from <i>Electronics</i> , January 12, 1984. (Am7990, Am7992A, Am7995)                                             | 169 |

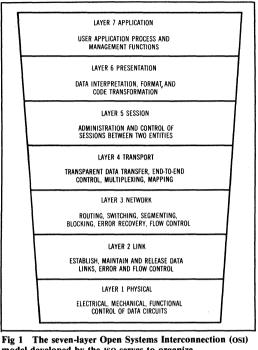

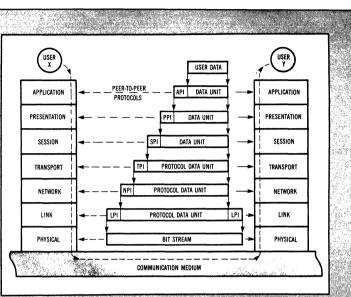

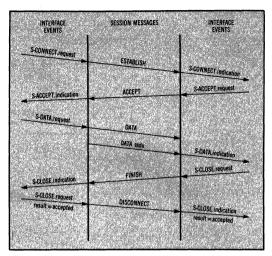

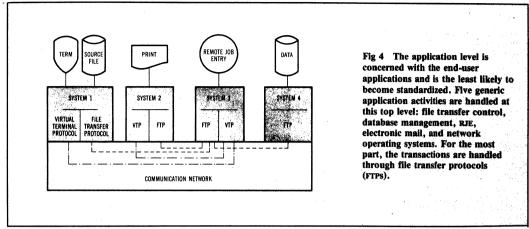

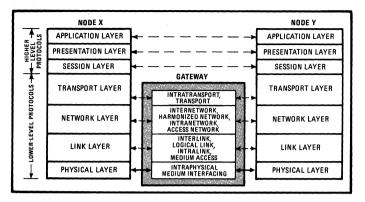

| "Standardizing upper-level network protocols," by David Berry, from Computer Design, February, 1984                                                                                                                     | 176 |

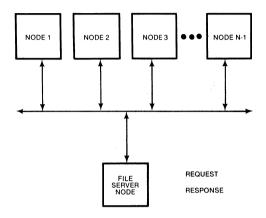

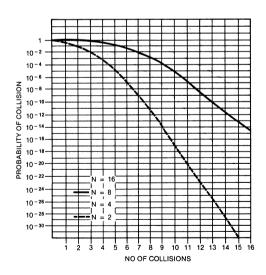

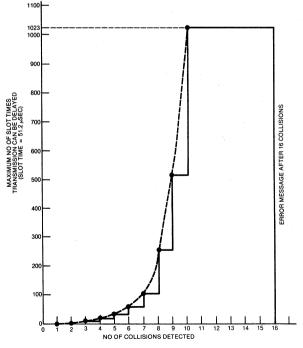

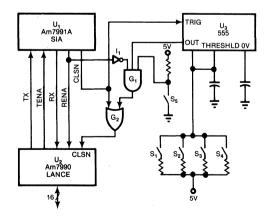

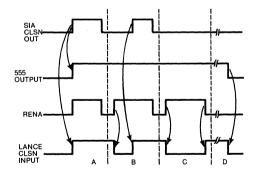

| "Design real-time Ethernet systems by giving priority to nodes," by Vernon Coleman, from <i>EDN</i> , March 22, 1984. (Am7990, Am7992A, Am7995)                                                                         | 184 |

| "Protocol standardization works its way up the ladder of the OSI model," by David Berry, from <i>Electronics</i> , June 14, 1984.                                                                                       | 190 |

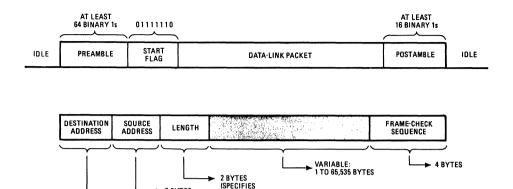

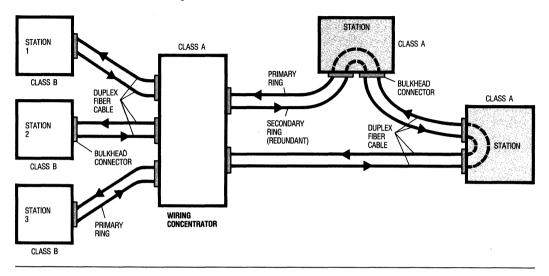

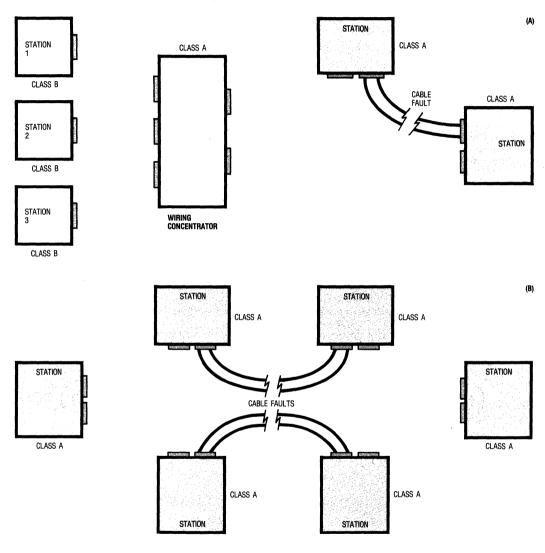

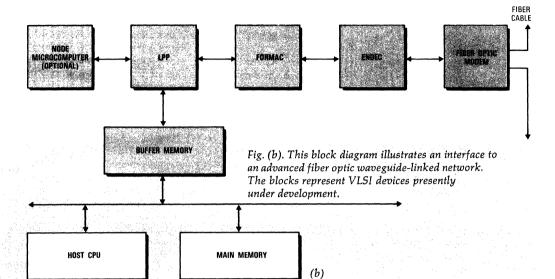

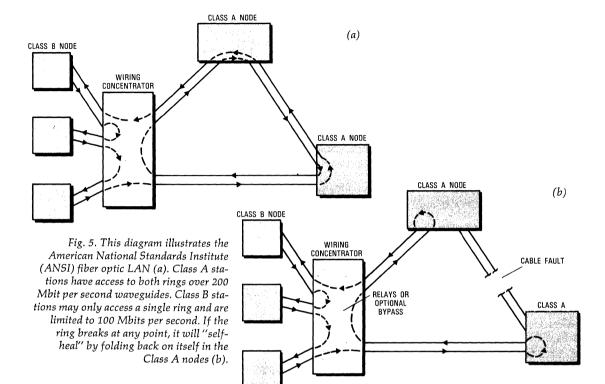

| "New standards for local networks push upper limits for lightwave data," by Sunil Joshi and Venkatraman lyer, from<br>Data Communications, July, 1984.                                                                  | 194 |

| "VLSI and digital networking," by Vernon Coleman, from Integrated Circuits, December, 1984. (Am7990, Am7992A, Am7995)                                                                                                   | 202 |

| Graphics                                                                                                                                                                                                                |     |

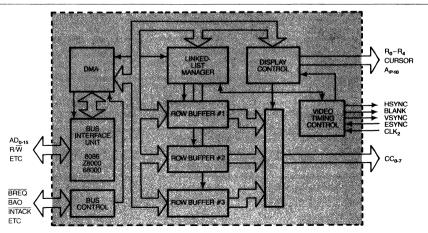

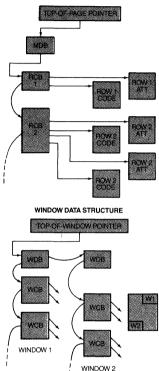

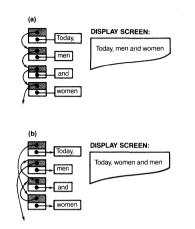

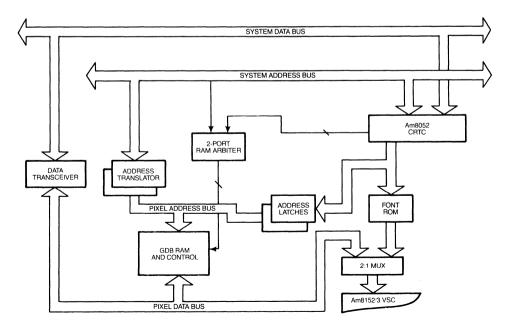

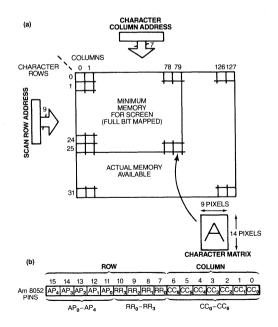

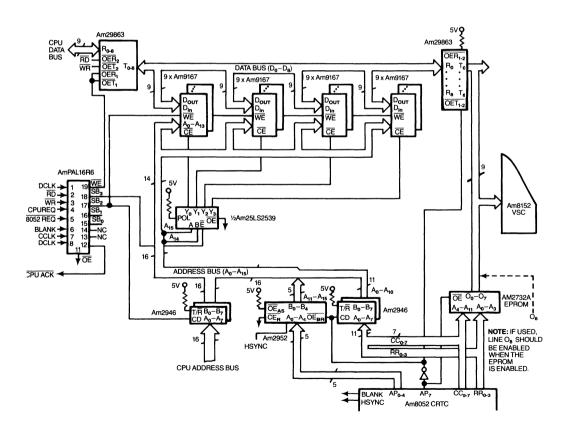

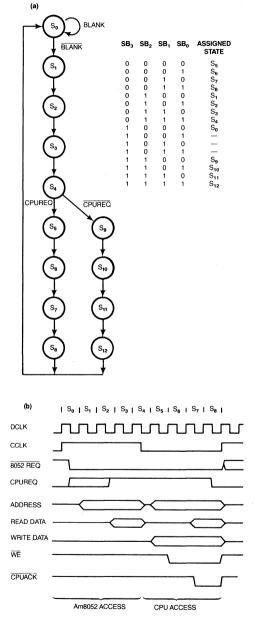

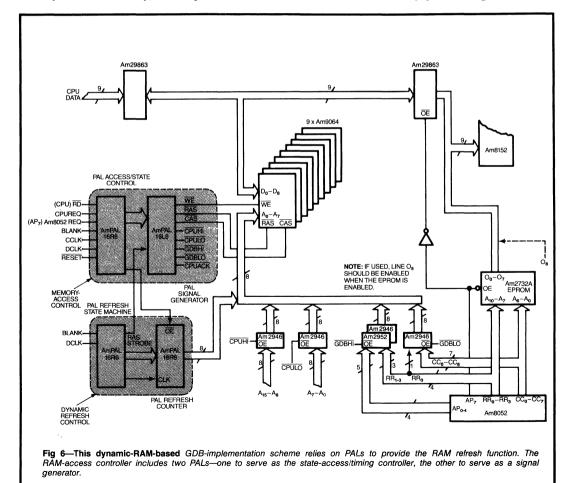

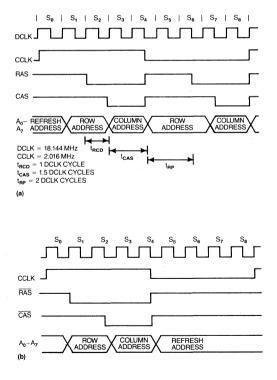

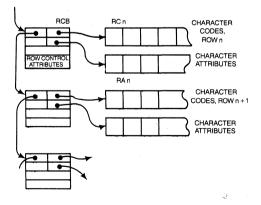

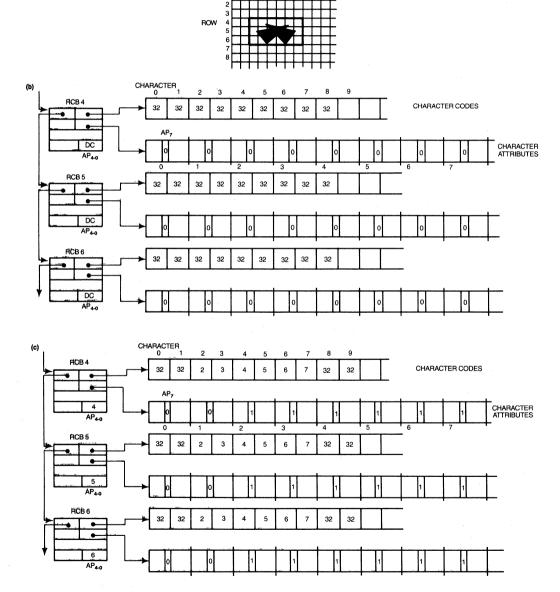

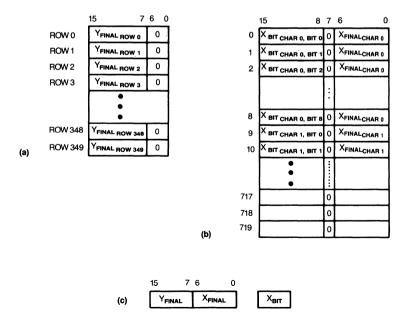

| "Use a CRT-controller chip to mix text and graphics," by Mark S. Young, from EDN, May 31, 1984. (Am8052, Am8152A)                                                                                                       | 210 |

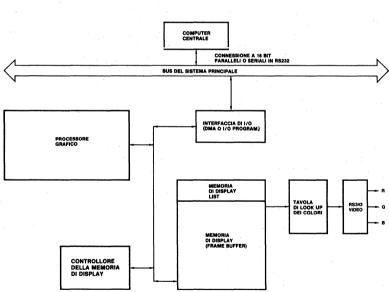

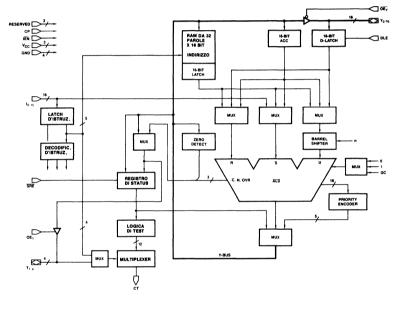

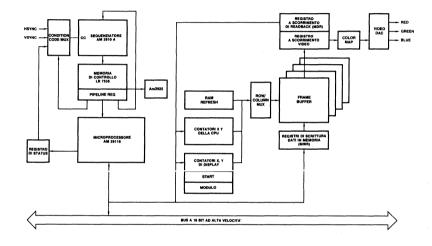

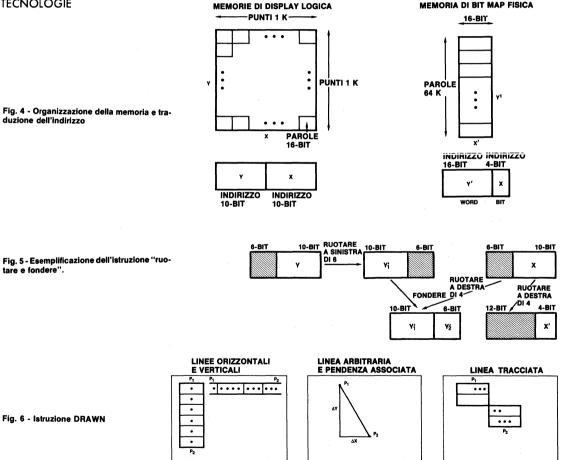

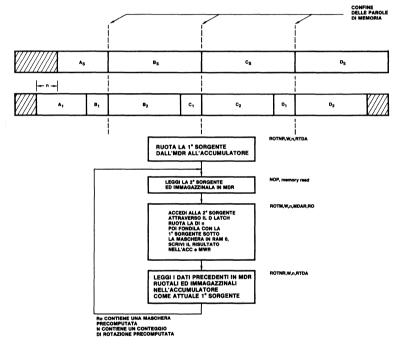

| "Nuove architetture per accelerare la gestione dei pixel nelle applicazioni grafiche," by W. Miller and R. Mazzoni, from <i>Elettronica Oggi</i> , (Italy) September, 1984. (Am29116)                                   | 223 |

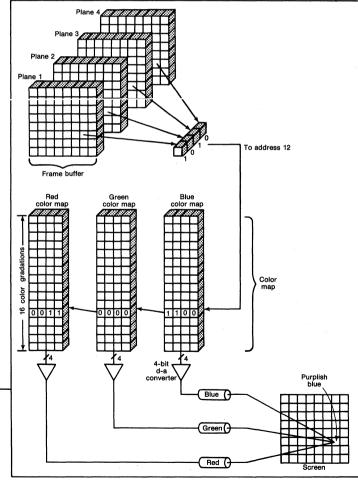

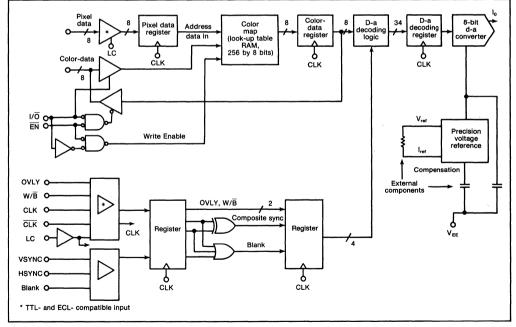

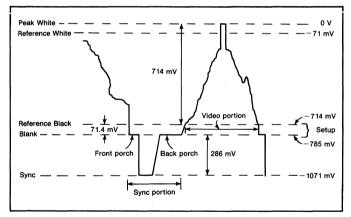

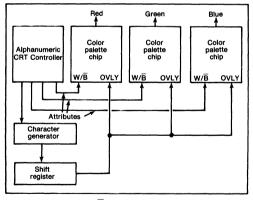

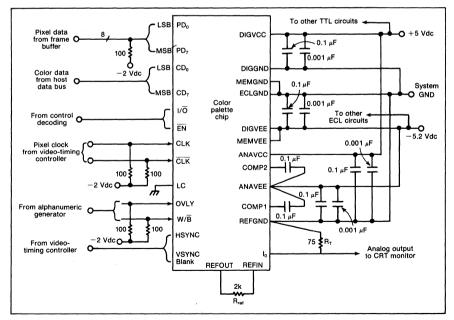

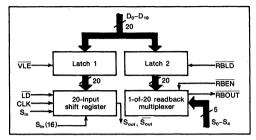

| "Monolithic color palette fills in the picture for high-speed graphics," by Steven B. Sidman and John C. Kuklewicz, from <i>Electronic Design</i> , November 19, 1984. (Am8151)                                         | 234 |

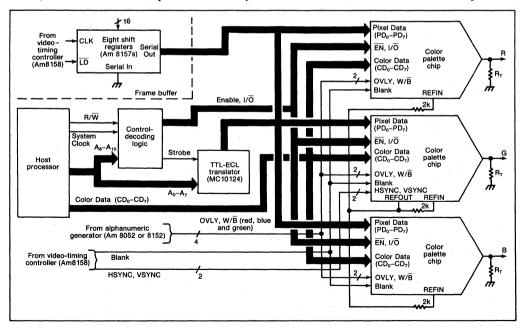

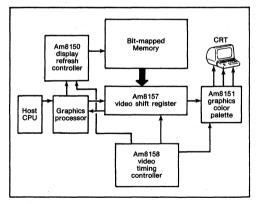

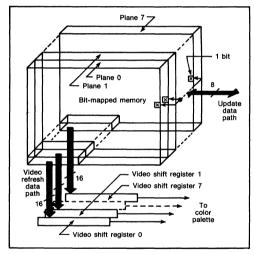

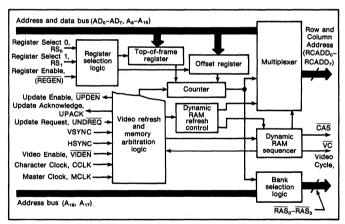

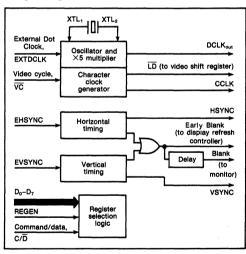

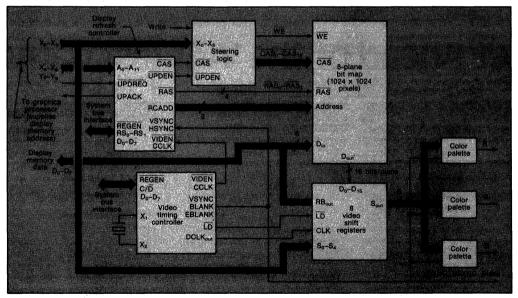

| "Three chips, plus palette, aid graphics designers to paint detailed pictures," by Andrew Daniel, Adrian Sfarti, and Achim Strupat, from <i>Electronic Design</i> , November 29, 1984. (Am8150, Am8151, Am8157, Am8158) | 243 |

| Mass Storage                                                                                                                                                                                                            |     |

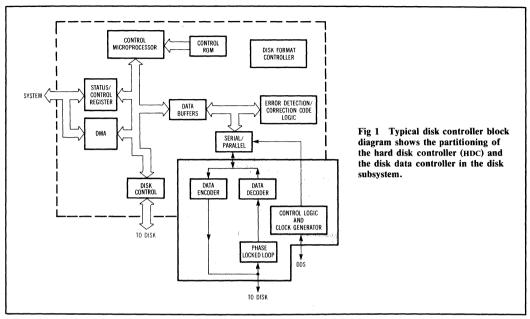

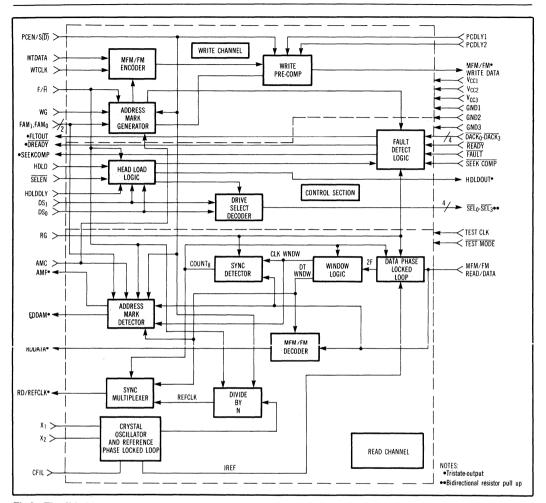

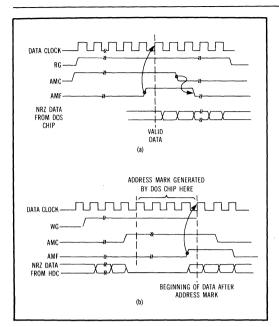

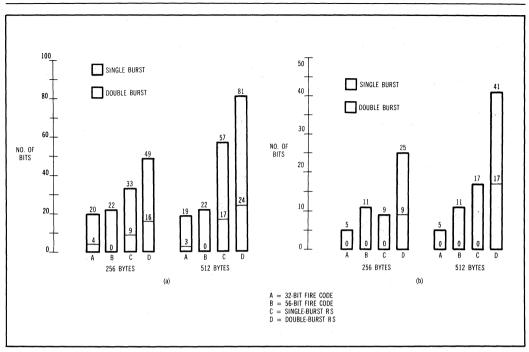

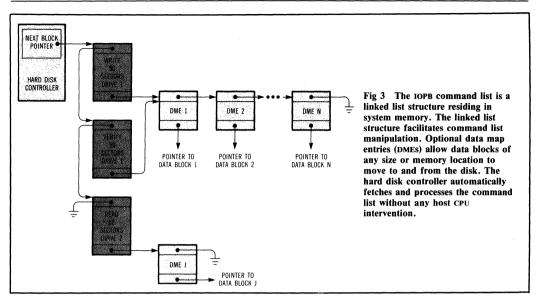

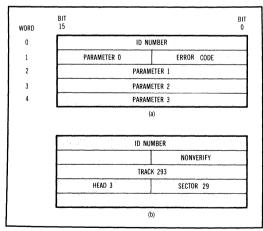

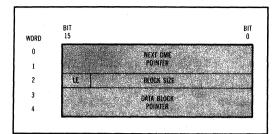

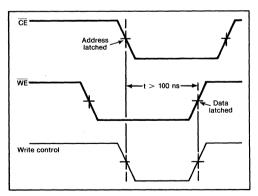

| "Two-chip set tackles disk control problems," by Mark S. Young, Pradeep Padukone, and Neil Adams, from <i>Computer Design</i> , October 1, 1984. (Am9580, Am9581)                                                       | 250 |

| "Winchester/floppy controller eases disk interfacing," by Mark S. Young, from <i>Computer Design</i> , October 15, 1984. (Am9580, Am9581)                                                                               | 258 |

|                                                                                                                                                                                                                         |     |

#### CONTENTS

#### **Memory Products**

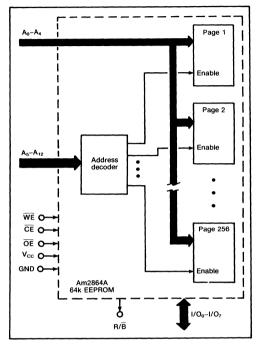

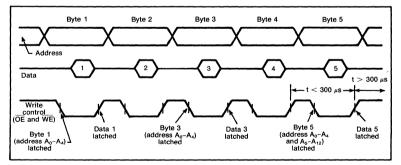

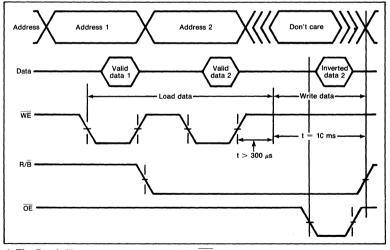

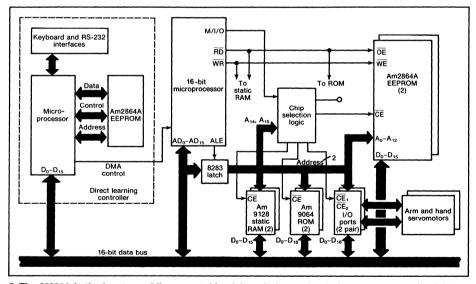

| "64-kbit EEPROM speeds in-system reprogramming, adds data polling," by Ken Pope, from <i>Electronic Design</i> , August 23, 1984. (Am2864A)                                                                                  | 266 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

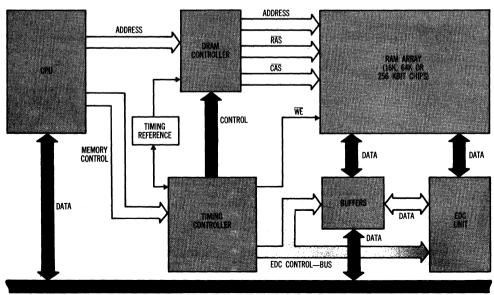

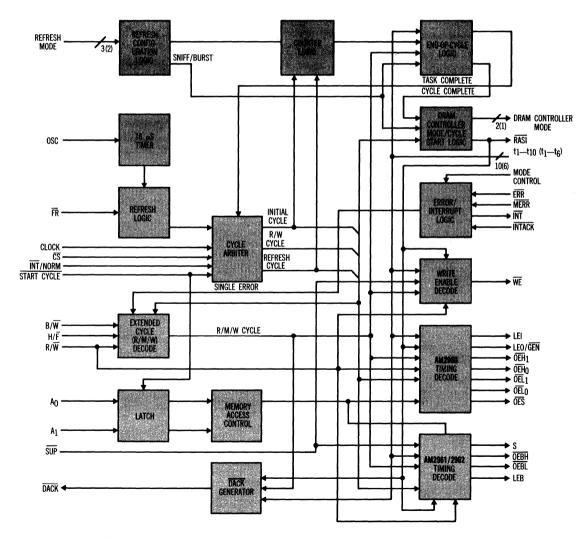

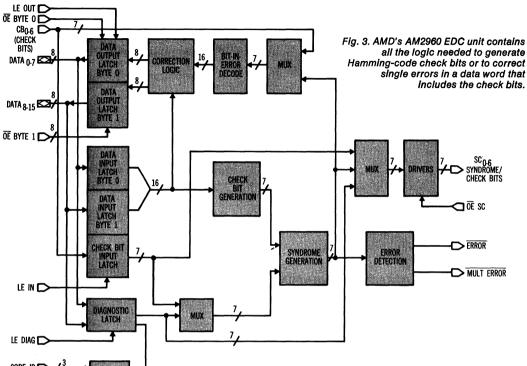

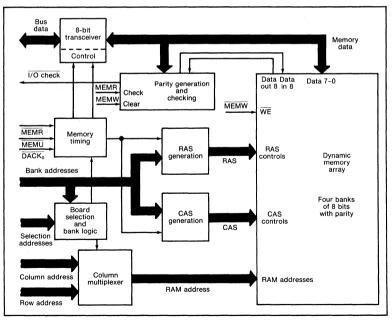

| "DRAM controller helps scrub errors," by Jimmy Madewell, from <i>Electronic Products</i> , September 17, 1984.<br>(Am2968, Am2960)                                                                                           | 273 |

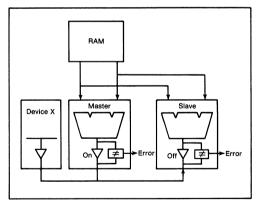

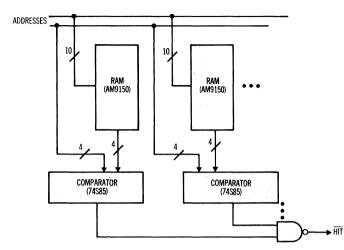

| "Resettable RAMs speed cache systems," by Bruce Threewitt, from <i>Electronic Products</i> , November 15, 1984.<br>(Am9150)                                                                                                  | 278 |

| Programmable Logic                                                                                                                                                                                                           |     |

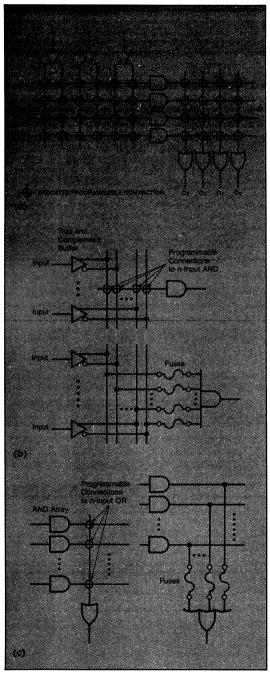

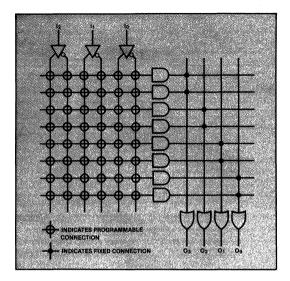

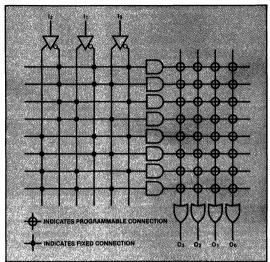

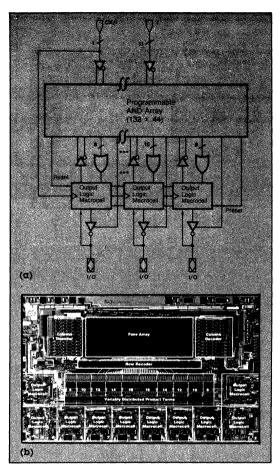

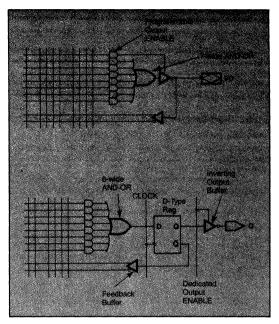

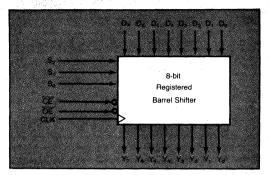

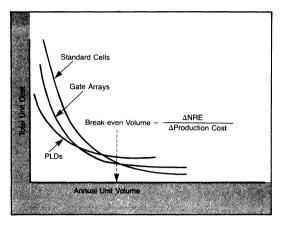

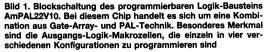

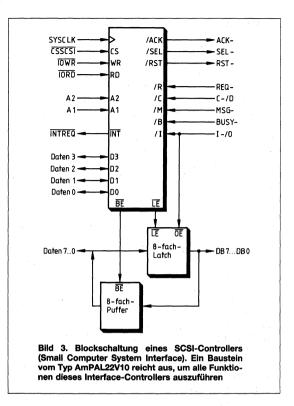

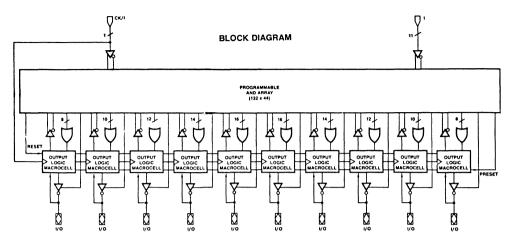

| "The Role of Programmable Logic in System Design," by Om P. Agrawal and David A. Laws, from VLSI Design,<br>March 1984. (AmPAL22V10)                                                                                         | 282 |

| "Super-minicomputer design using PALs," by Bradford S. Kitson and B. Joshua Rosen, from <i>Electronic Engineering</i> ,<br>(U.K.) March, 1984. (AmPAL16R4, AmPAL16R6, Am25S10)                                               | 288 |

| "Logic-programming language enriches design processes," by Brad Kitson and Kevin Ow-Wing, from <i>Electronic Design</i> , March 22, 1984. (PLPL, AmPAL22V10)                                                                 | 294 |

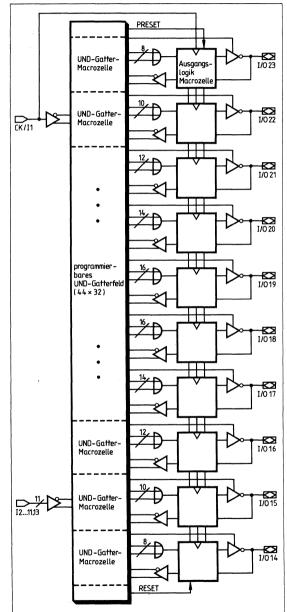

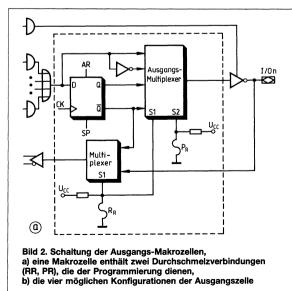

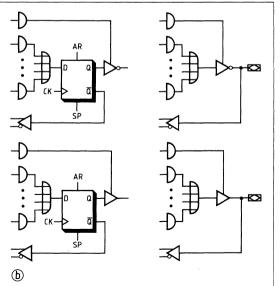

| "Logik-Baustein kombiniert PAL- und Gate-Array-Technik," by Brad Kitson, Dave Laws, and Warren Miller, from<br><i>Elektronik</i> , (Germany), March 23, 1984. (AmPAL22V10)                                                   | 302 |

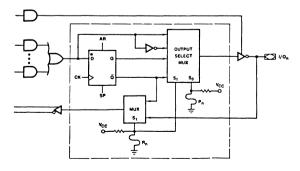

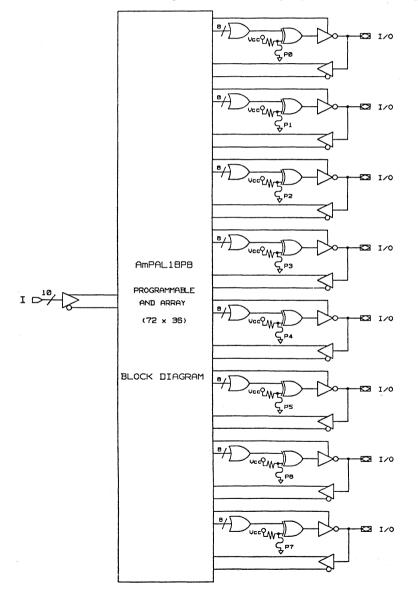

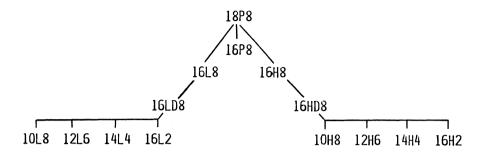

| "Second-Generation Programmable Logic Devices Extend Design Capabilities," by Jenny Yee, presented at WESCON, October, 1984. (AmPAL22V10, AmPAL18P8)                                                                         | 306 |

| On-Chip Diagnostics                                                                                                                                                                                                          |     |

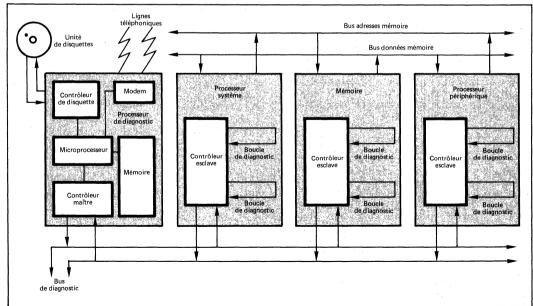

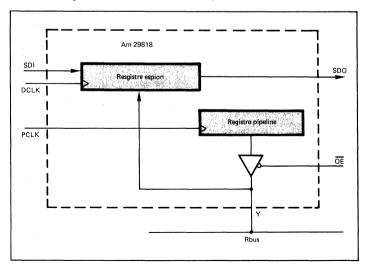

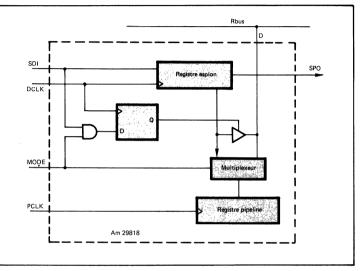

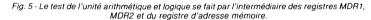

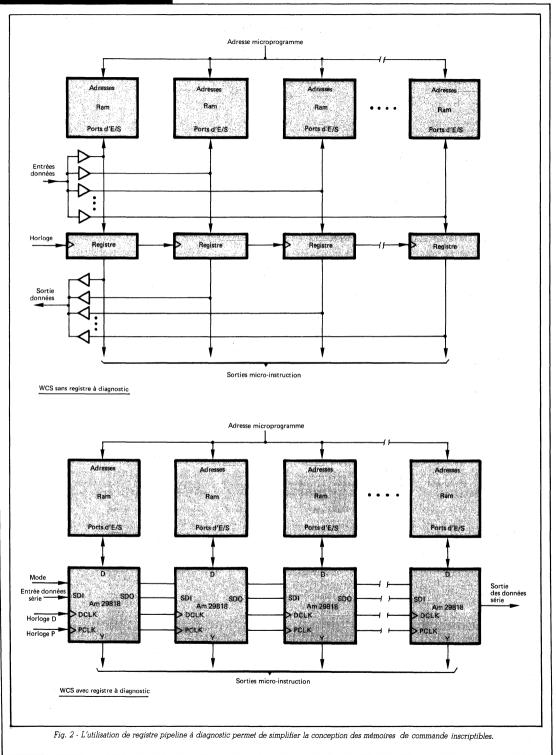

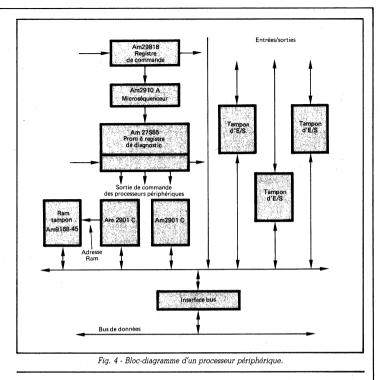

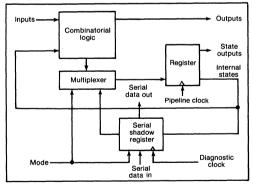

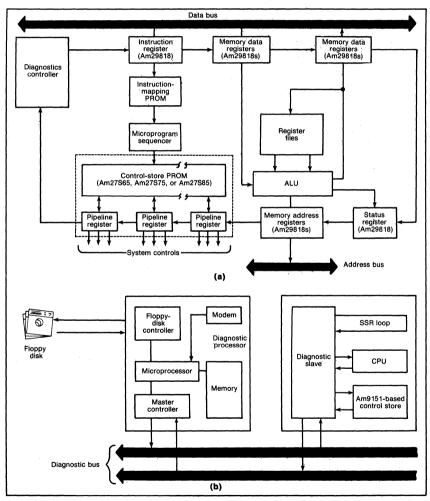

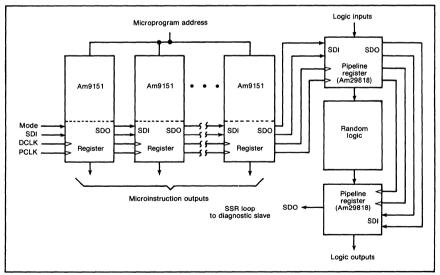

| "Methode de test et de conception de diagnostic," (parts 1 and 2), by Kevin Ow-Wing, from <i>Minis et Micros</i> , (France)<br>February 27 and March 12, 1984. (Am29203, AmPAL16H8A, Am29818, Am9168, Am2910, Am27S65/75/85) | 312 |

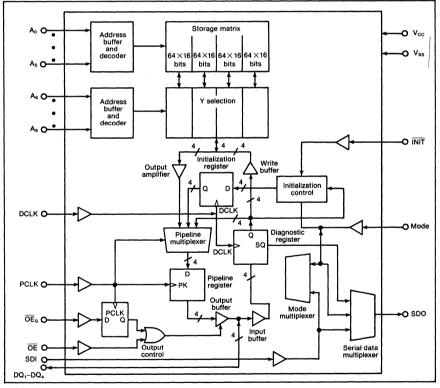

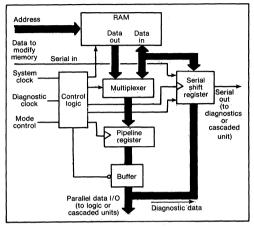

| "RAM's on-chip registers build simple control stores that include self-diagnostics," by Bruce Threewitt, from<br>Electronic Design, June 14, 1984. (Am9151)                                                                  | 322 |

### PREFACE

The articles and conference papers included in this volume are the best examples of the products, technology, and applications that have made Advanced Micro Devices a leader in the integrated circuit industry. These articles and conference papers from 1984 are organized by the major application areas that incorporate AMD chips, such as telecommunications, networking, graphics, digital signal processing, and mass storage. We are publishing them to underscore AMD's substantial contributions to computation, instrumentation, and telecommunications technologies.

Founded in 1969, Advanced Micro Devices is a leading worldwide supplier of proprietary and industry-standard semiconductors for manufacturers of electronic systems. The company produces a broad range of devices, including microprocessors, peripherals, memories, telecommunications and logic products, and semicustom integrated circuits. With state-of-the-art bipolar and CMOS manufacturing capabilities, AMD is in a unique position to draw on the strengths of both technologies to provide the products demanded by an increasingly sophisticated market. At the same time, the company offers the highest quality guarantee in the industry for every one of its products.

AMD is the fastest growing U.S. semiconductor manufacturer, with a 10-year compound annual growth rate of 42 percent. Fiscal 1985 ended with net sales of over \$930 million, up from \$583 million for fiscal 1984. AMD employs over 15,000 people worldwide, and has manufacturing facilities in Sunnyvale and Santa Clara, California; Austin and San Antonio, Texas; Woking, England; Penang, Malaysia; Manila, Philippines; Bangkok, Thailand; and Singapore. AMD's corporate headquarters are in Sunnyvale.

# Denser process gets the most out of bipolar VLSI

To shrink bipolar chips to feature sizes of very large-scale integration, IMOX-S technology implements a series of closely related processing steps

by Phil Downing, Pete Gwozdz, and Bernie New, Advanced Micro Devices Inc., Sunnyvale, Calif.

Design considerations for new integrated systems range widely, from projecting on-board power consumption to estimating production costs, but the principal benchmarks of performance are the speed and density of individual large-scale integrated circuits. Though significant improvements in system size and capability are nothing new, it is only with the most recent bipolar processing techniques, such as IMOX-S (for ion implantation, oxide isolation with scaling), that the benefits of bipolar speed have come to very large-scale integration (see "Designing high-performance systems with newer, faster processors," below).

#### Shrinking size, power use

High-speed IMOX technology, introduced in 1980, has been incorporated into such products as the 2901 bit-slice microprocessor and the 29116 bipolar microprocessor, as well as into various programmable read-only memories and logic chips. When development began on IMOX-s, two principal goals were an improvement in speed and in gate densities: chips produced with it were to be denser, incorporate smaller geometries, and be significantly faster than earlier IMOX parts or other bipolar ICs (see table). At the same time, the designers of the new scaled process wanted to avoid the increase in power level that usually accompanies higher processing speeds, and this they brought off as well.

At first, it may seem impossible to satisfy these usually incompatible requirements. IMOX-S, however, succeeds by concentrating not only on the primary contributions of each processing step but also on how the successive steps interrelate. These interrelationships—one of the more interesting aspects of the IMOX-S process—work synergistically so that the final process is more than the sum of the individual steps.

Like many other processes, IMOX makes use of oxide isolation for device sizes that are smaller than older, junction-isolation processes could achieve. But the designers of other processes opted for an unwalled-emitter structure that requires extra silicon area (the absence of which would allow the emitter and collector regions to make electrical contact, thus incapacitating the transistor) to isolate the collector and emitter regions.

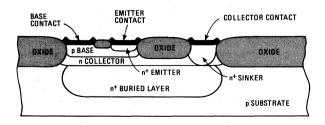

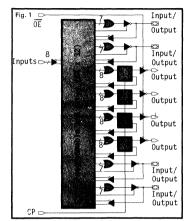

IMOX instead uses oxide isolation to wall off the transistor's emitter (Fig. 1), eliminating the wasted area found in the unwalled-emitter approach—the field oxide defines three of the emitter's four edges. The direct contribution of oxide isolation to shrinking device size is considerable; when combined with a walled-emitter structure, the result is dramatic.

#### Speed, too

Oxide isolation and walled-emitter structures have the advantage of speed, as well as of greater density. Device speeds are faster because some of the capacitances that usually reduce the switching speed have been eliminated through the reduced device area. The collector-to-base capacitance usually accounts for 50% of the total delay

#### Designing high-performance systems with newer, faster processors

Architectural enhancements such as microprogramming in very large-scale integrated circuits can allow one processor to do more useful work than another in a single instruction cycle—but, as a rule of thumb, the faster a processor executes instructions the better. Hence the single most telling specification for any processor, and potentially the most demanding performance requirement, is the instruction-cycle time.

For pure speed, the 29116A 16-bit microprogrammable processor and the 29517A pipelined 16-by-16-bit multiplier—both fabricated with the IMOX-S process—should be considered for the core of high-performance dedicated systems such as graphics processors. The 29116A and the 29517A can execute instructions in as little as 80 nanoseconds—more than 10 times as fast as a fixed-instruction-set microprocessor for similar instruction complexity.

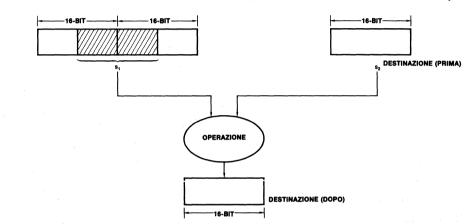

Besides the more familiar logical and arithmetic instructions, the 29116A has the type of instructions necessary for image-oriented graphics algorithms. For example, singleclock-cycle instructions can rotate from 1 to 16 places and merge two 16-bit data fields on a bit-by-bit basis, as well as prioritize a 16-bit data value. In addition, the 29517A, through inclusion of pipeline processing, executes a 16-by-16-bit multiplication with a 32-bit result in one clock cycle.

| Process                                              | Nonoxide-<br>isolated<br>processes                     | IMOX                                                               | IMOX-S                                                                           |

|------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Technology                                           | Contact alignment<br>Isotropic etch<br>Two-layer metal | 1 : 1 projection<br>alignment<br>Isotropic etch<br>Two-layer metal | Stepper technology<br>Anisotropic etch<br>(including metal)<br>Three-layer metal |

| Minimum drawn<br>feature size (µm)                   | 4.0                                                    | 3.0                                                                | 1.5                                                                              |

| Metal pitch (µm)                                     | 11.0                                                   | 8.0                                                                | 4.0                                                                              |

| In-circuit gate delay<br>at 1 mW (ns)                | ·                                                      | 1.5                                                                | 0.8                                                                              |

| Transistor maximum operating frequency $(f_T)$ (GHz) | ·                                                      | 2                                                                  | 2                                                                                |

when operating at 1-milliwatt gate power, but, because the walled emitter directly reduces the base size, the associated collector-base capacitance drops.

The use of the walled-emitter transistor structure neatly reduces device size; complementing this feature of the process architecture are fabrication techniques—most prominently the use of stepper lithography and anisotropic etching. Compared with more traditional masking techniques, steppers cause minimal variations over a wafer's surface by exposing wafers a few die at a time. In addition, misalignment problems are less severe because a few die at most are aligned at a time, whereas traditional methods align the entire wafer at once.

#### **Reactive ion etching**

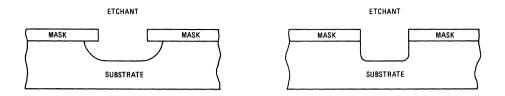

Anisotropic etching (Fig. 2) controls the direction of the removal of material from the wafer surface; the usual means is either a plasma or reactive ion-etching process, which is the process used for IMOX-s. Side etching is minimized with anisotropic etching, which removes only the material directly below the mask opening.

Since anisotropic etching allows the smallest feature size while wafer-stepping technology draws fine line widths, the overall result is a much smaller device—one that can be defined to the full limit of the lithographic process, not only because of the individual benefits of each step but also because of the synergistic interrelationship of the steps.

The IMOX-S transistor structure, fabricated with a combination of the above techniques, has a number of advantages over transistors fabricated with the older diffusionbased processes. The ion-implanted base and emitter

regions intersect at a much lower concentration level than the diffusedbase structure. Because dopant levels are lower, the base-emitter capacitance per unit is lower, reducing delay. Furthermore, the transistor's gain, or beta—which primarily depends on the total amount of dopant deposited in the base region—is much more controllable in the ionimplanted structure.

In a transistor fabricated with a diffusion-based process, which has a high level of dopant concentration at the intersection of the base and emitter, a shift in the intersection causes a dramatic change in the base dop-

ant. The implanted structure, with its lower intersection concentration, will be less sensitive to these shifts, will have tighter beta tolerances, and hence will be faster.

One of the differences between the IMOX-S transistor and other modern transistor structures is the use of a low-resistance plug, or sinker, directly below the collector contact. In IMOX-S, the usual buried layer of lowresistance silicon alone does not reduce the collector resistance to levels consistent with the process's speed and power requirements. Concern for collector resistance grows as transistor size shrinks, but the addition of the implanted sinker provides a low-resistance path from the contact to the base-collector junction.

#### Hooking up

Once device sizes are at the minimum, there is little extra space over which to route the necessary interconnections. In addition, each metal line placed on the surface occupies precious silicon area, which could have been used to implement transistors. In IMOX-s, threelayer-metal technology places a large portion of the interconnection off the silicon surface, making interconnection easier and less expensive since it wastes less die area.

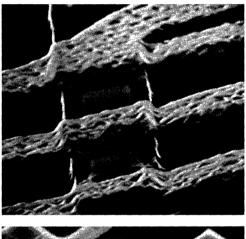

Before, multiple-layer-metal techniques required wide, thick metal lines to compensate for the discontinuities, or steps, in the silicon surface left by previous etching and diffusion steps. The die surface lost the planarity, or smoothness, necessary for thin, narrow metal lines. As Fig. 3a shows, steep steps in the wafer surface might cause metal lines to narrow and tear. Thicker metal lines would be necessary to ensure reliable metal interconnection. Thicker lines, however, tend to make the surface

> even more ragged, which makes top layers of metalization even more difficult to apply.

> But the IMOX-S process uses carefully selected oxide growth and etch steps to retain the surface's planarity

> 1. Walled in. Rather than using up precious silicon real estate to electrically isolate the transistor's collector and emitter regions, IMOX-S surrounds the emitter with a wall of oxide. The sinker, or low-resistance plug, facilitates current flow to the buried layer.

2. Perpendicular etching. Isotropic etching (a) removes material in all directions below a mask, making the feature size larger than the limit of the lithographic process. But the anisotropic-etching technique (b) used in IMOX-S burns straight down into the wafer.

(Fig. 3b). The first metal layer can be placed on this planar surface much more reliably and with tighter tolerances, thereby contributing to the overall increase in density.

Smaller metal lines also contribute indirectly to improved performance: if the lines are narrower, because of improved lithography and processing techniques, and

shorter, because of higher device density, then the capacitance associated with each line is reduced. Lower capacitance makes higher performance levels possible, especially on high fan-out transistors such as internal output drivers on bus-organized VLSI chips.

Second-layer metal now contends with the newly discontinuous surface introduced by the addition of the first metal layer. A planarization technique called oneto-one etching is used to remove this new discontinuity. The technique first creates an oxide layer over the entire wafer surface, covering metal as well as silicon. A photoresist-which is specially etched at the same rate as the new oxide covering-is spun on with a centrifuge in order to create a smooth surface, and the surface is then etched until only oxide remains.

Because the photoresist etches at the same rate as the oxide, the resulting ox-

3. Smooth. The first layer of metal interconnection for a conventional bipolar process (a) is much more ragged than in IMOX-S (b). The smoother the silicon and oxide surface below the metal layer, the more reliable the finished integrated circuit will be.

ide surface has the desired smooth planar quality. Hence the second layer of metal has the thin and narrow qualities necessary for a high-density VLSI process.

The third layer of metal in IMOX-S chips is used almost exclusively for power and ground buses—hence a thick, wide metal line is desirable to reduce the resistance of the metal and thus minimize unwanted voltage drops

> along these critical lines. A planar surface is no longer necessary after third-layer metal since no critical deposition steps follow.

> Owing to the huge commitment of capital and labor for new process development, it is important that an evolutionary path be followed so that it is easy to add future improvements in lithographic and diffusion technologies. IMOX-S can easily use new techniques to further reduce feature sizes because all the critical parameters of its transistor structure can be shrunk or scaled. In fact, the transistor structure was designed with this characteristic in mind.

> Further improvements will come with the IMOX X-85 process, with its slot-isolation technique-a narrow groove cut into the surface of the silicon wafer and filled with an insulator to isolate the adjacent active elements. IMOX X-85, now under development, will have a minimum feature size of 1 micrometer and a 2.5-um metal pitch, meaning that device size can be cut approximately in half. Yet these new devices to be fabricated with IMOX X-85 will deliver twice the performance of those fabricated with the IMOX-S process.  $\Box$

#### Bipolar and CMOS Technologies Become Partners In Digital Signal Processing

by Robert Perlman senior engineer Product Planning and Applications Advanced Micro Devices Sunnyvale, CA 94088

#### Abstract

Bipolar and CMOS technologies each offer distinct advantages to those interested in implementing hiqhperformance digital signal processing For applications requiring systems. high operating speeds, bipolar remains the process of choice; for applications requiring low power and more modest speeds, CMOS is suitable. By making judicious choices, the digital designer can use both technologies to produce an optimal design.

#### Introduction

Until a few years ago, designers of high-performance digital signal processing systems had little choice but to use bipolar technology. While the CMOS devices available at that time had the low power that many system architects desired, those devices were far too slow for serious consideration.

Today, although bipolar technology is still the solution for systems demanding the very highest performance, the advent of fast silicon-gate CMOS parts gives the designer a reasonable alternative when designing a system with somewhat more modest speed requirements. Bipolar and CMOS technologies differ in a number of significant ways. These differences have architectural implications that

the designer must be aware of when choosing a technology or technologies for implementation of a digital signal or array processing system.

#### Comparing the technologies

Speed - While it's generally that bipolar technology agreed is faster than CMOS, there's some disagreement as to just how much faster Estimating the speed advantage it is. of bipolar over CMOS is often а difficult task for the casual observer because, invariably, one has no choice but to compare an emerging technology with a mature one, or to compare devices with different functionality or architecture.

A case in point is a comparison the AMD Am29517A 16 between x 16 bipolar multiplier and the soon-to-beintroduced Am29C517 CMOS multiplier. The bipolar part has а clocked multiplication time of 38 ns over the commercial temperature range, the CMOS multiplier a time of 65 ns. One might rashly assume that the bipolar device is only seventy percent faster. This assumption, however, ignores the fact that the internal architectures are The bipolar part does not different. use a recoding algorithm, and forms the by summing sixteen partial product products, while the CMOS part uses twobit Booth recoding and fast adder

techniques to improve speed. A bipolar device designed with two-bit Booth and fast adders, and implemented with AMD's IMOX-S (for ion implantation, oxide isolation with scaling) process would be significantly faster than the Am29517A.

speed difference The actual between the fastest bipolar and the fastest CMOS parts is a factor of two While this figure is only a or three. rule of thumb, it finds its origins in AMD's experience with both technologies.

**Power** - A device's power comprises two terms - static power, which is dissipated when the device is quiescent, and A.C power, which is dissipated when the device's nodes toggle.

For applications demanding low static power, CMOS devices are clearly superior . The static power of a CMOS device is usually negligible; this low static power, appealing as it may seem, is rarely a consideration in high speed digital signal processing systems, as the devices in such systems are usually clocked at as fast a rate as is feasible. Much more significant is the contribution of the A.C. power term, which is roughly proportional to the system clock frequency. If the clock frequency is high enough, CMOS devices may actually dissipate more power than their bipolar counterparts - when comparing low-power Schottky with HC CMOS, for example, the cross-over point is in the neighborhood of 10 MHz. Τn many cases, it may be difficult to estimate the A.C power of a given CMOSbased system by means other than direct measurement, because the power is dependent on the average percentage of nodes that toggle during a clock cycle, this percentage varying from system to system.

Bipolar devices typically consume from one to ten times the power of CMOS devices. the exact ratio depending on the technologies being compared and the operating speed. Bipolar devices using internal ECL ( which include most of AMD's newer bipolar VLSI) draw more or less constant power, although capacitive effects and output driver totem pole currents give rise to a small speed-dependent power term.

Functional density - The functional densities of CMOS and ECLinternal bipolar devices are roughly the same. Although MOS is usually thought of as a high-density process, there is considerable difference in the densities of the various MOS technologies. NMOS, for example, has a density advantage over bipolar. but CMOS gates contain more devices than their NMOS counterparts. Bipolar design innovations, such as walledemitter structures, allow bipolar densities to keep pace with CMOS.

One factor working against CMOS is that architectural and logic design concessions must often be made to improve speed; these compromises in turn reduce functional density. A case in point is the problem of CMOS gate width - CMOS gates tend to become slower as more inputs are added. Δ designer, then, might be tempted to replace a logic implementation that uses multiple-input NOR gates with one having only two-input NOR gates, thus improving performance but increasing the number of gates and the die size.

Although CMOS functional density is no greater than that of bipolar, it may be possible, in some cases, to make a larger die and pack a greater number of logic functions using a CMOS process. The reason for this is lower power consumption: it's much easier to meet package power limits with CMOS than with bipolar. **Drive** - Bipolar gates have somewhat better drive characteristics than CMOS gates, particularly when the line being driven is capacitive. This superiority holds both for drive within a chip and for drive between chips.

Transmission line effects -Because new CMOS parts have edge rates approaching those of bipolar parts. CMOS users are now encountering transmission line effects similar to the ones that have plaqued TTL designers for years. The problem is somewhat less severe than that for the highest speed TTL families, due to the large voltage noise immunity of CMOS, and to the ESD diodes found in many CMOS parts, which tend to clamp reflections to either supply rail. Even so, the problem is serious enough to deserve the designer's attention.

At present, only bipolar technology offers a clean, predictable means of controlling transmission line effects in the highest-performance systems - this means is ECL I/O. The high-drive, low-impedance emitter follower outputs and the high-impedance differential amplifier inputs of ECL allow the user to series- or parallelterminate signals correctly, thus reducing reflections.

Noise immunity - Comparing the noise immunities of bipolar and CMOS yields no clear winner. At first glance it may appear that CMOS prevails, as its voltage noise immunity is roughly Vcc/2, while bipolar noise immunity is usually on the order of hundreds of millivolts. The conclusion one might draw from this comparison is deceptive for two reasons. First, energy noise immunity is more crucial an issue than voltage noise immunity. Because CMOS gate inputs have a much higher impedance than their bipolar counterparts, it takes much less noise energy to drive a CMOS gate into false

transition. Second, CMOS logic thresholds are set by both the supply voltage and ground; bipolar logic thresholds depend mostly on ground, making bipolar logic somewhat less susceptible to power supply noise. This is not to say that bipolar logic is more noise-immune than CMOS, but to point out that the often-alleged superiority of CMOS in this area is by no means clear-cut.

## Architectural implications for integrated circuits

The differences between bipolar and CMOS technologies have two major implications for the architecture of integrated circuits made with these processes:

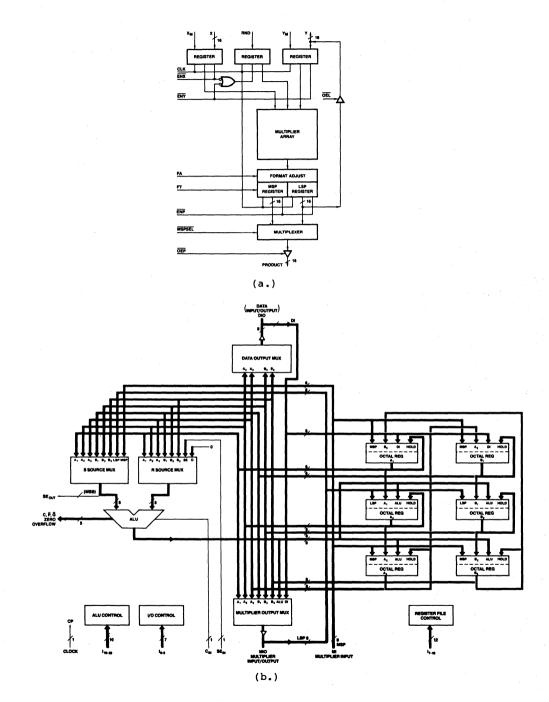

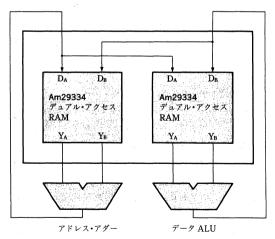

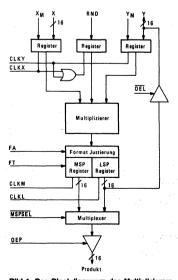

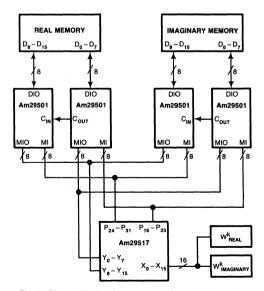

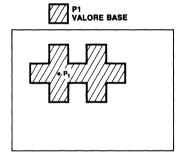

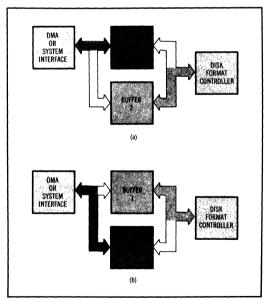

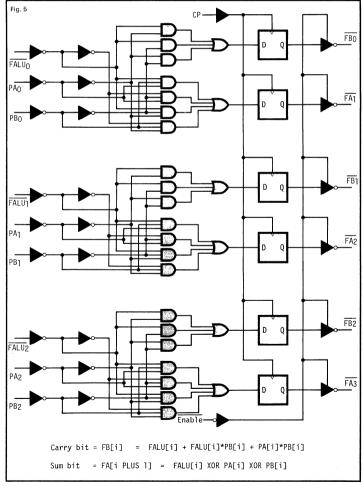

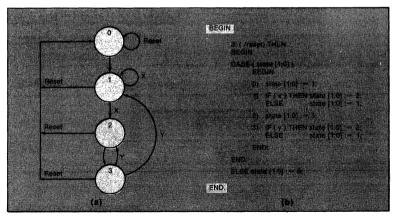

Local vs. global communication -Integrated circuit architectures can be divided into two broad categories. Into the first category fall those chips in which communication takes place primarily between neighboring circuit elements: these architectures feature local communication. An example of an integrated circuit that depends heavily on local communication is the Am29517A 16 x 16 combinatorial multiplier (fiq. 1 a). Most communication in this device takes place among neighboring computational elements in the multiplier's combinatorial core.

The second category includes those architectures in which widely-separated circuit elements talk to one another over buses; such devices feature global communication. The Am29501 Multi-Port Processor (fig. lb) is an example of a global communication architecture, with its many resources - multiplexers, registers, and arithmetic unit communicating over a large number of internal buses.

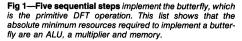

Fig. 1: Architectures using local and global communication. (a.) the Am29517A 16 x 16 multiplier -local communication; (b.) the Am29501A Multi-port Processor - global communication.

Due to the limited drive capability of its gates, CMOS is most suitable for integrated circuits that depend heavily on local communication. Bipolar excels in designs that need a significant amount of global communication at high speeds.

**Pipelining** - Because CMOS gates have speeds and drive capabilities that are somewhat more modest than bipolar, designers of CMOS integrated circuits often insert pipeline registers at strategic points in data and control paths to maintain a reasonable throughput rate.

Pipelining is a time-honored technique for improving system speed, and is not necessarily a disadvantage. Excessive pipelining, however, particularly in the middle of arithmetic elements, can create difficulties when programming signal processing algorithms for which intermediate results must be used as input operands later in the computation. The problem arises when an intermediate result that is needed as the input to the next operation is not available, but is instead stuck somewhere in the arithmetic element's pipeline. The user must solve this problem by either allowing time for the intermediate result to fall out of the pipe, thus reducing throughput, or by overlapping other operations, thus complicating system programming and control.

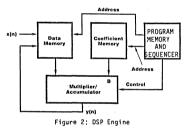

# Architectural implications for system design

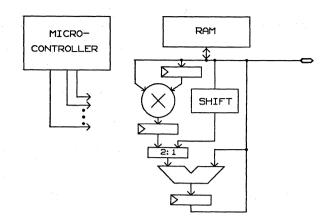

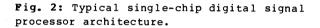

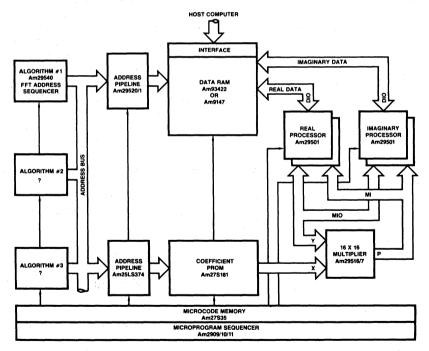

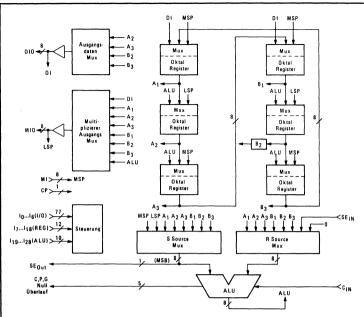

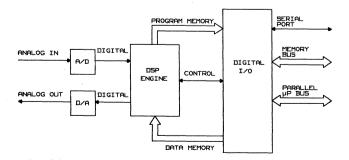

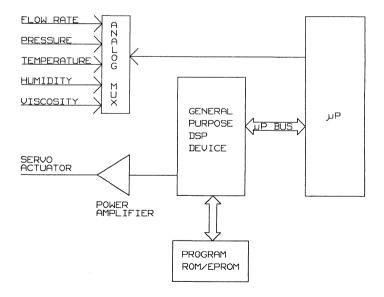

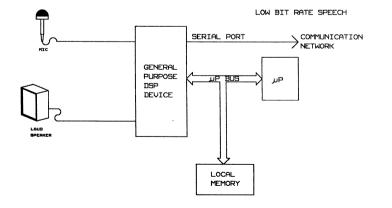

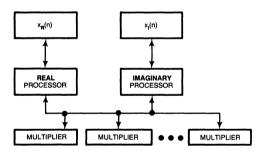

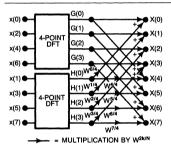

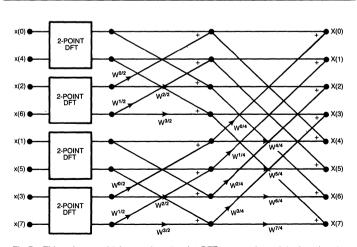

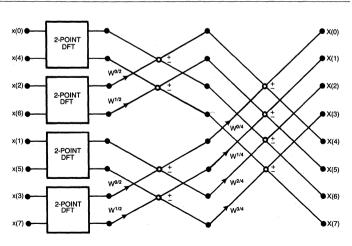

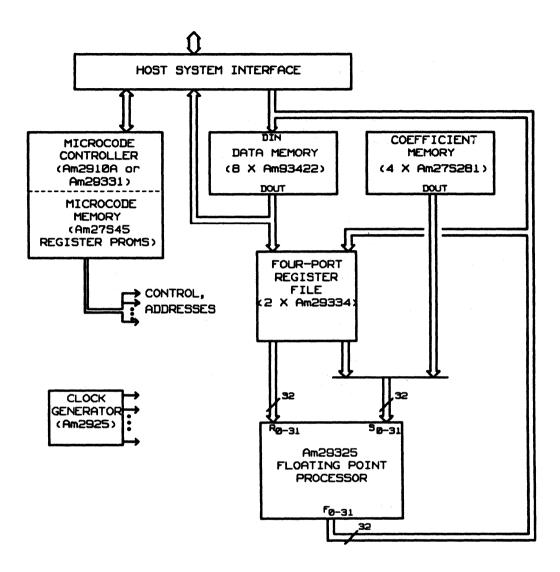

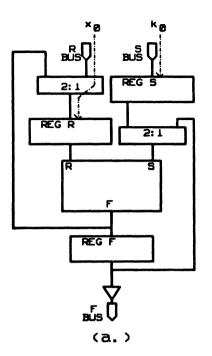

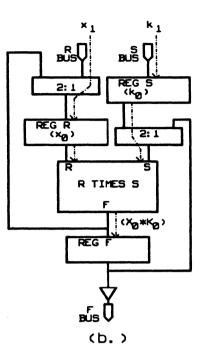

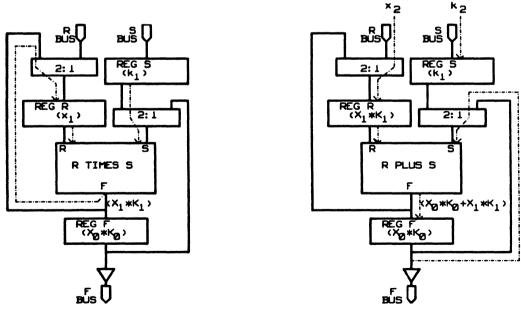

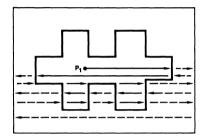

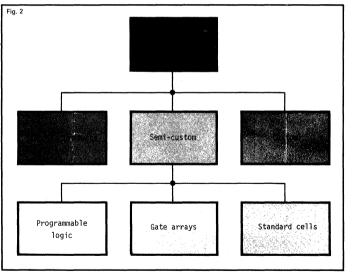

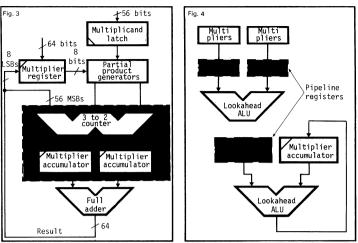

When creating a digital signal processing system, a designer can choose one of two approaches to hardware implementation. The first approach is to base the design on a single-chip digital signal processor, choosing from a small but steadilygrowing number of product entries; a typical single-chip digital signal processor architecture is shown in fig. 2. These processors are usually relegated to lower-speed applications, though the meaning of the phrase "lower-speed" is changing almost daily. The second approach is to use a multichip solution, designing the system with arithmetic/control building blocks configured in a manner that best suits the application. A typical multi-chip array processing system based on the Am29500 series of digital signal processing parts is shown in fig. 3.

While single-chip processors are becoming more sophisticated and powerful, they are still, in most cases, not capable of handling the more demanding digital signal processing applications. The multi-chip solution gives the user the ability to optimize the architecture, adding data paths and arithmetic elements as needed. The multi-chip solution in fig. 3, for example, is capable of performing a 1024-point complex-input FFT in 2 milliseconds; if a user must perform an FFT in less time, the necessary arithmetic elements and data buses can be added to increase throughput.

If the application is such that only a multi-chip solution is feasible, it is crucial that attention be given to minimizing signal delay between communicating components. Bipolar devices have the advantage in such because their higher gate systems, speeds and superior drive capability significantly reduce chip-to-chip delays. Designers building multi-chip solutions from CMOS must take particular care to assure that communication between components is fast enough to keep pace with the processing power of those components.

Fig. 3: Typical multi-chip digital signal processor architecture, using the Am29500 DSP family.

4/3

#### Conclusions

There is little doubt that CMOS technology is a worthy competitor to bipolar, and that its infuence and capabilities will grow as time goes on. CMOS brings moderate-to-high performance digital signal processing to applications whose lower power and cooling requirements preclude the use of bipolar technology.

It must be stressed, however, that the reports of bipolar's death are greatly exaggerated. Bipolar still offers higher speeds and greater architectural flexibility than CMOS, and will continue to do so for the forseeable future.

#### Bibliography:

Downing, P., Gwozdz, P., and New, B. "Denser Process Gets the Most Out of Bipolar VLSI," **Electronics**, June 28, 1984, pp. 131-133.

Bursky, D. "CMOS Processes Shrink Geometries, Pick up Speed for RAMs, Multipliers," **Blectronic Design**, Vol. 32, No. 9, 1984. A HIGH PERFORMANCE CMOS PROCESS FOR THE NEXT GENERATION EPROM

Jih Lien, Steve Longcor, K.Y. Chang, Lewis Shen, Pete Manos, David Chan, Tien Lee, and Sucheta Nallamothu

> Advanced Micro Devices Sunnyvale, CA 94088

#### ABSTRACT

A high performance CMOS process has been developed for the fabrication of the next generation EPROM family. The effective channel length of the EPROM transistor is approximately 1.0 um, with the gate and inter-poly oxide thicknesses, and junction depths scaled accordingly. Using this transistor, the cell size can be scaled to less than 20 um<sup>2</sup>. By utilizing state-of-the-art lithography, dry etch, and glass reflow technologies, a one megabit EPROM can be fabricated. With proper shrinking of the dimensions, the cell can be reduced to approximately 12um<sup>2</sup>, demonstrating that this process is sufficient for future EPROM's in the multi-millionbit range.

#### INTRODUCTION

Recent advances in NMOS technology have brought EPROM manufacturing to the 512Kb level [1]. An experimental NMOS 1Mb EPROM has also been presented [2]. The high power consumption of NMOS circuits limits the application of very high density NMOS memory chips in future generation microprocessors and computer systems. On the other hand, CMOS circuits have the advantage of low power consumption and high noise margin, making them especially suitable for high density design. Furthermore, as the feature size shrinks, the speed performance of CMOS circuits begins to improve. At the megabit level the speed of a CMOS EPROM is comparable with or even superior to its NMOS counterpart.

Latch-up susceptibility has been a basic problem for CMOS circuits, which becomes even more serious when high voltages and currents are present. Using a  $p^-$  epitaxial layer on a  $p^+$  substrate can increase the holding current significantly, but there are still several avalanche-induced latch-up triggering modes which cannot be corrected by using epi wafers. Design and layout techniques are used to remedy these problems and ensure safe operation of the circuits.

In this paper, we will describe our CMOS process, show memory device characteristics, and present methods of preventing latch-up triggering.

#### FABRICATION TECHNOLOGY

Primary considerations for the development of this CMOS process were: (a) maximum compatability with present NMOS EPROM processes, (b) suitability for high-volume production, and (c) shrinkability for future multi-million-bit level designs. An n-well process is the logical choice for an EPROM product and allows the desired NMOS compatibility. The  $p^-$  type starting material has the same resistivity as the previous generation NMOS process.

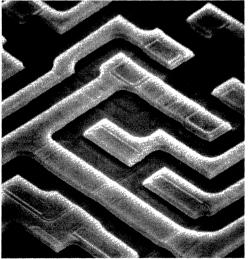

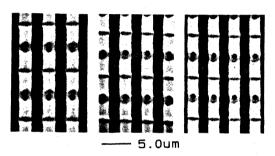

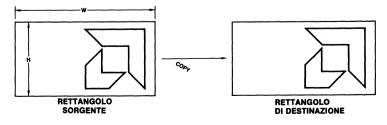

Table 1 shows the key features of this process. A conventional LOCOS isolation scheme is used, with the field oxide thickness scaled for small cell size. The EPROM transistors fabricated in this process are conventional double-poly stackedgate structures. They are derived from proven NMOS EPROMs by appropriate scaling of device dimensions. An anisotropic dry etch process is important for the definition of this double-poly structure. Figure 1 shows a cross-sectional view of the stacked-gate structure. Figure 2a shows the top view of a portion of the memory array using a cell of approximately 20um<sup>2</sup> Figures 2b and 2c are similar views of the 90% ( $16um^2$ ) and 80% ( $12um^2$ ) reductions respectively. A low temperature glass reflow module is used to improve the metal step coverage over contacts. An antireflection coating is needed for improved metal line definition.

A 21-stage ring oscillator with a fan-out of one has been used for the evaluation of this process. At  $V_{DD} = 5V$  the gate delay is 280 ps and the corresponding speed-power product is 0.031 pJ.

#### MEMORY TRANSISTOR CHARACTERISTICS

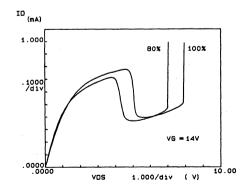

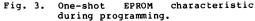

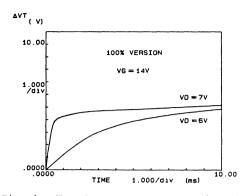

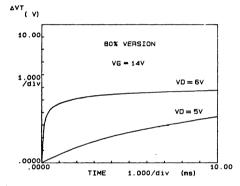

The EPROM transistors described above have been fully characterized under read and program conditions. Device sizes suitable for memory cells as small as  $12 \text{ um}^2$  have been studied. Figure 3 shows one-shot  $\rm I_{DS}$  vs.  $\rm V_{DS}$  curves during programming for the 100% and 80% sizes. Both curves indicate critical programming (drain) voltages of less than 5 volts: they could be programmed using  $V_{\rm DD}$  = 5V. Instead of sacrificing programming speed to achieve 5 V-only operation, optimal voltages are applied to both control gate and drain. Figure 4 clearly shows the importance of drain voltage in determining  $\Delta^V \eta_{\rm p}$  in the 0-5ms time range. An on-chip voltage pump provides a gate voltage larger than V<sub>pp</sub>. The voltages are regulated by circuit techniques to prevent damage to the memory transistor, selecting programming in the hot-electron injection region rather than in the impact ionization breakdown region.

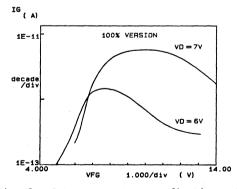

As can be seen from Figure 3, drain voltages of 7V for the 100% version and 6V for the 80% version are safely below the breakdown region. Punchthrough voltages (with V  $_{\rm G}$  = 0.2V) for unprogrammed EPROMs are > 7.5V for the 80% version and > 10V for the 100% version. Figures 4 (100%) and 5 (80%) show that the desired programming speeds have been achieved under these conditions. The optimum gate voltage can be determined by measuring programming speeds or by studying gate current vs. floating gate voltage curves (see Figure 6). Peak injection current results from a  $V_{\rm FG}$  near 10V, corresponding to a control gate voltage of approximately 14V. Note that during actual programming, the gate current will rapidly approach zero as charge collects on the floating gate. The drain voltage supplied by regulating circuitry will also rise somewhat as programming proceeds.

Given the similarity between the EPROM transistors produced by this process and their proven NMOS counterparts, high product reliability should be expected. In particular, measured charge loss characteristics are similar to 512K NMOS EPROM transistors (which demonstrate data retention far in excess of ten years).

#### LATCH-UP PREVENTION

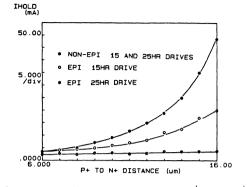

High voltage operation during programming requires special care in process development, circuit design, and layout to prevent the occurence of latch-up. Figure 7 shows the holding current as a function of  $p^+$  to  $n^+$  spacing. The use of  $p^-$  epi on  $p^+$  substrate offers significantly higher holding current for large  $p^+$  to  $n^+$  spacing, but is ineffective at small spacing. Epi is useful only when proper layout rules are followed in the design. The effect of n-well implant drive time is also shown. In order to minimize n-well side diffusion, thinner epi is generally preferable to longer well drives for achieving the desired relationship between well depth and  $p^-$  layer thickness.

Epi wafers provide higher holding current and prevent the CMOS circuits from permanently latching-up, but do not prevent the occurence of triggering (transient latch-up). On the other hand, epi wafers are more vulnerable to  $V_{\rm SS}$  line noise and gate noise because the lateral NPN transistor has higher current gain. Triggering does not always damage the device but causes malfunction of the circuit.

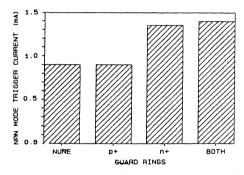

An inverter can be triggered by substrate current from a neighboring nchannel transistor even at a distance of  $400\,\mathrm{um}$ . During programming, the total substrate curent generated by the EPROM array can be as high as 1-2 mA, which poses a danger of triggering nearby peripheral circuits. Double guard rings are provided as current sinks around the array. The inner p<sup>+</sup> guard ring collects substrate current. The outer n<sup>+</sup> guard ring serves as a second collector to divert electrons that would otherwise flow into the n-well. A 50% reduction in substrate current was observed by using double guard rings.

As a second protection, guard rings were also applied around selected peripheral circuits to avoid possible triggering induced by substrate current. An  $n^+$ guard ring around the p-channel transistor increases the NPN mode triggering current significantly and is more effective in preventing substrate current-induced triggering than a  $p^+$  guard ring around the nchannel transistor (see Figure 8).

#### SUMMARY

A high performance CMOS process has been described. Fabrication of EPROM arrays and characterization of the memory cell transistors demonstrate shrinkability suitable for multi-million-bit level circuits. Latch-up susceptibility of CMOS circuits can be prevented by using suitable design and layout techniques. The simplicity of this process makes it compatible with volume production.

#### ACKNOWLEDGEMENT

The authors would like to acknowledge the support of John Stanczak in test chip design and layout, Al Miller in electrical measurement, Yasmin Nawaz in photolithography development, and the Fab VII staff in processing the wafers. Consultations with the EPROM design group during the preparation of this paper are highly appreciated.

#### REFERENCES

- D. Rinerson, M. Ahrens, J. Lien, B. Venkatesh, T. Lin, P. Song, S. Longcor, L. Shen, D. Rogers, and M. Briner, "512K EPROMS," ISSCC Digest of Technical Papers, Feb. 1984, p. 136.

- [2] K. Okumura, S. Ohya, M. Yamamoto, T. Watanabe, Y. Shimamura, and M. Kikuchi, "A 1Mb EPROM," ISSCC Digest of Technical Papers, Feb. 1984, p. 140.

— 0.5um

Fig. 1. SEM cross section of the stackedgate structure.

Fig. 2. Top views (left to right) of the (a) 100%, (b) 90%, and (c) 80% EPROM arrays.

Table 1. Process Features (100% Version)

silicon gate n-well CMOS two polysilicon layers

| L <sub>eff</sub> (min.) 1.0                                                                                                                                                                 | Jum  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Weff (min.) 0.9                                                                                                                                                                             | ) um |

| gătê oxide 250                                                                                                                                                                              | A    |

| interpoly oxide 300                                                                                                                                                                         | ) A  |

| field_oxide 5500                                                                                                                                                                            | 5 A  |

| (n <sup>+</sup> ) Ø.2                                                                                                                                                                       | 2 um |

| X (p <sup>+</sup> ) Ø.35                                                                                                                                                                    | 5 um |

| $\begin{array}{cccc} X_{1} & (n^{-}) & 0 & 2 \\ X_{1} & (p^{+}) & 0 & 3 \\ X_{2} & (n-well) & 3 & 3 \\ V_{L} & (n) & 0 & 6 \\ V_{L} & (p) & -6 & 5 \\ V_{L} & (ppppy) & -6 & 5 \end{array}$ | 5 um |

| $V_{+}^{J}(n)$ 0.6                                                                                                                                                                          | 5 V  |

| V <sub>+</sub> (p) -0.9                                                                                                                                                                     | v    |

| Vt (EPROM) 1.0                                                                                                                                                                              | V    |

| speed-power product 0.031                                                                                                                                                                   | L pJ |

| gate delay 280                                                                                                                                                                              | Ø ps |

- IEDM 84

Fig. 4.  $V_{T}$  change vs. programming time (100% version).

Fig. 5. V<sub>T</sub> change vs. programming time (80% version).

Fig. 7. Holding current vs. p<sup>+</sup> to n<sup>+</sup> distance.

Fig. 8. NPN triggering current for different guard rings.

Fig. 6. Gate current vs. floating gate voltage.

# Surface Mount Technology, Plastic Chip Carrier Trends

By Michael C. Lancaster, Manager, Advanced Package and Materials Development Group, Advanced Micro Devices, Inc., Sunnyvale, Calif.

The word is being spread all over the world through well-attended seminars and articles in trade journais that surface mount technology is the packaging revolution of the 1980s. By now most engineers and managers under the electronics umbrella know of the reasons and need for surface mount technology. The impact to systems houses of increased board density, elimination of costly through-holes, fewer board lavers, and the ease of automation of populating boards have been well publicized. So why this meteoric interest and demand?

In the passive component field, surface mount resistors and capacitors have been available for a decade, most notably in Japan. Driven by consumer-oriented products, the need to reduce product size, weight, and cost has been of paramount importance. Since these products primarily consist of analog circuitry. treating radio frequency (RF) signals instead of digital codes, resistors, and capacitors are required in great numbers in resistor-capacitor inductance networks. It is estimated that more than 30 percent of the Japanese consumption of passive components (63 billion units) is already of surface mount (SM) configuration. In addition, because most Japanese companies are vertically integrated, surface mountable IC packages have been developed for inclusion in about 16 percent of their products. However, this approach resulted in a proliferation of outlines with no attempt at standardization.

When a need for surface mount components was identified in the

United States, manufacturers of passive components quickly responded to avoid orders going overseas. Standards were developed for component values and physical size. Today a full range of surface mount resistors from  $10\Omega - 2.2M\Omega$  of one size (1.6  $\times$  3.2  $\times$  0.6mm) and surface mount capacitors 680 pF-0.5µF are readily available. The lack of standardization and the horrendous capital investment required by semiconductor suppliers to tool and internally handle SM configurations have resulted in a reluctance to "go it alone." Thus frustration from lack of availability of SM IC's has been building as total conversion to surface mount technology has been severely hampered. Companies such as Delco have played a critical part in forcing a standard between major suppliers and in turn an industry-registered family outline.

Developed out of Texas Instruments' initial design concepts, standard outlines are in the final stages of approval by the Joint Electronic Device Engineering Council (JEDEC). With standards in place and demand from computer and telecommunication industries for SM components now being added to these initial consumer applications, the rush for SM IC availability and secured source is on.

Components surface mounted on a thermal test board.

Several plastic chip carrier packages show variations in design and actual mounted capability.

#### IC Package Availability

The main and earliest motivation for surface mount technology in IC packaging has come from government contracts. In fact, the long standing flatpack which appeared in the late 1950s is still widely used in military applications, utilizing surface mount technology on ceramic substrates. The three contracts awarded in the late 1970s to RCA, Hughes, and Texas Instruments to develop leadless chip carriers was the first major thrust to find an alternative to the flatpack that would satisfy MIL-Std-883 and 38510. The family of packages developed served as a useful impetus to piece-part and socket manufacturers, test handler suppliers, and users to set industry standards of package design and PCB interface.

As a result, most semiconductor suppliers now offer leadless chip carriers as a package option to their full range of products, and thus, the first widely available surface mountable package.

Despite the availability of this surface mountable family, the expected rush of orders did not materialize. This could be attributed to two things. First, the packages were two to three times more expensive than their equivalent ceramic dual inline packages and five to six times more than the plastic package. Furthermore, the expected cost reduction to the single layer and metallized package (SLAM) never materialized because of the unreliability of the cap seal.

Second, the thermal mismatch between the ceramic piece-part and a polyimide or epoxy PC weakened the solder joints and was found to be an unacceptable method of attachment for lead counts of 44 and above. For these applications, sockets were needed which negated surface mount technology and added approximately one dollar to the cost of each part.

For 48 leaded parts and above, however, where there was not an acceptable dual in-line package (DIP) alternative to the multilayer packages, these ceramic chip carriers have found a niche in the marketplace. The superior electrical parameter performance to be achieved with a leadless chip carrier (LCC) and the lower cost than multilaver DIPs have outweighed the additional socket costs. However, even this market has been eroded recently with improved plastic DIP processing techniques up to 64 lead devices.

The salvation for this SM requirement with thermal compliance to a

variety of substrates has been to sacrifice hermeticity and accept a plastic package.

#### PLCC and SO Packages

Two plastic surface mount package configurations have been considered. These are the plastic leaded chip carrier family, also known as a PLCC, PCC, or quadpak, and the small outline (SO) family. To understand the development of these packages, the derivation of the outline history needs to be expounded.

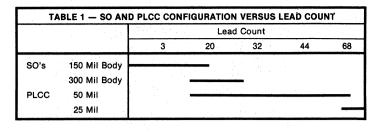

The oldest and therefore more established package of the two is the SO. Originally developed in Europe by Philips, the SO package (or Swiss Outline as it was termed, displaying its European origin) found first application in discrete devices also adopted by Motorola. As the surface mount requirements in consumer and telecommunications industries mirrored the Japanese approach, IC's with 14 and 16 leads were packaged in SO. These had a 150 mil wide body with dual in-line leads with individual spacing of 50 mils with the leads bent in a gull wing fashion or a butt joint. The package size of the SO was approximately half its DIP counterpart. Recent trends have been to extend lead counts up to 28 with increased body widths up to 300 mils (table 1).

Texas Instruments has been the chief propounder of the plastic quad package. Originally developed for internal use, the package has found general acceptance in the industry. With few modifications, JEDEC recently accepted registration of the square package family and may soon be accepting the rectangular family.

PLCC, a late-comer compared to the SO package, has made significant in-roads in establishing itself as the standard. The configuration lends itself to accommodate very large scale integrations (VLSI) die with high lead counts and, perhaps more importantly, is compatible with the footprint established for LCC. Initial reliability data shows it to be comparable with the DIP with potential for improvement.

When determining the properties of the leadframe material to be used in DIP's or SO's, a compromise needs to be reached between a strong frame to minimize lead damage and a frame with good thermai properties. Unfortunately, for metals, the higher the thermal conductivity, the lower its mechanical strength (table 2). Since with PLCC the lead is wrapped under and locked in place under the package, there is little concern for subsequent lead damage and bending. Hence softer copper materials which have improved thermal characteristics can be used for the leadframe. A further consequence of utilizing a softer frame material is that the leadframe plastic pullaway created during the lead forming operation is minimized. Recently, questions have arisen concerning the reliability of the SO package because of the thin plastic body and narrow path from die to package body outline. This has been hotly contested by SO manufacturers?

There is an obvious need for the SO package, which will become increasingly popular for lead counts below 20. For more than 28 leads, it is clear the PLCC is presently the only viable SM package with at least a DIP reliability. There will be an overlap of technologies for lead counts of 20, 22, and 24. For semiconductor companies with large volumes of low lead count parts, it is in their interest to promote the SO package to as high a lead count as a marketplace is found. Companies that supply primarily high lead count products will extend the PLCC family to as low a lead count as there is a market (table 1).

Both Philips at their Surface Mount Technology Center in Milwaukee and Texas Instruments at their facility in Houston offer extensive surface mount technology training courses and capabilities for prototype SM on boards, naturally biased to SO and PLCC technologies, respectively.

The dynamic random access

memory (DRAM) market does not know whether to go guad or SO, and many companies are sitting poised to go either way depending on which way the big computer companies commit. For memory arrays, a dual in-line configuration is still the best for board routing and interconnection of the discrete memory modules. Quad packaging would force systems houses to another board layer (three instead of two), thus adding to costs. Texas Instruments proposes to adopt a modified SO package utilizing the "J" bend concept of the guad package and is being considered for their 256K and a further modified SO, but still 300 mil, for their proposed megabit. Here they are in conflict with Intel, which favors a 350 mil wide × 550 mil PLCC!

#### **High Lead Count Direction**

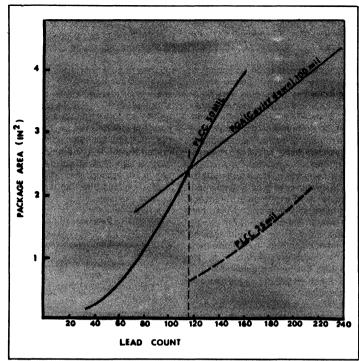

Is there a surface mountable package for lead counts in excess of 100? To partially answer this question, consider the package area versus lead count (figure 1). For lead counts of less than 100, the 50 mil lead-spaced PLCC shows the most effective use of board space, but for more than 100, the pin grid array (PGA) package is more efficient. Although this is not a surface mount part, it is already an established industry standard.

If the lead spacing on a PLCC is reduced to a 25 mil pitch, the PLCC immediately becomes the most attractive configuration, and furthermore, is compatible with surface mount technology. Before this configuration can be introduced, systems houses have to agree that they can accommodate wave or reflow soldering in pads of 25 mil pitch. One of the largest computer manufacturing companies recently announced that this is now possible. However, a further limitation is set by the semiconductor manufacturers and piece-part vendors.

For a 120-lead device, the leadframe stamping and discrete wire bond constraints on finger width and spacing dictate that the leads can converge toward the package center only to an envelope 500 mils square. This may be too large to accommodate die, especially since wire sweep could be a serious issue with the PLCC and wire lengths needing to be minimized.

An alternative would be to reduce frame thickness, which would make possible narrower fingers and spacing. The full implications of accomplishing this, however, need to be investigated. As for the military requirements for surface mountable hermetic packages, it is expected that an extension of the existing

|          | TABLE 2 — CONDU<br>FOR DIFFERENT | CTIVITY, STRENGT<br>MATERIALS AND |         |         | 8       |         |

|----------|----------------------------------|-----------------------------------|---------|---------|---------|---------|

|          | O                                | Tensile                           |         | θja°C/  | w       |         |

|          | Conductivity<br>BTU+Ft/Ft²+HR+°F | Strength<br>34 Hard               | 40L DIP | 48L DIP | 64L DIP | 68 PLCC |

| Alloy 42 | 8.8                              | 92                                | 66      | 72      |         |         |

| Olin 195 | 110                              | 76-84                             | 44      | 55      |         |         |

| Olin 194 | 142                              | 57-67                             |         |         | 35      |         |

| Olin 155 | 189                              | 48-58                             |         |         |         |         |

| Olin 151 | 197                              | 47-56                             |         |         |         | 37      |

ELECTRI•ONICS • December 1984

Figure 1 shows the PCB area occupied by package lead count.

leadless chip carrier family will be developed with either 25 or 20 mil pad pitch to satisfy the high lead count needs (table 1).

Talk of yet a lower pitch, 12.5 mils, has been suggested but will probably have to wait until the applications of the TAB technology is universally accepted after implementation in high lead count and VLSI fields. System houses may also have to develop alternatives to wave soldering.

#### **Response to Demand**

There has been hesitation on the part of semiconductor device suppliers in the United States to join the surface mount technology bandwagon and support their customer needs. They have been content to continue packaging IC's in the DIP format and develop another through-the-hole packaging concept (PGA) for higher lead count devices where the DIP format is impractical.

A notable exception to this has been Texas Instruments. Because of a captive application for their devices and the tight control over their packaging and interconnection technology, they have been able to develop the quad package through to production independent of other system houses.

The majority of semiconductor device manufacturers do not have captive applications and supply electrical components to the consumer, telecommunication, and computer markets. The reluctance to commit to surface mount technology has been largely due to a lack of industry standards. These are close to becoming corrected, and most companies are in a position to eagerly respond to surface mount technology demands. AMD, for instance, has anticipated the standards being approved and is well under way with the gualification procedures. The initial thrust has been to establish gualified subcontractor capability, but to provide in-house capability for expected high volume runners (44 and 68 lead) or when subcontractor tooling was not readily available (as in the case of 18 lead rectangular).

The requirements for tooling unfortunately has hit tool manufacturers just at the time when business was expanding because of a worldwide increase in demand for standard DIP packages. Thus an already desperate situation was exacerbated, pushing mold leadtimes out to 30-40 weeks.

Subcontractor assembly houses have been quick to see the potential increase in their business by supplying PLCC capabilities. In fact, not only have they offered assembly capability, but also leadframe availability. In the scramble for PLCC product capability, heavy demand will be placed on this, and availability of capacity will go to companies that have supported this tooling or have partaken in early production volumes.

Why have AMD and semiconductor device manufacturers taken this and similar approaches to surface mount technology? First, the cost savings to be obtained in converting are all at the level two of packaging. This is the systems board level and hence the major incentive is not with the supplier. This systemsdriven need resulted in uncertainty on the suppliers' part as to the seriousness of their vendors, the type, and industry uniformity of desired configurations.

Second, manufacturers have been pushing for an industry-wide agreement on standards before committing significant amounts of capital investment in tooling. To appreciate fully the need for standardization, consider for a moment the costs involved in providing even a modest capacity in PLCC. New mold and deflash, trim, and form equipment have to be purchased for each lead count, and both die attach and wire bond indexing carriages have to be modified. In the test area, burn-in sockets, electrical test sockets, and environmental handlers have to be purchased. This total investment in capital per lead count could exceed \$400,000. As for leadframe tooling, an initial etched leadframe source can be established for approximately \$20,000, but if volumes explode as some pundits predict, a stamping source must be established at a cost of \$120,000 per lead count.

Unfortunately, unlike DIP configurations in which one stamping tool can offer several cavity size options, the tight tolerances and geometry design considerations for PLCC frames dictate that one stamping tool only gives one cavity size. Some stampers will offer two, but this is

ELECTRI•ONICS • December 1984 •

the maximum, and some compromise in design is anticipated. Thus not only do leadframes have to be tooled for 10 different lead counts — 20, 28, 44, 52, 68, 84 square, and 18, 22, 28 and 32 rectangular — but maybe two or three cavity sizes as well. This in itself necessarily imposes international standardization and unprecedented cooperation between semiconductor device manufacturers and/or with leadframe suppliers to share this astronomical tooling cost, estimated at \$5 million.

#### **Component Demand**

Four years ago, the expected demand for LCC never materialized. Will the same thing happen this time? Perhaps not, for the reasons discussed below.