# M80-000 and M80-001 MODEL 80 MAINTENANCE MANUAL

Consists Of:

GENERAL DESCRIPTION

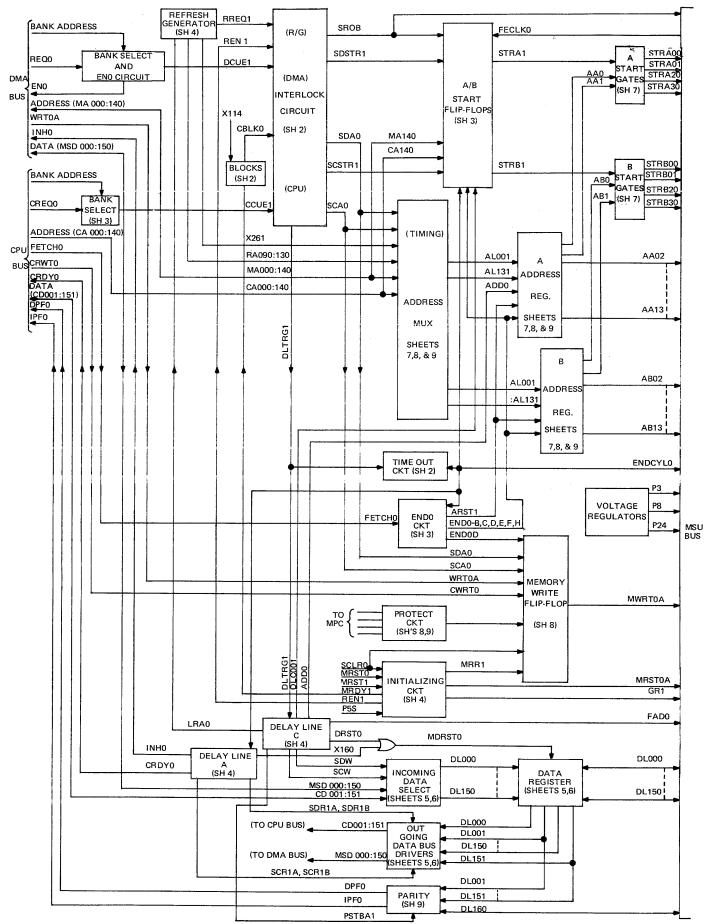

General Description

29-280A12

**PROCESSOR**

Processor Installation Specification Processor Maintenance Specification

01-053A20 01-053R01A21

**MEMORY**

**Memory Maintenance Specification**

02-247A21

**MEMORY PROTECT**

Memory Protect Controller Programming Specification Memory Protect Controller Installation Specification Memory Protect Controller Maintenance Specification 02-248A22 02-248A20 02-248A21

**SELECTOR CHANNEL**

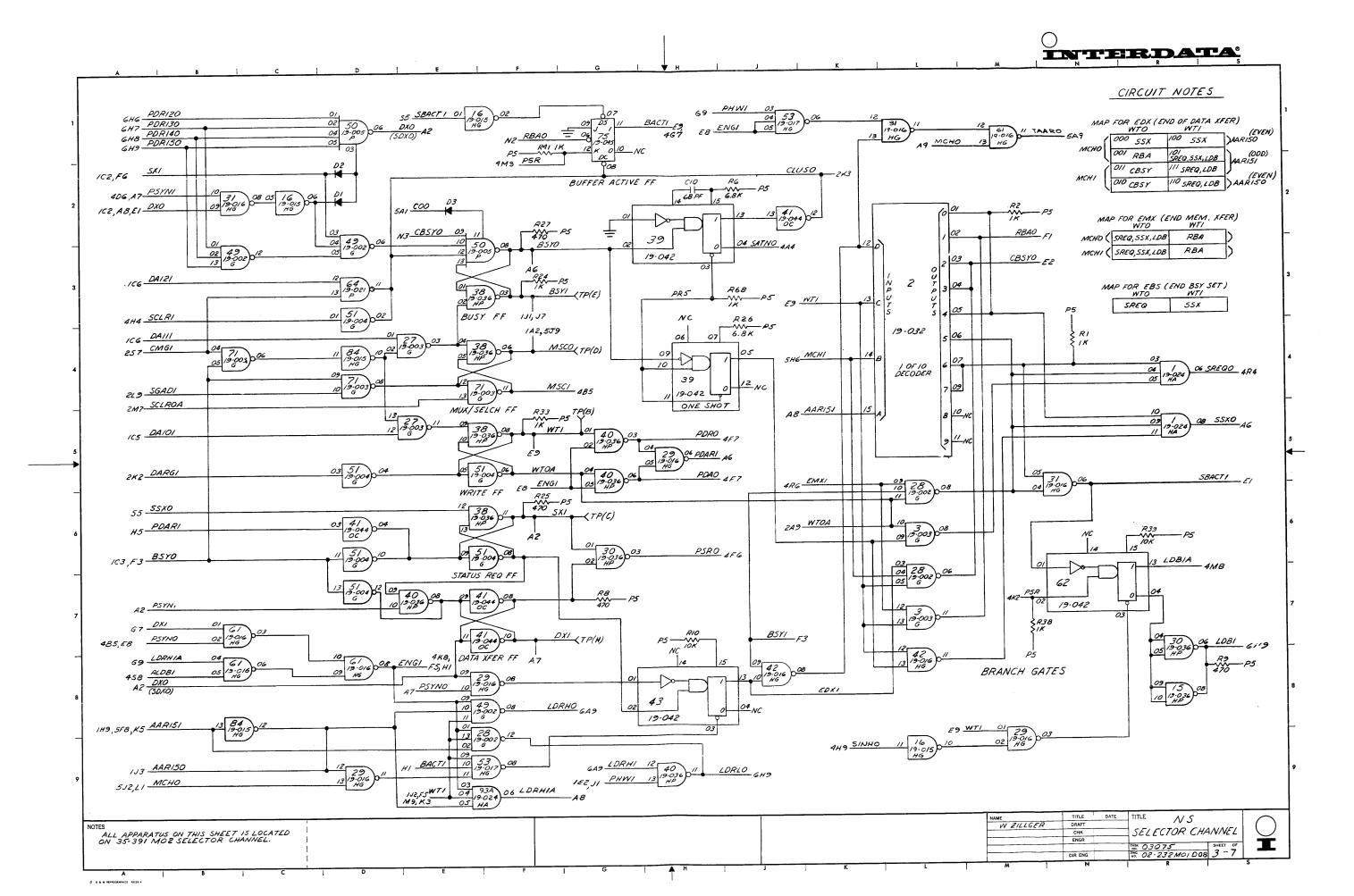

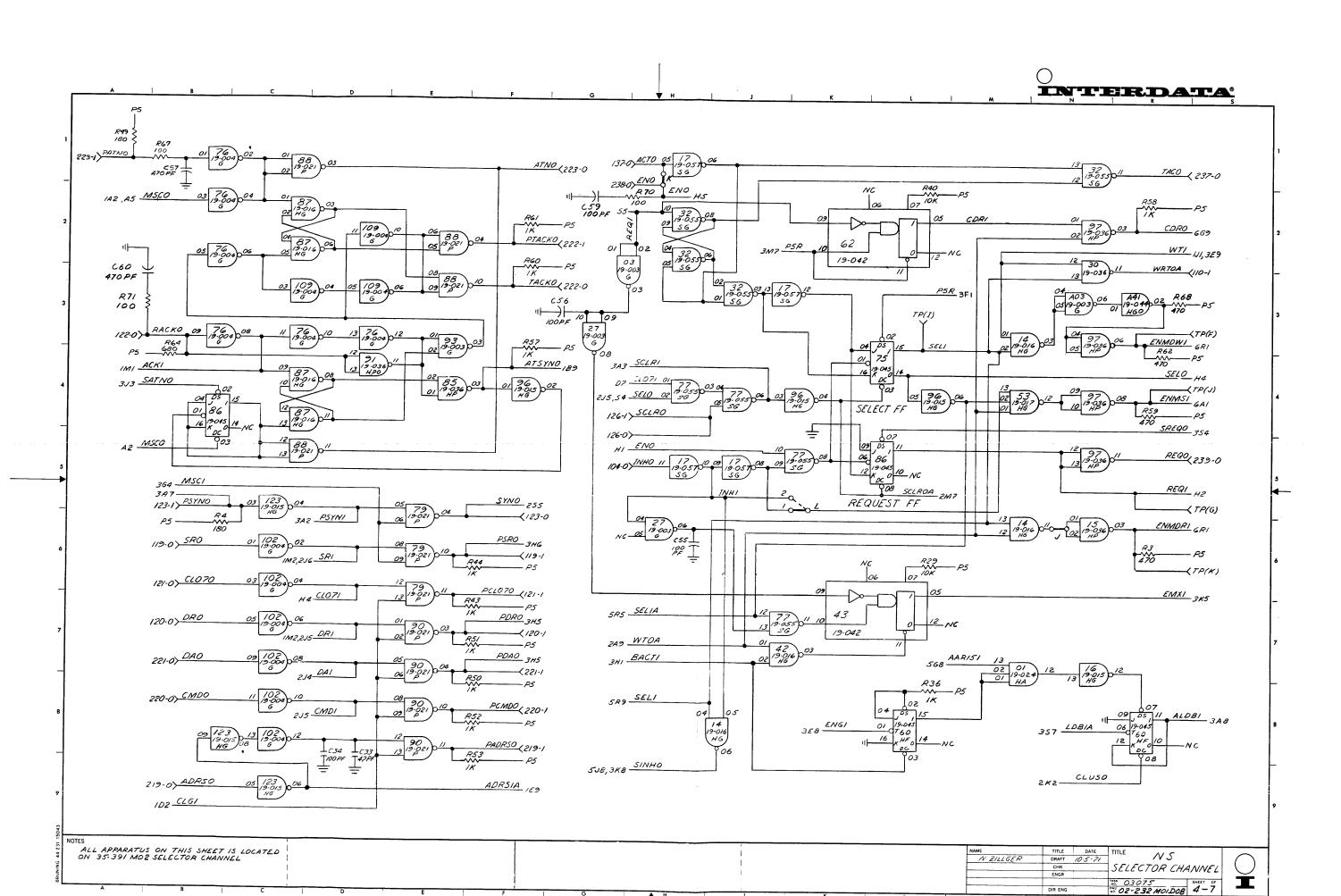

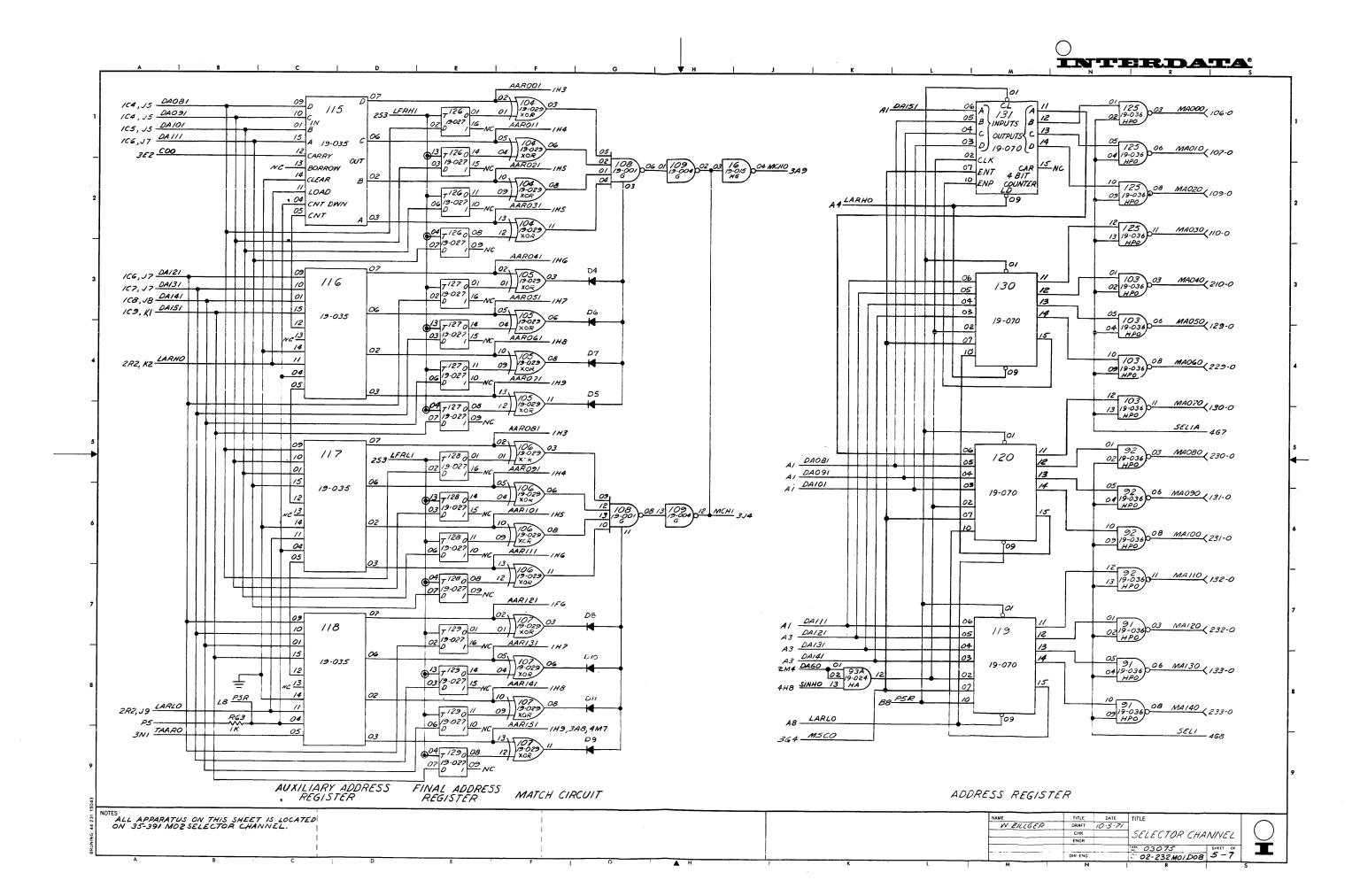

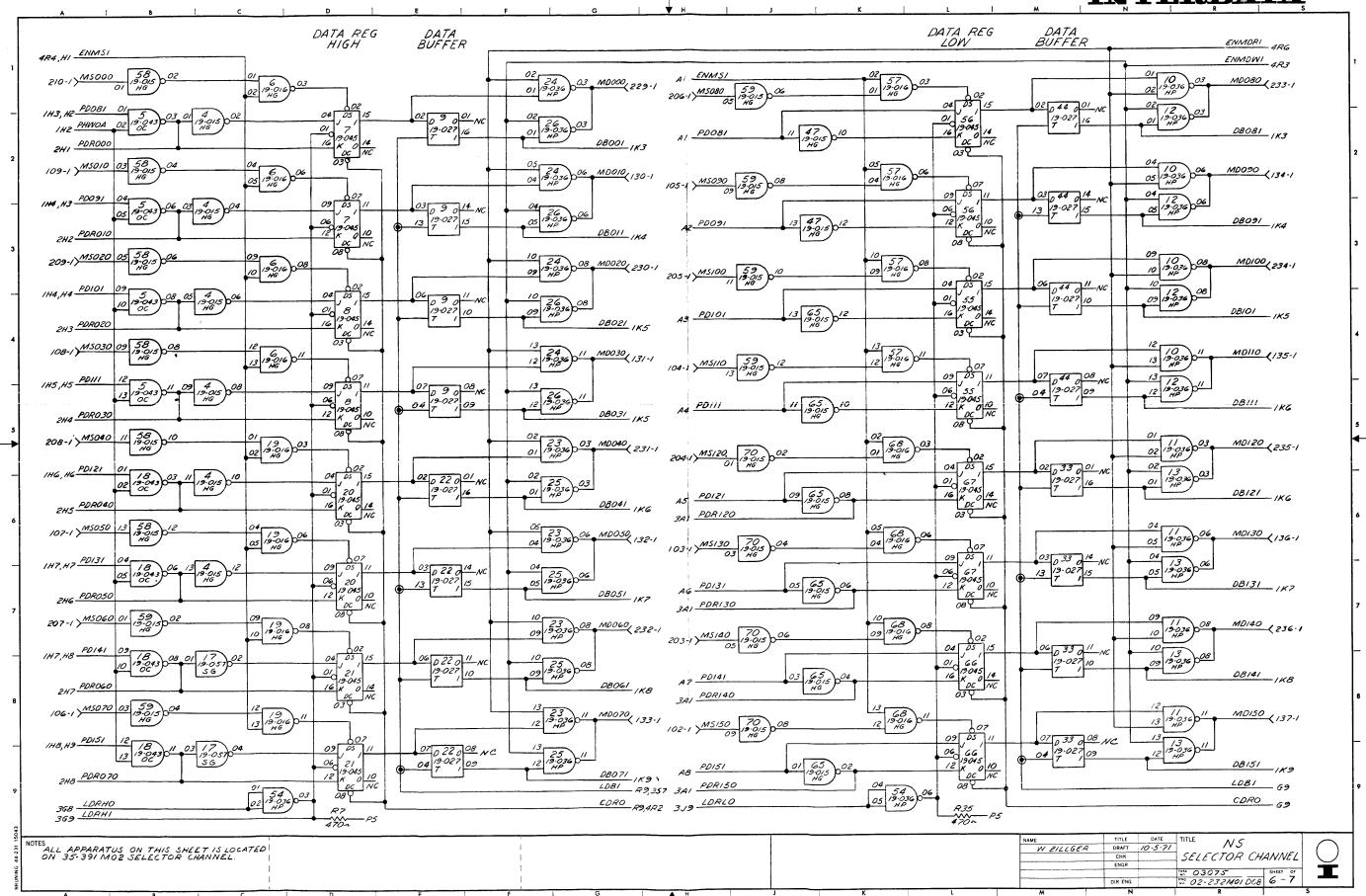

Selector Channel Installation Specification Selector Channel Maintenance Specification 02-232M01A20 02-232M01A21

**POWER SYSTEM**

**Power System Description**

02-261A12

**DRAWINGS**

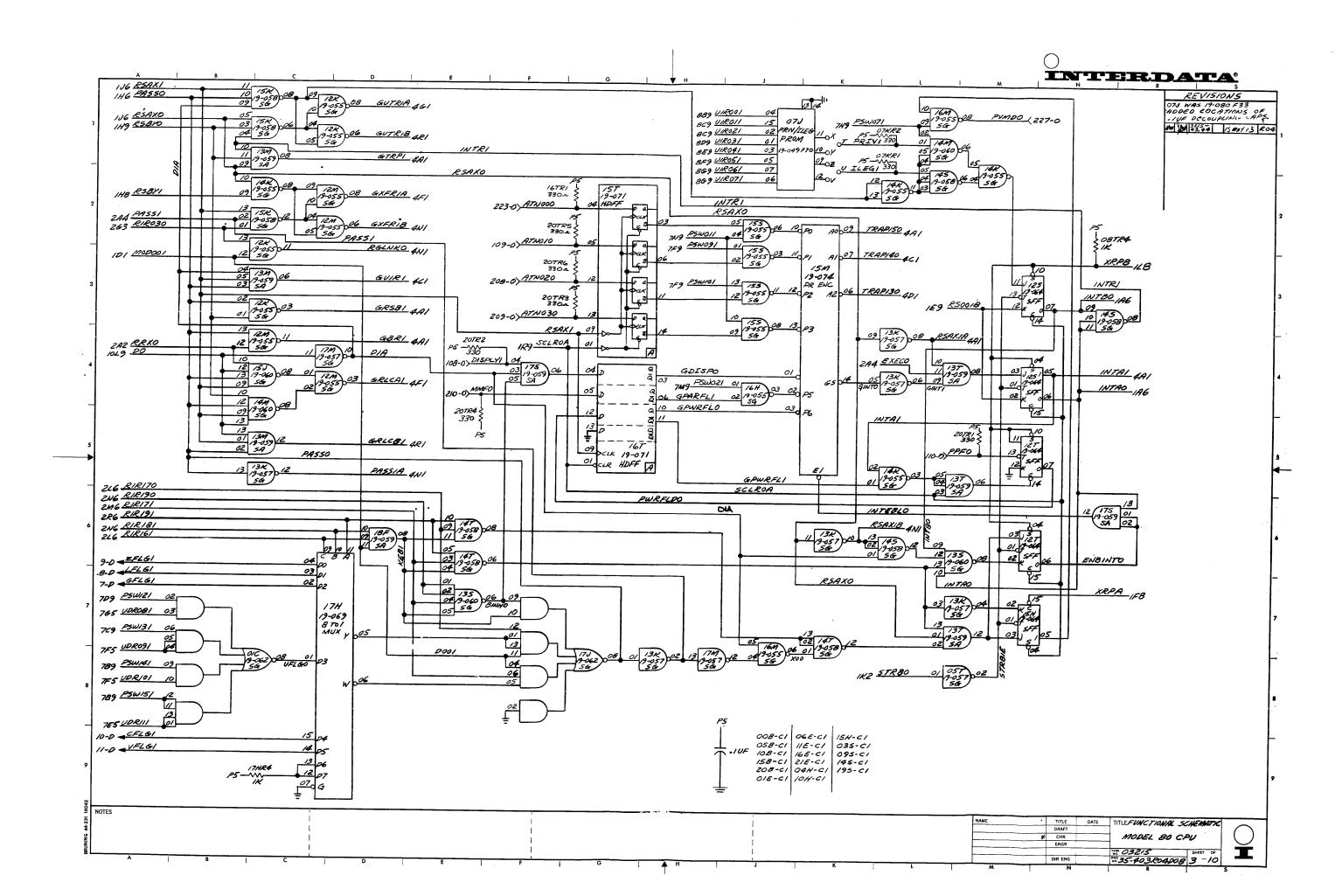

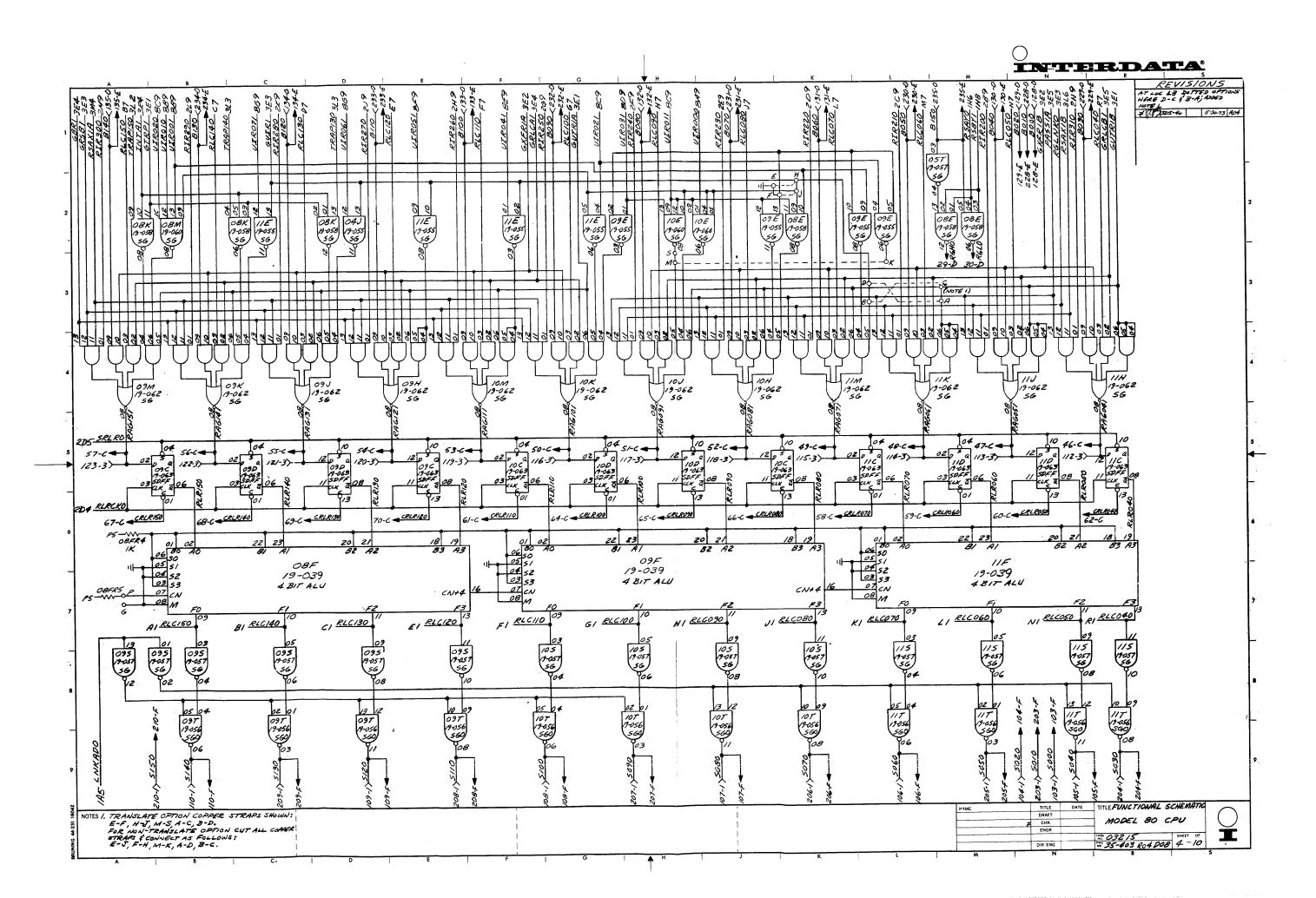

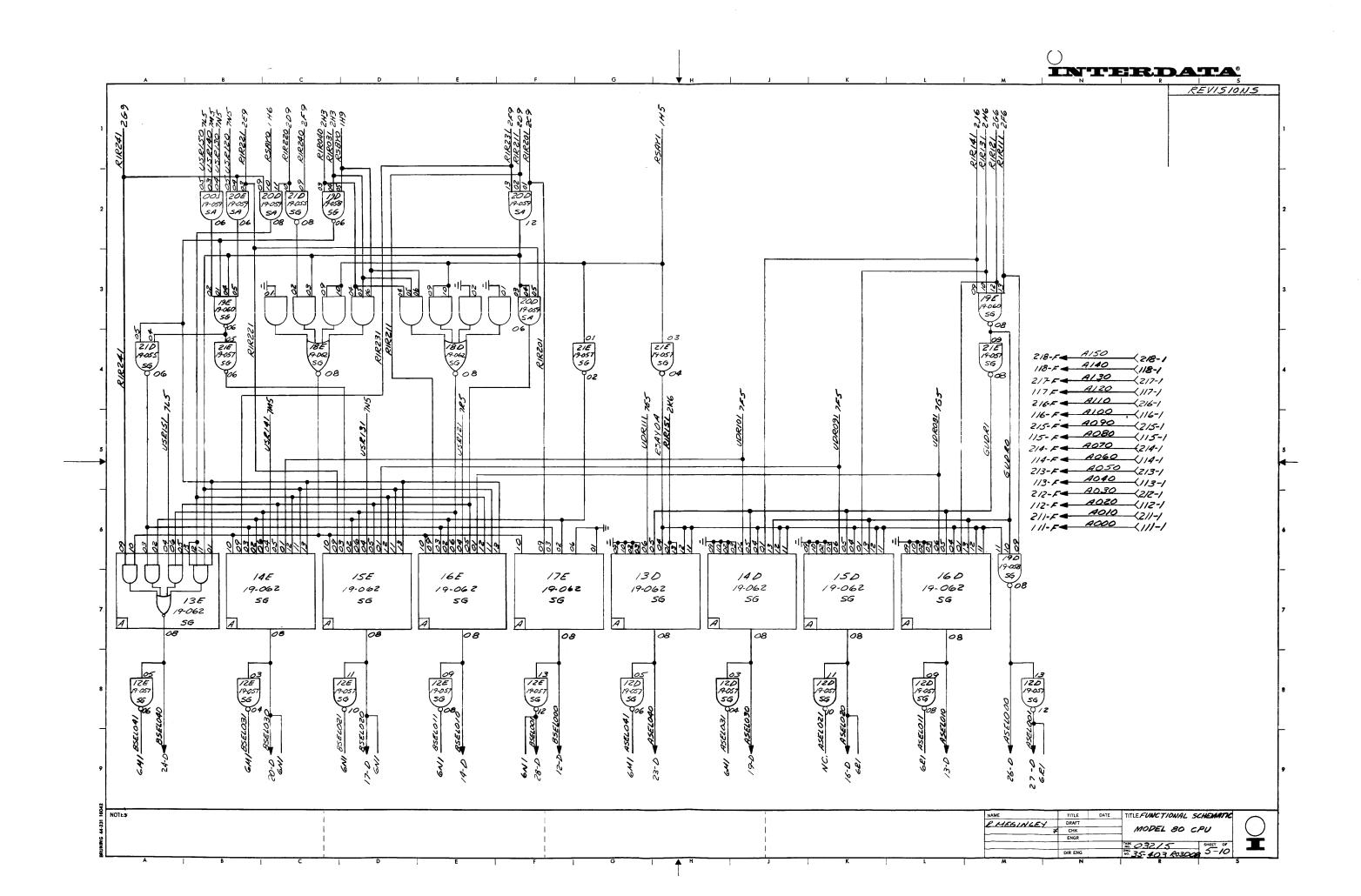

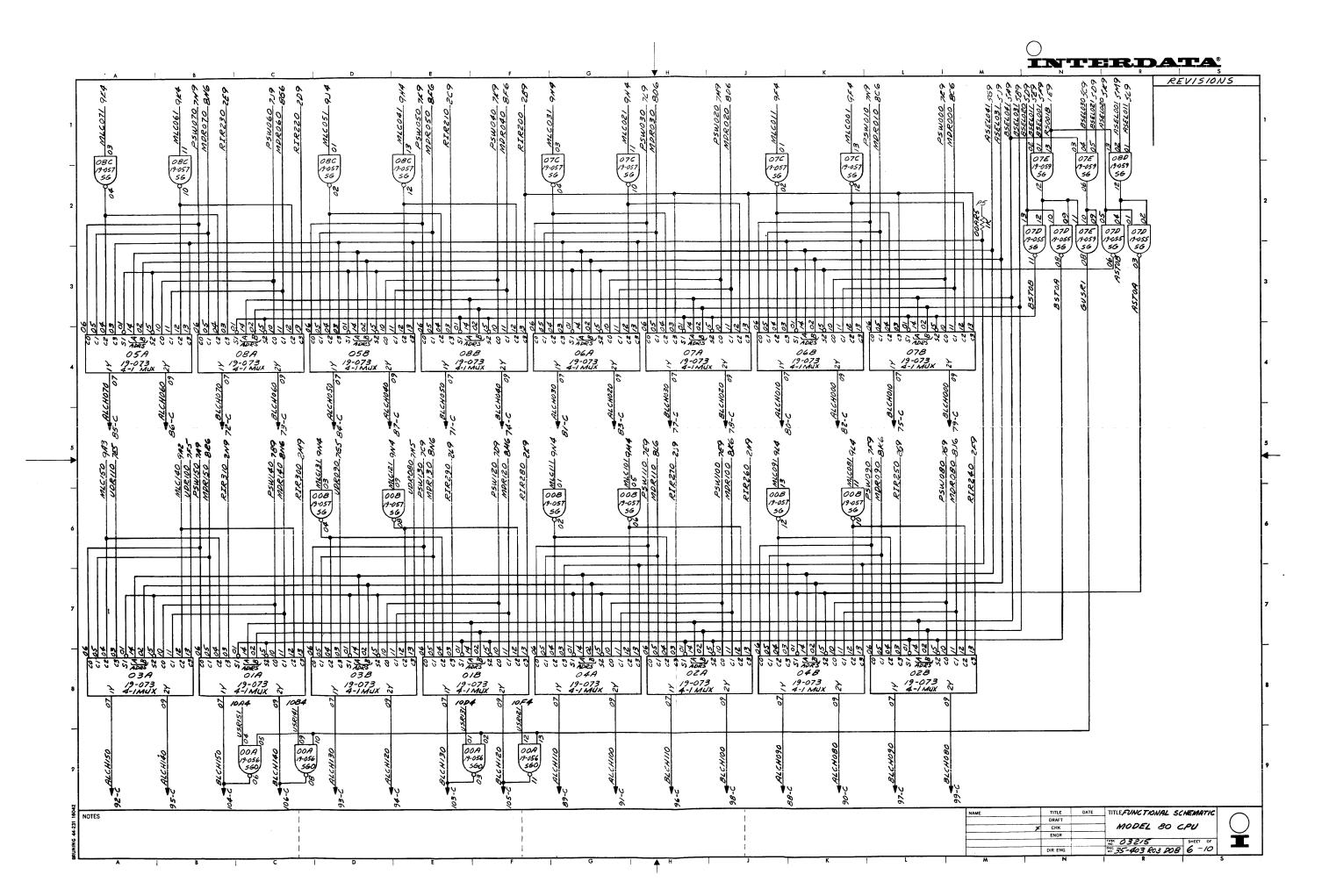

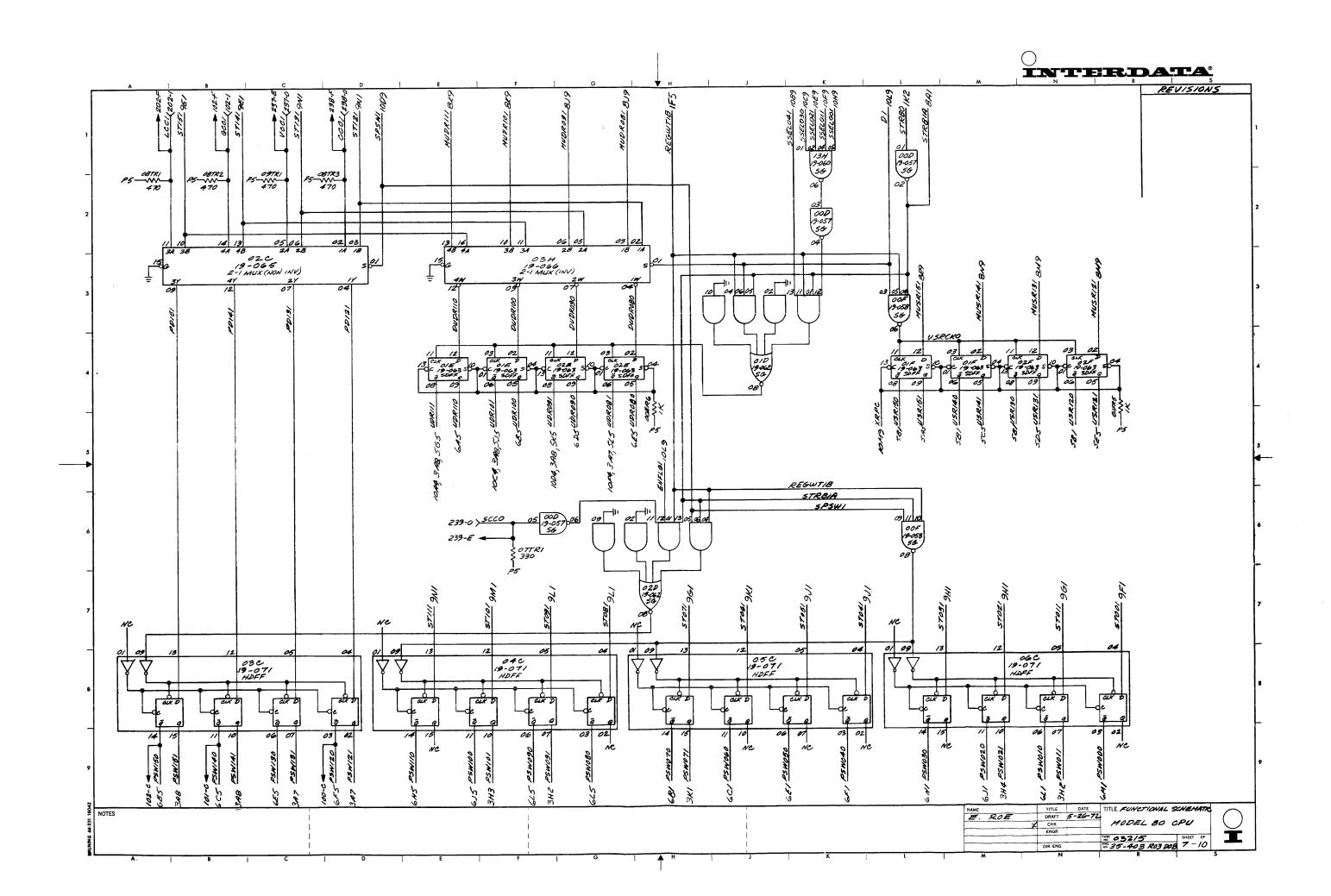

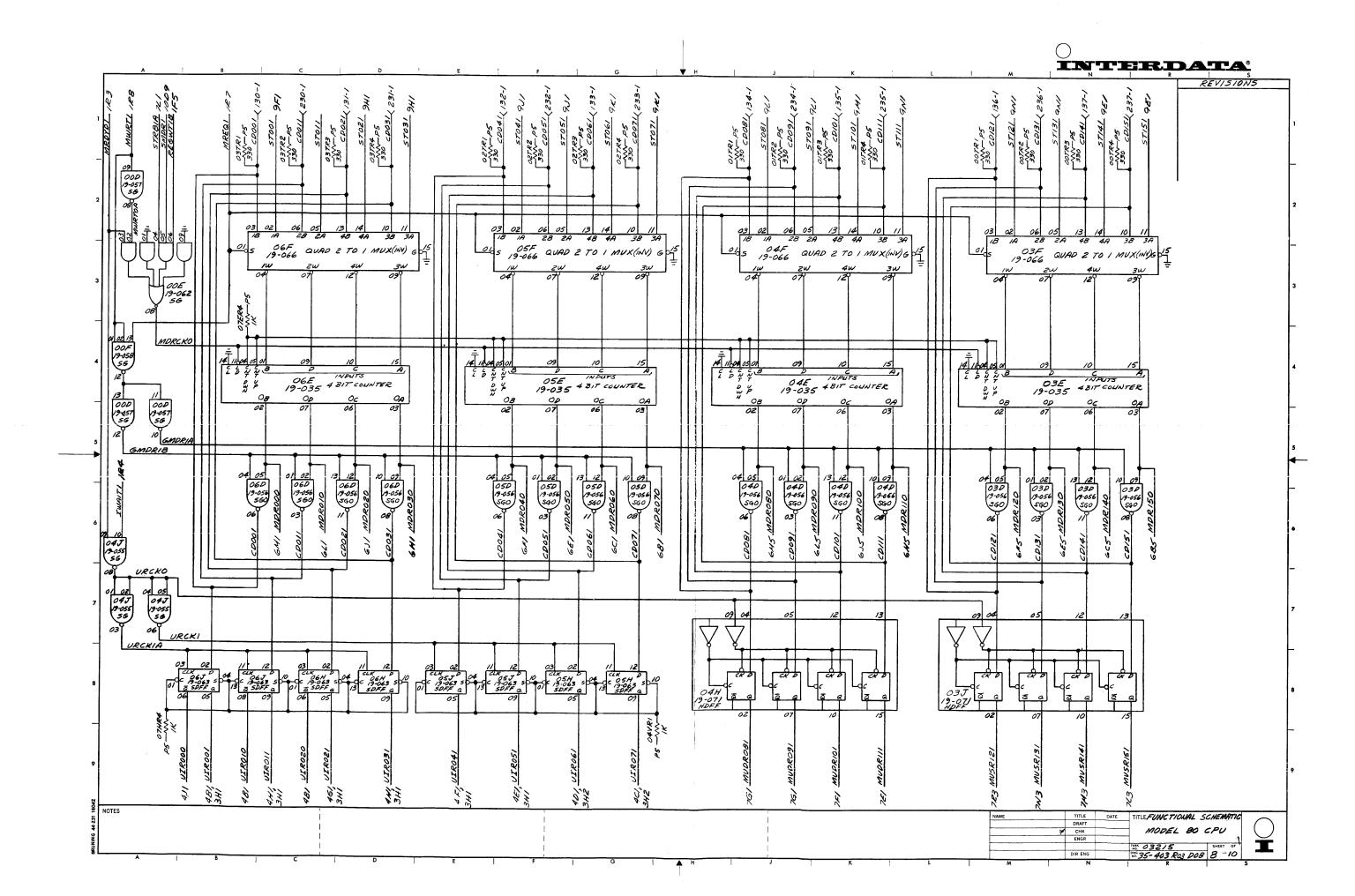

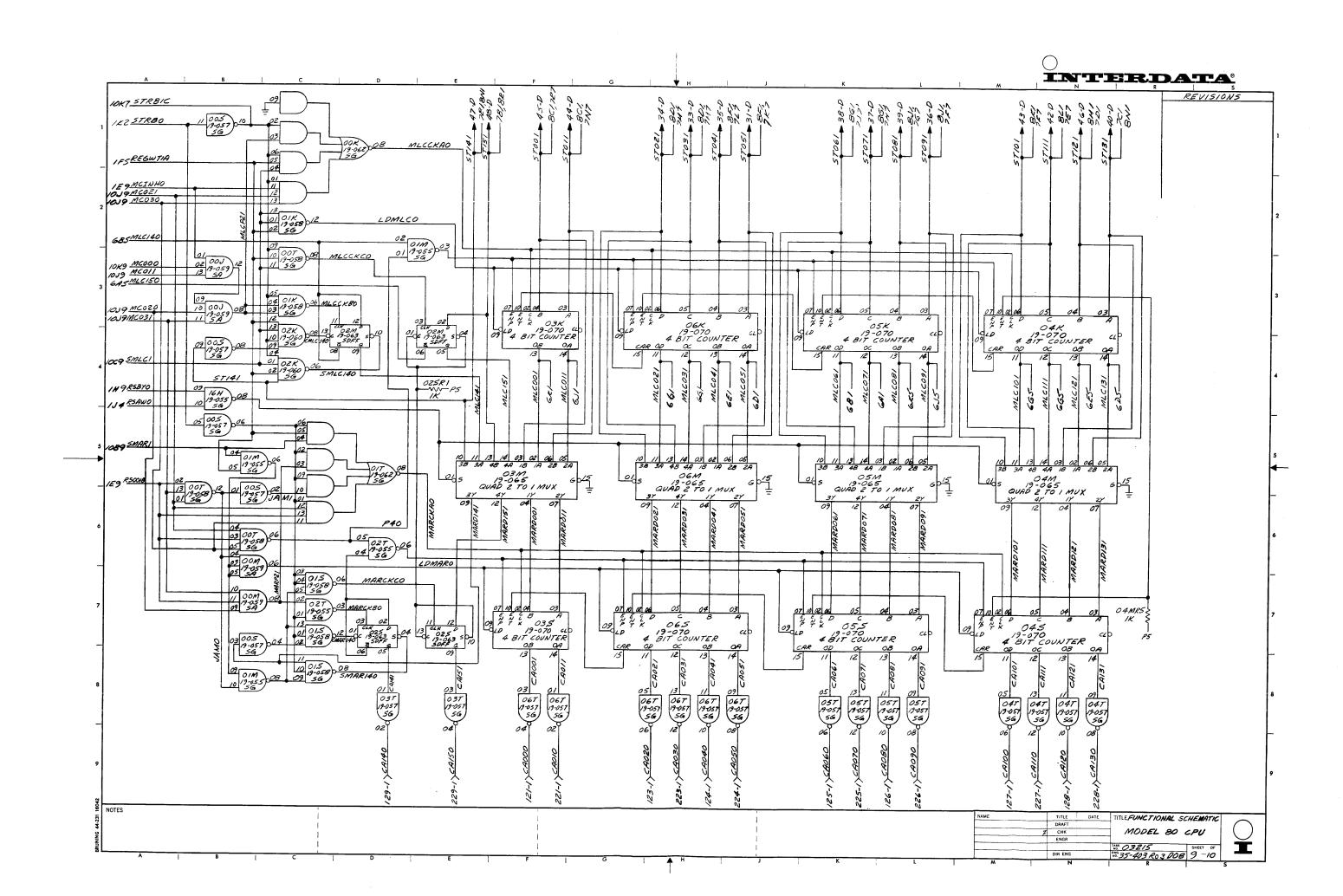

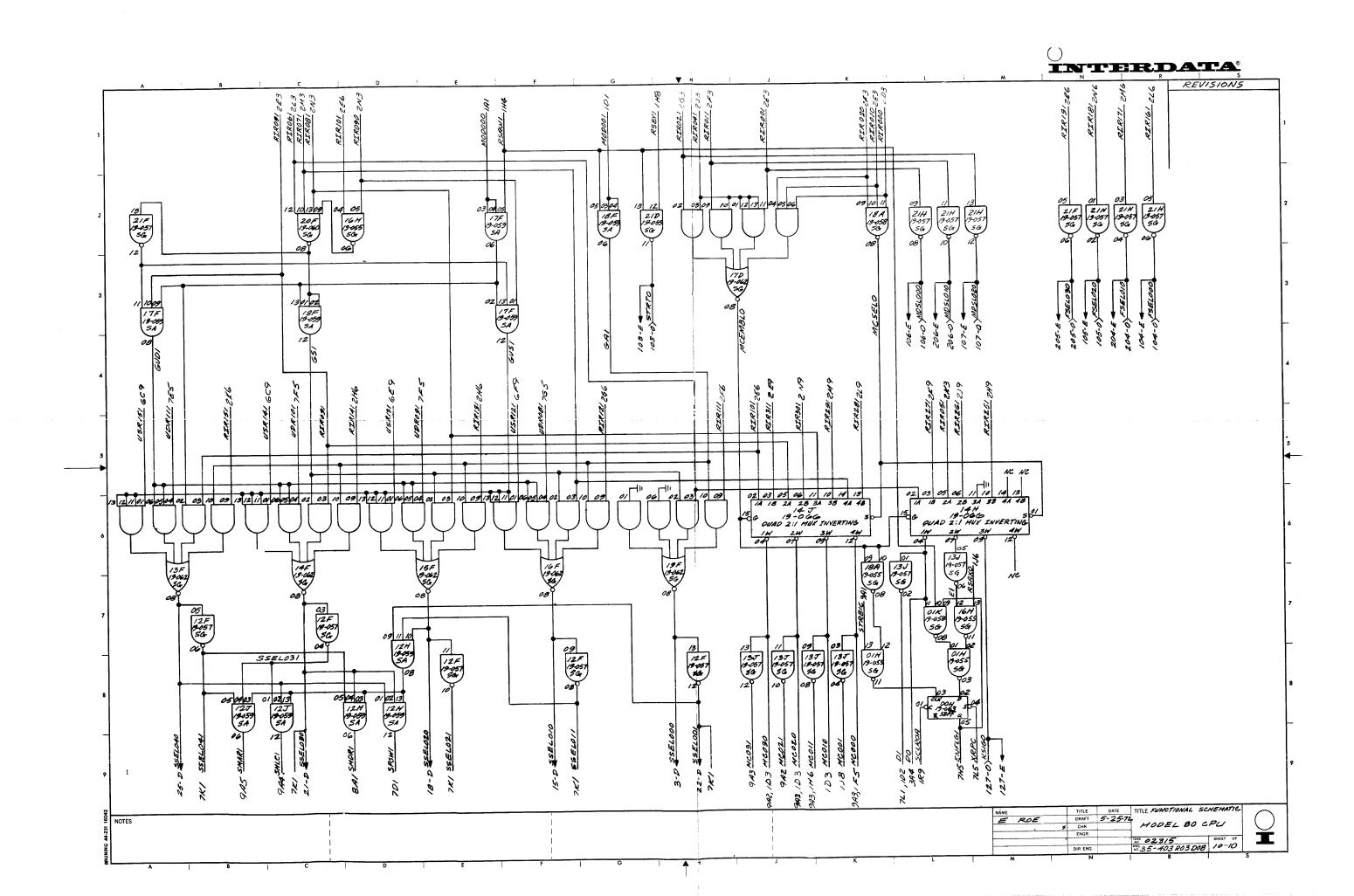

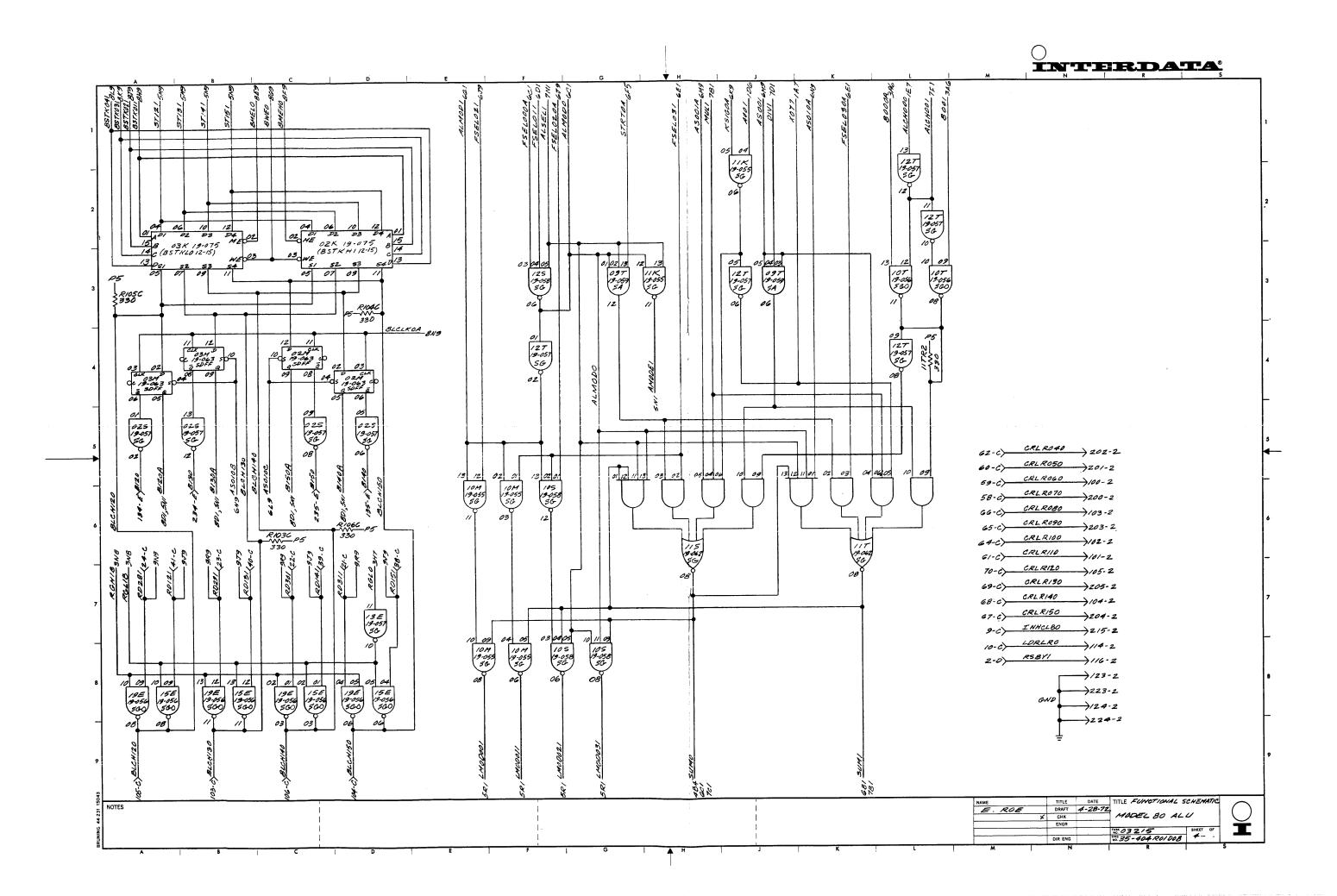

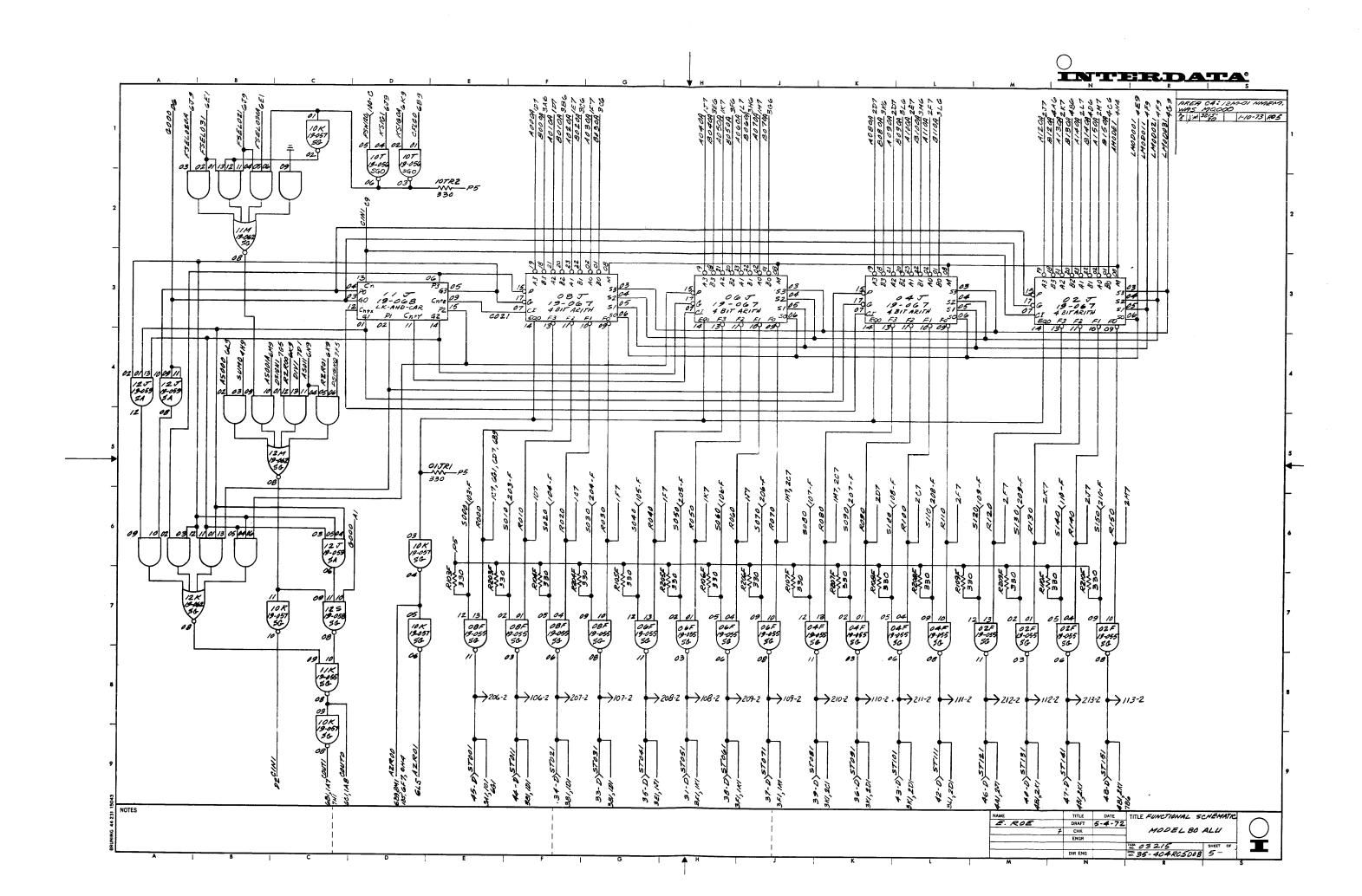

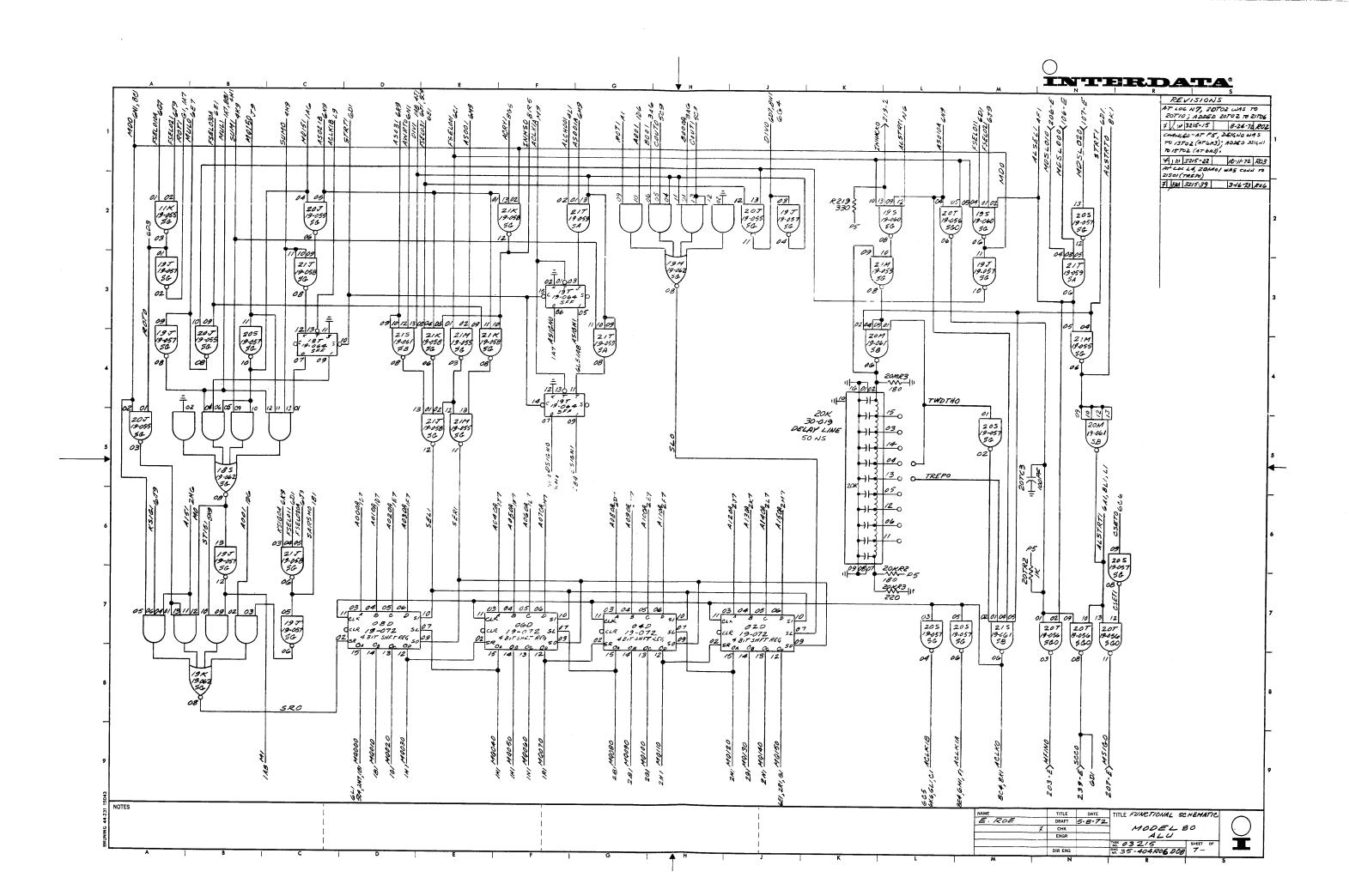

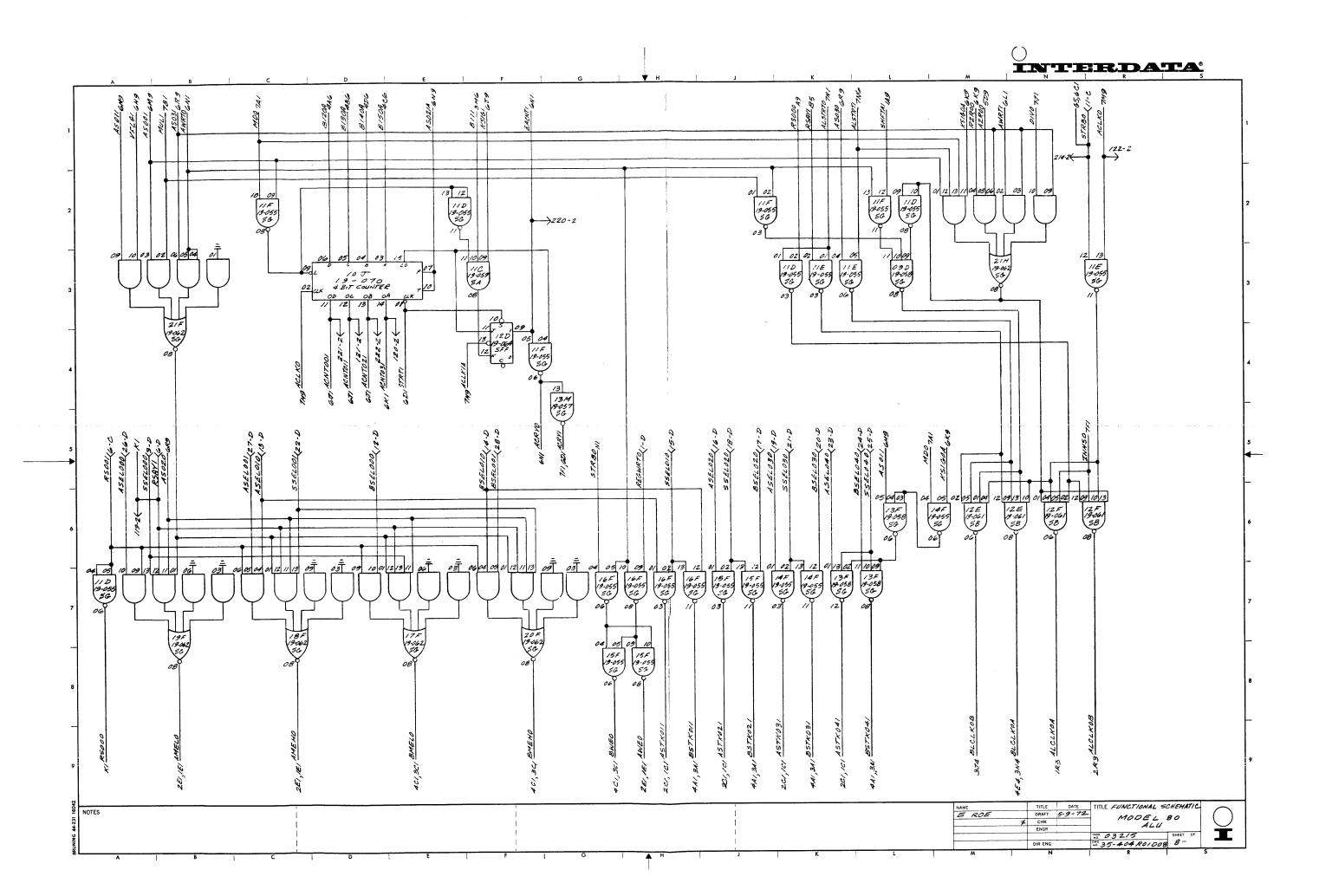

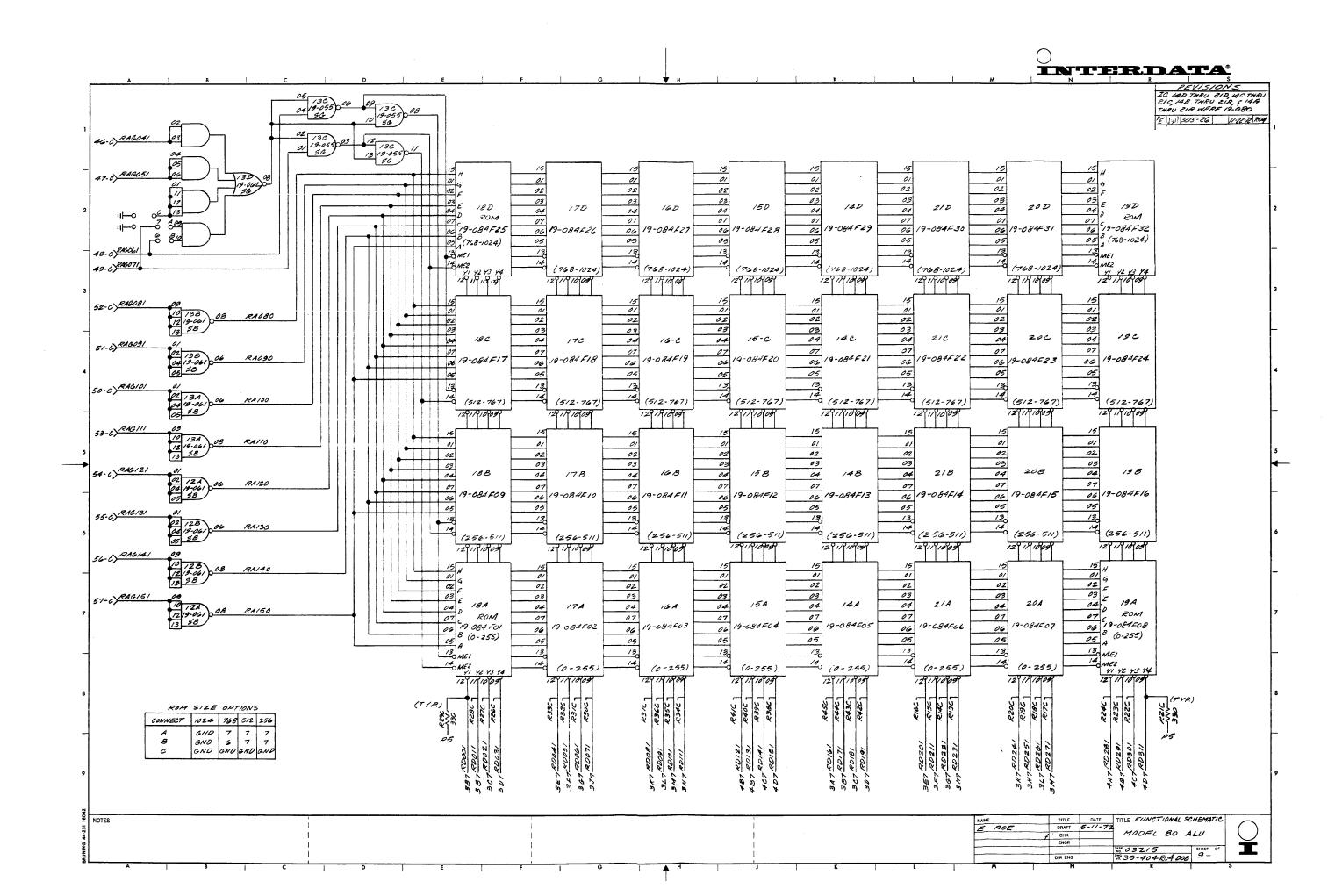

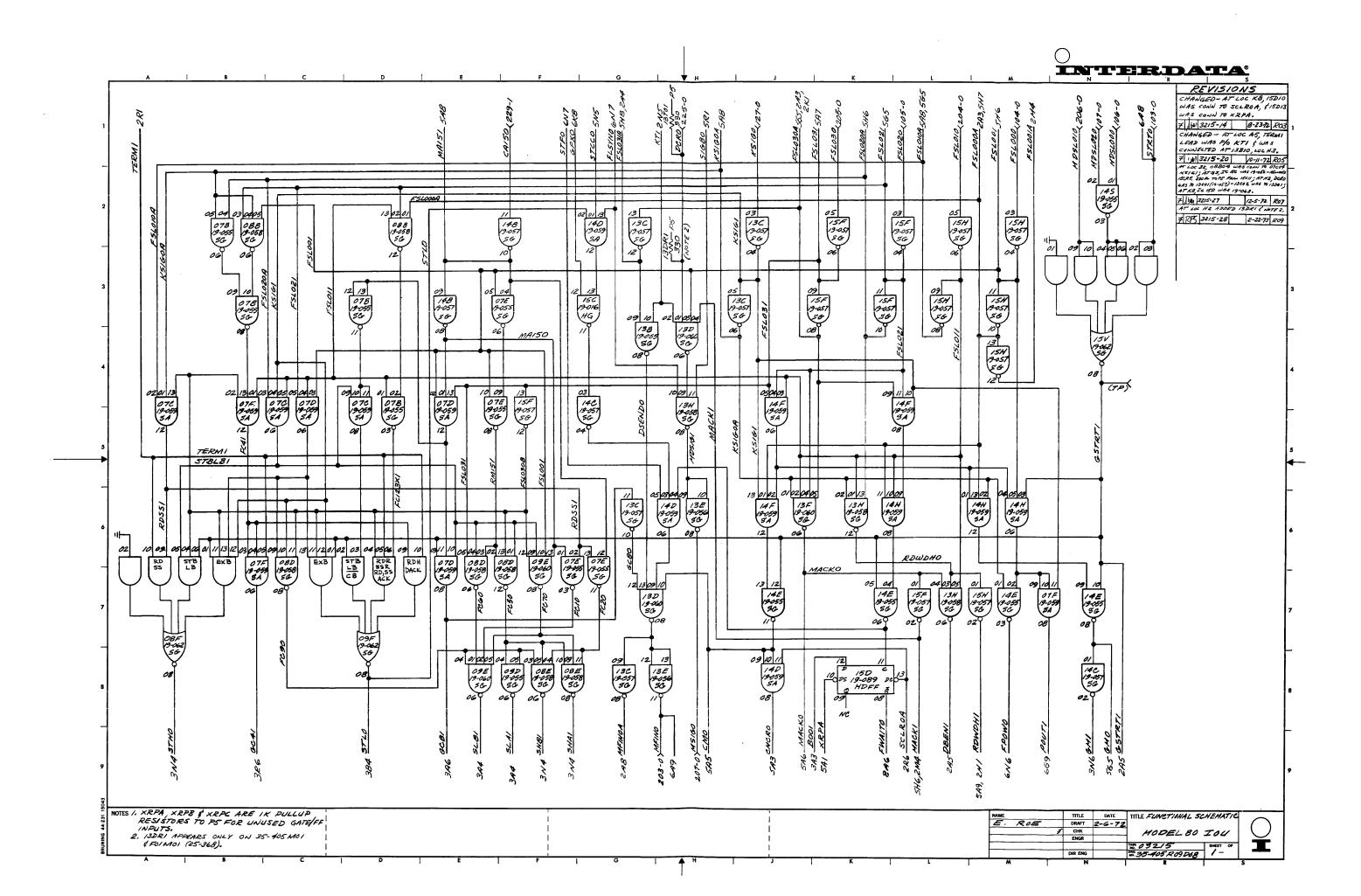

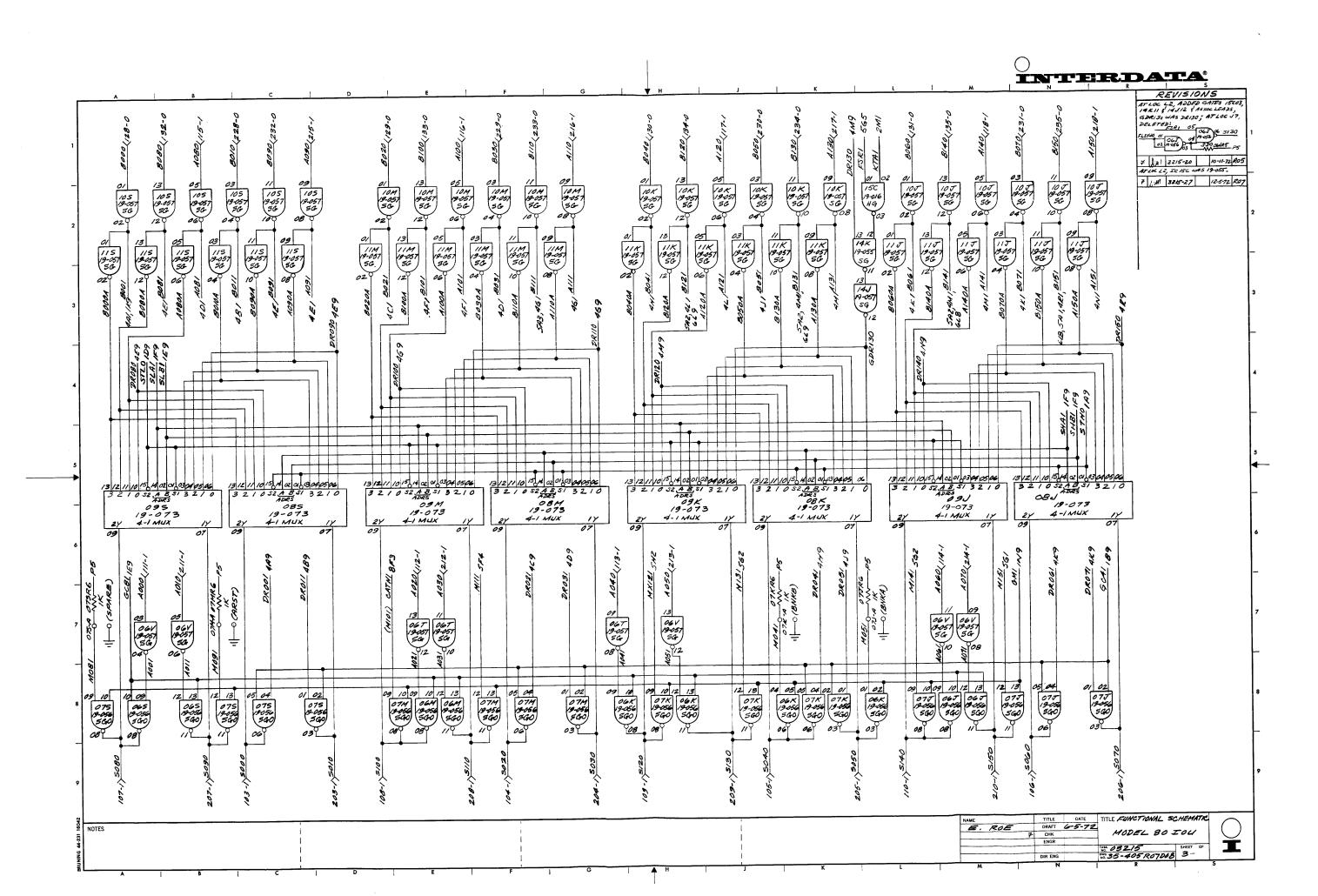

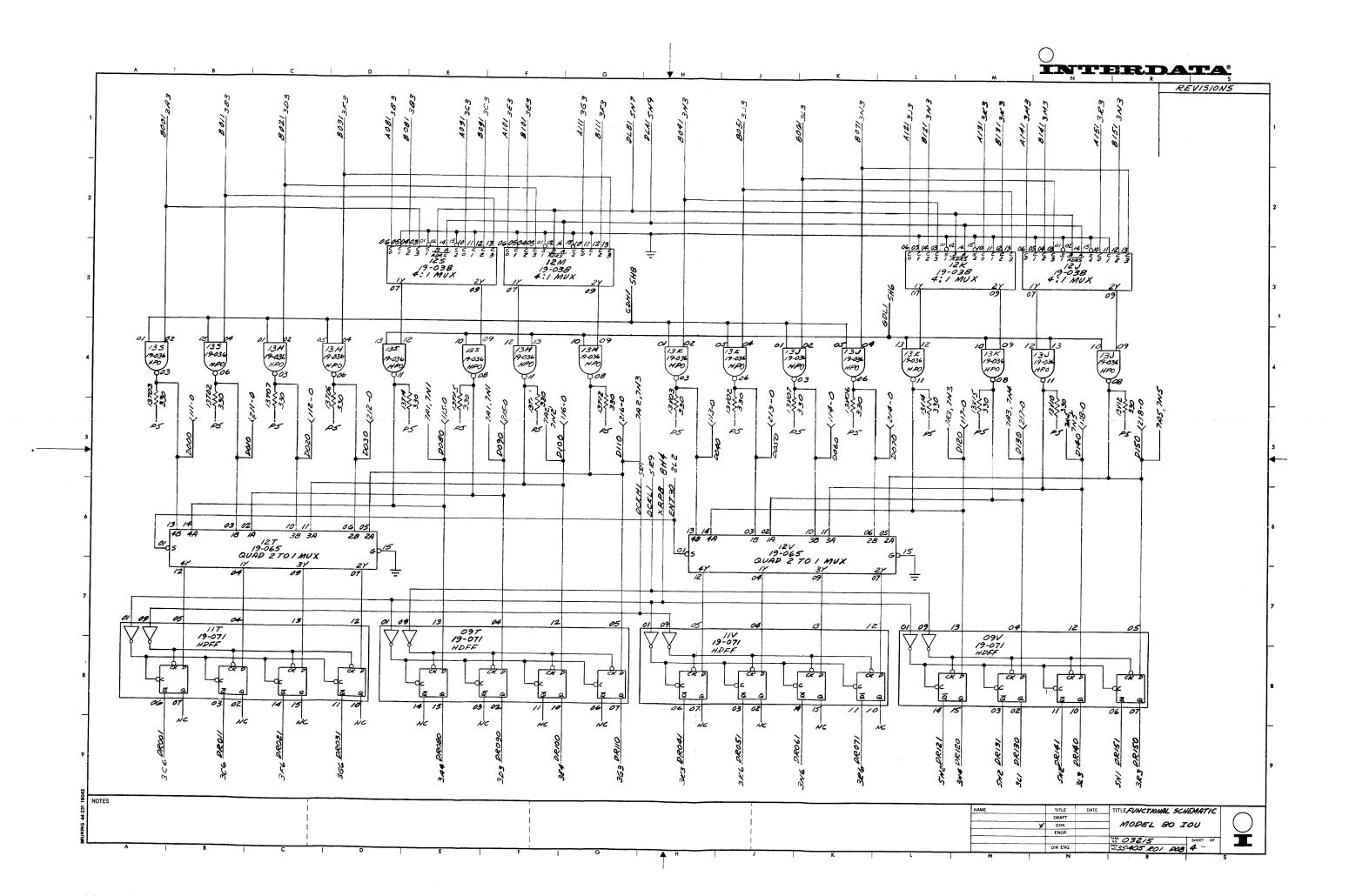

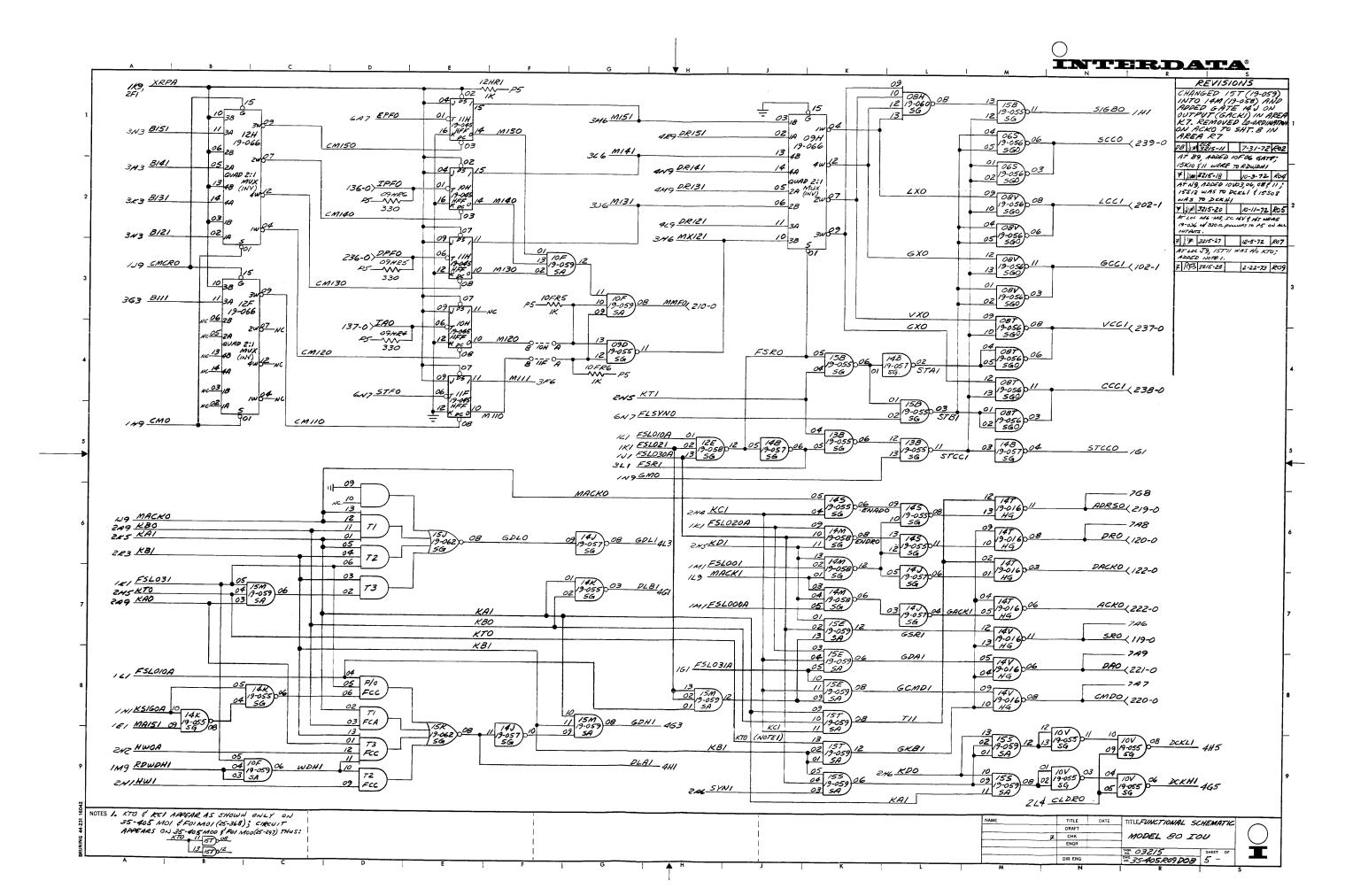

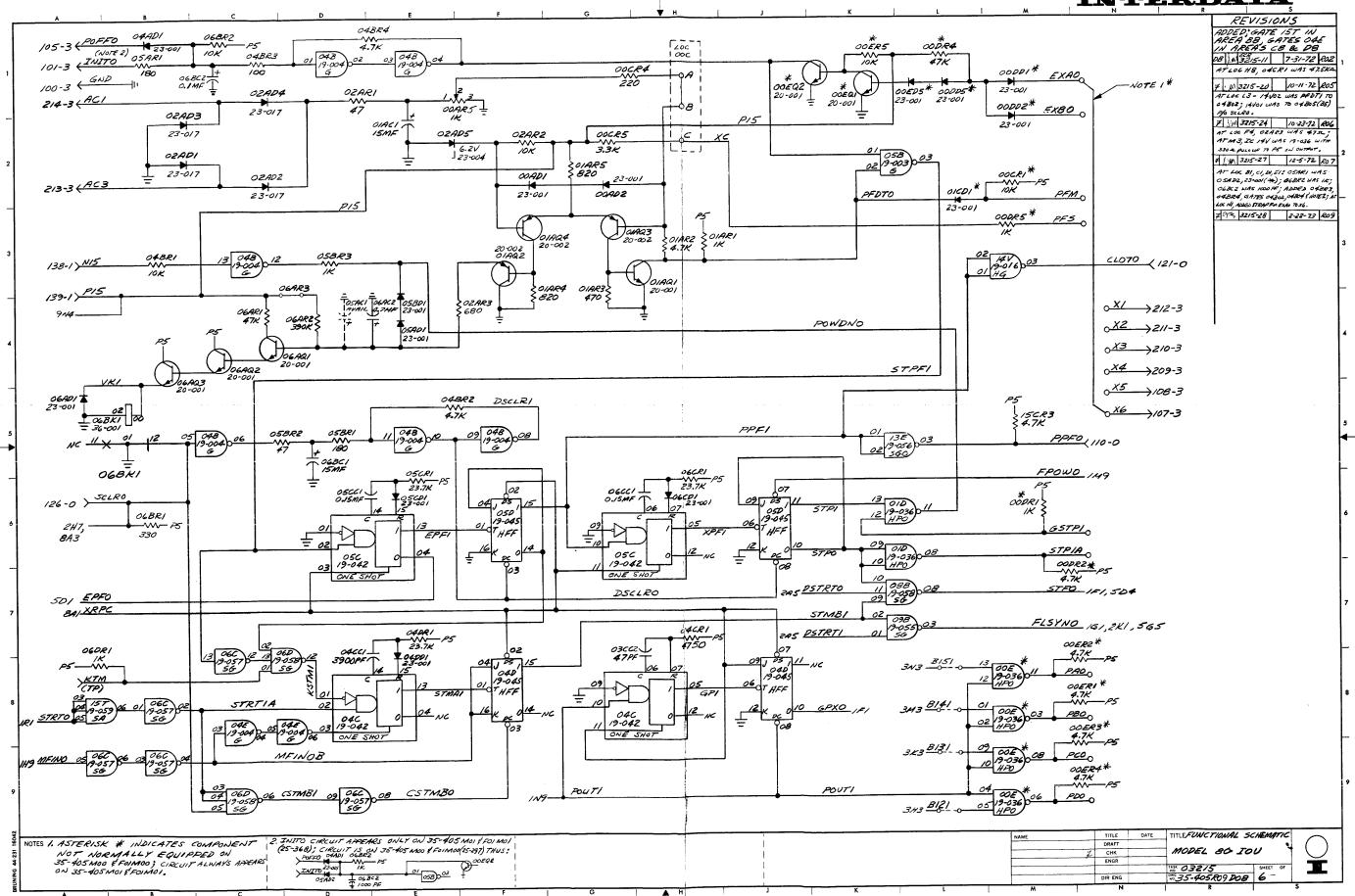

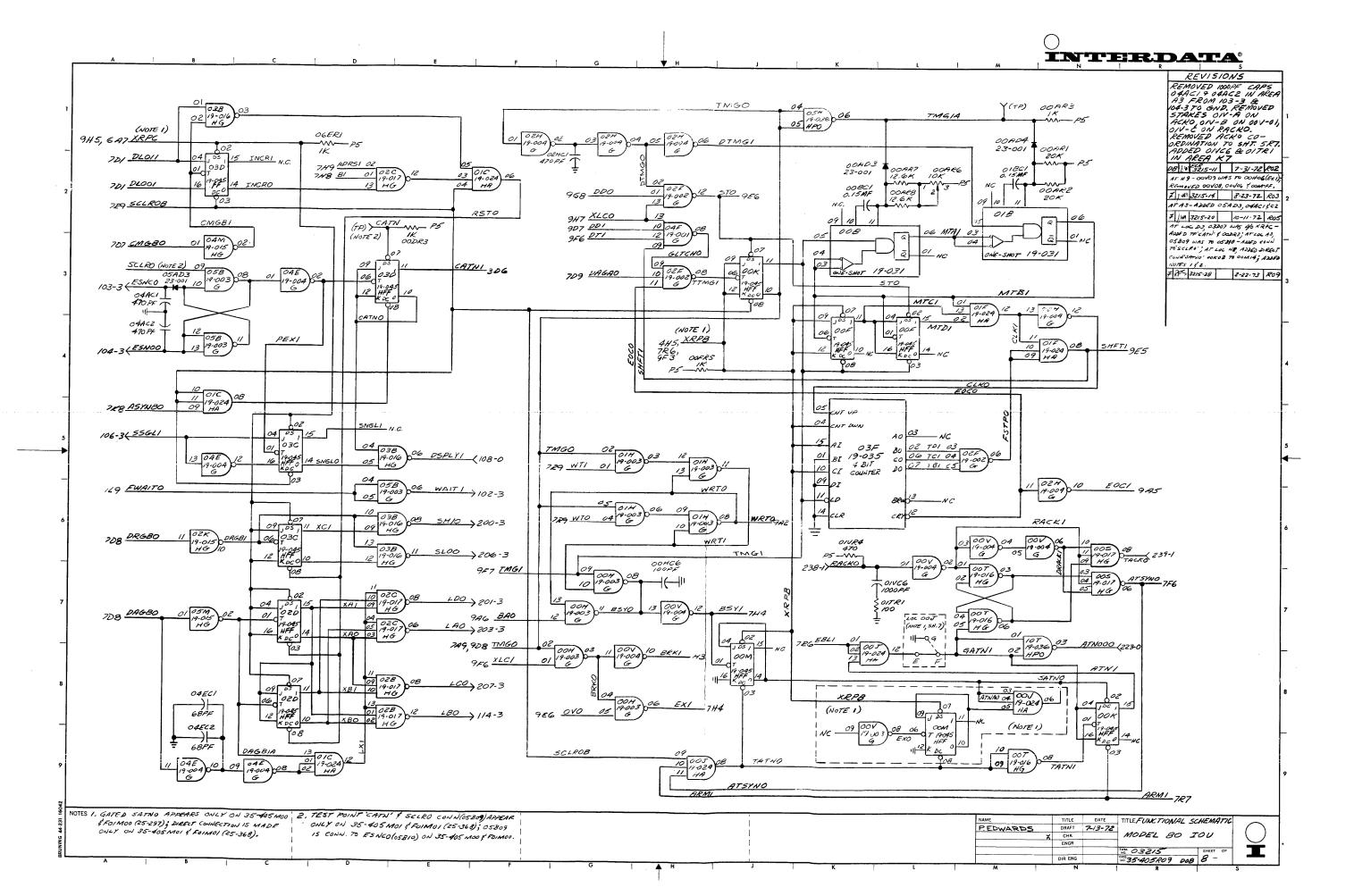

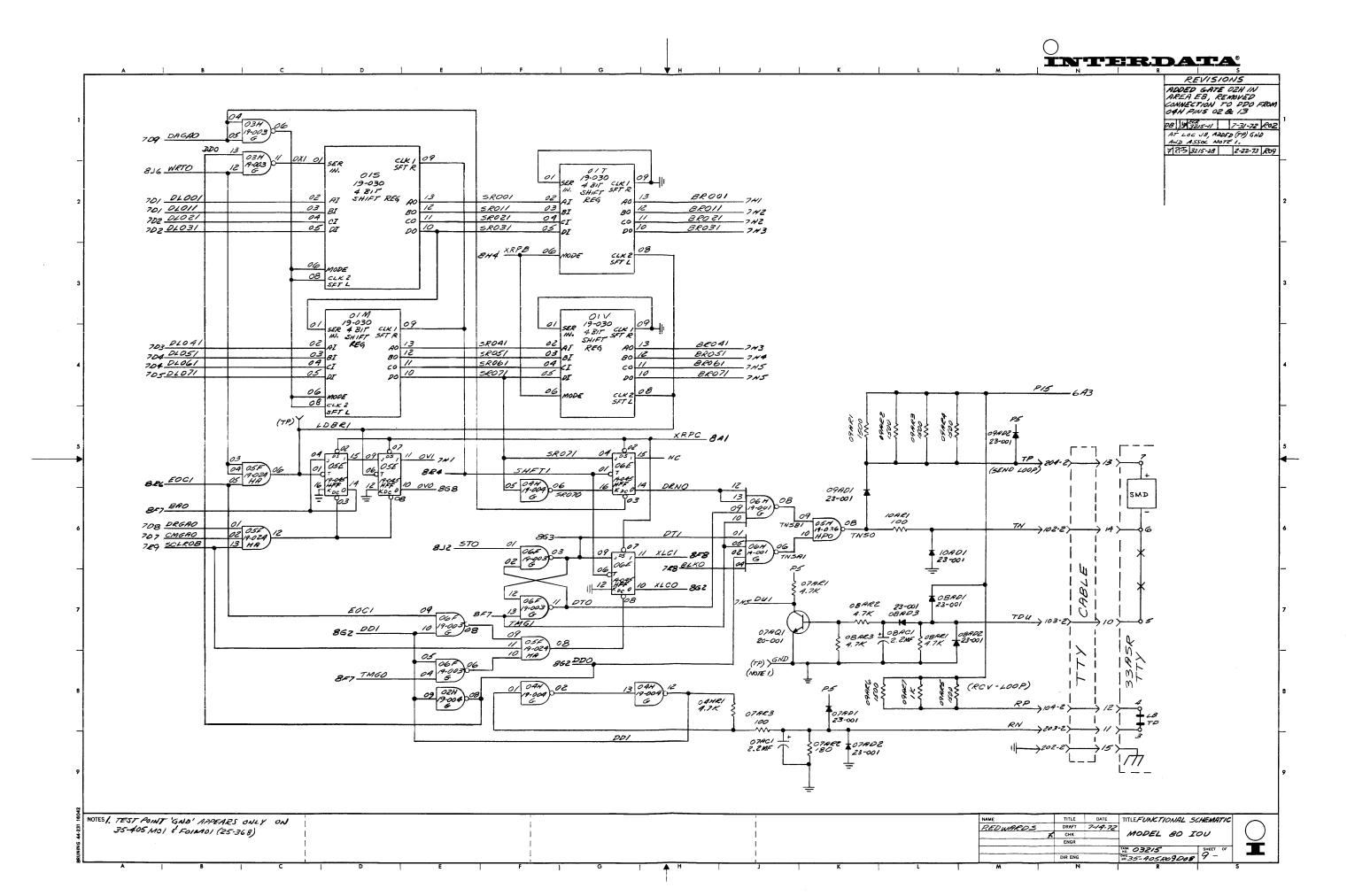

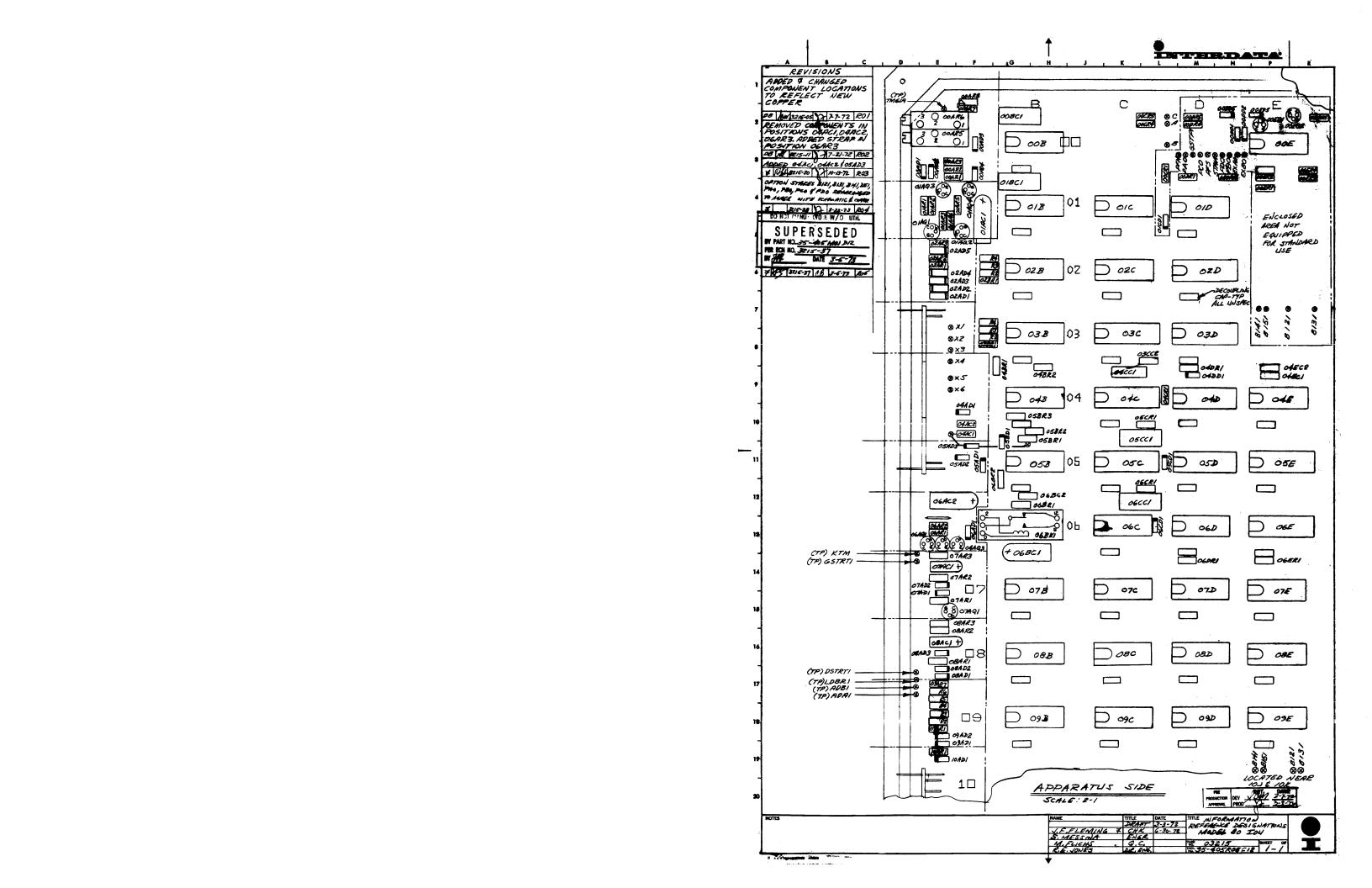

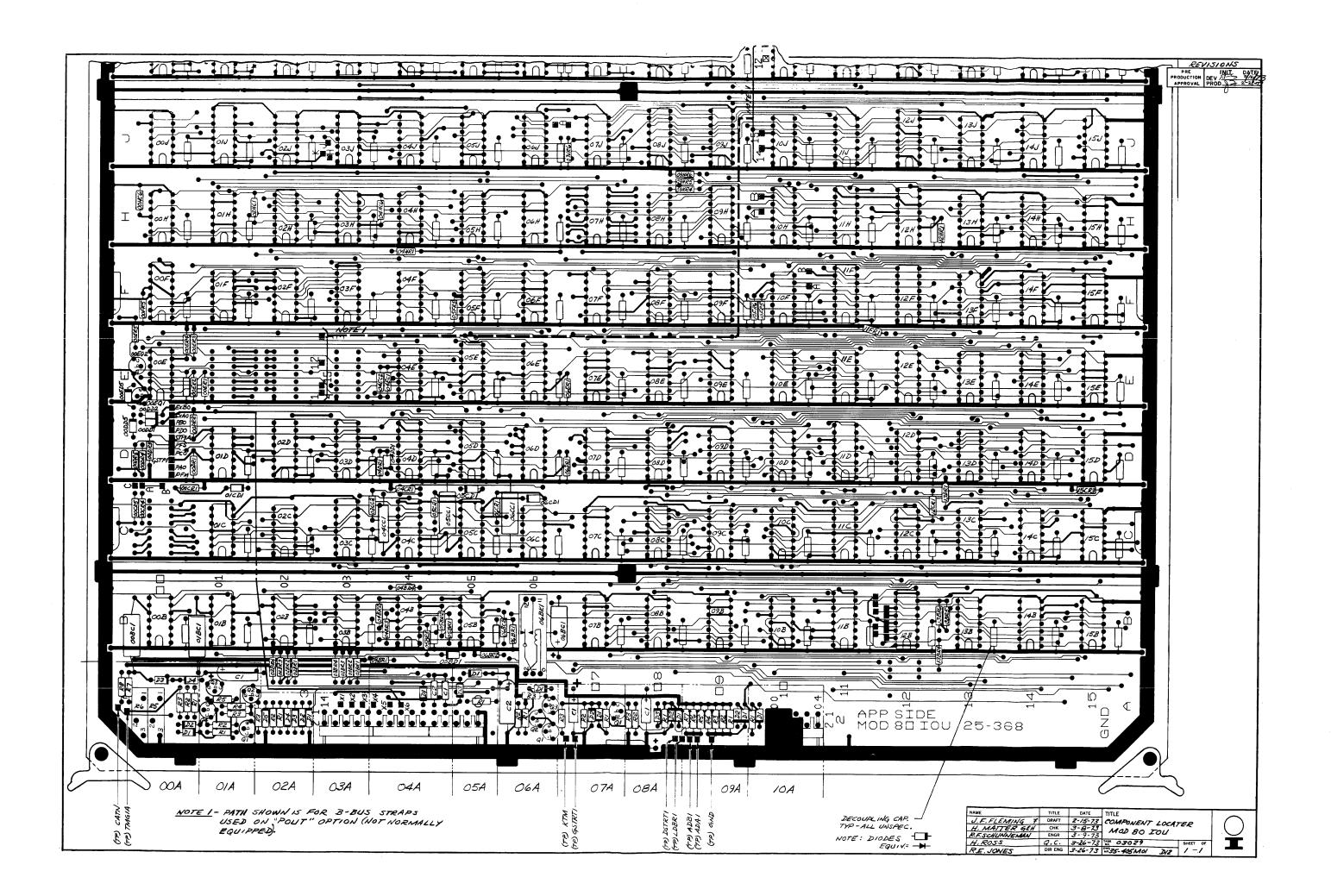

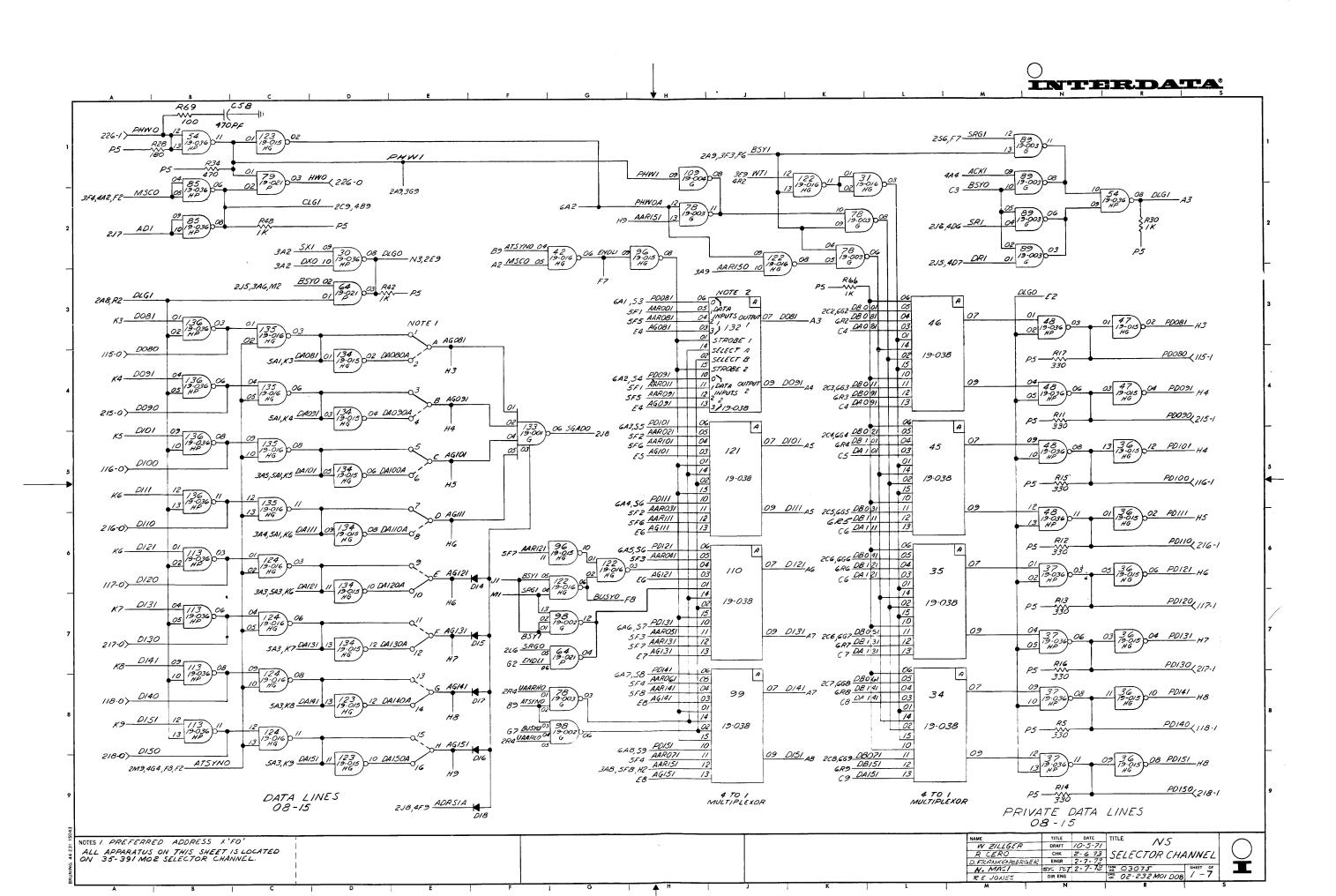

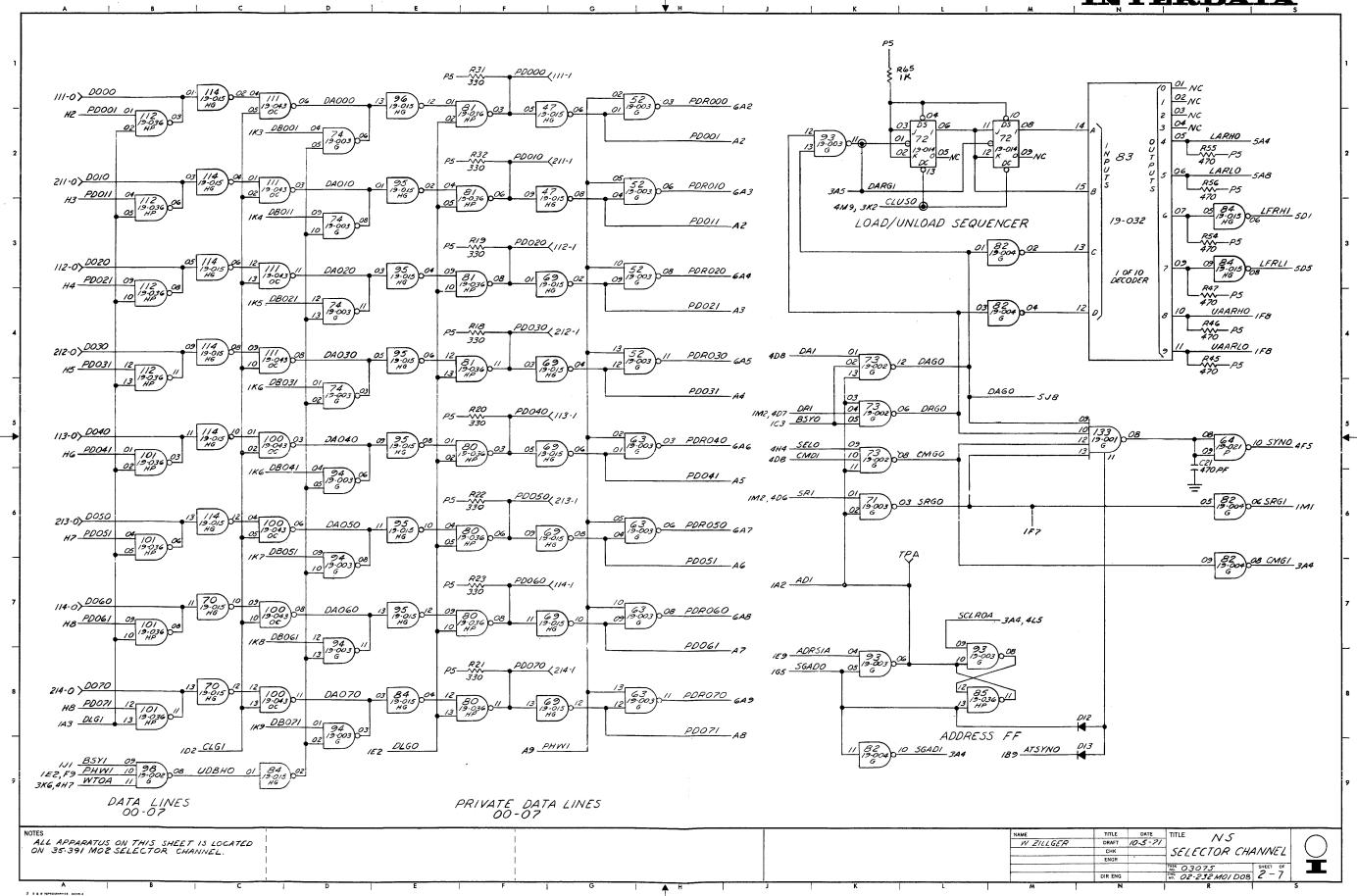

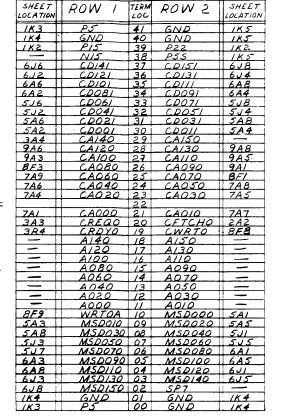

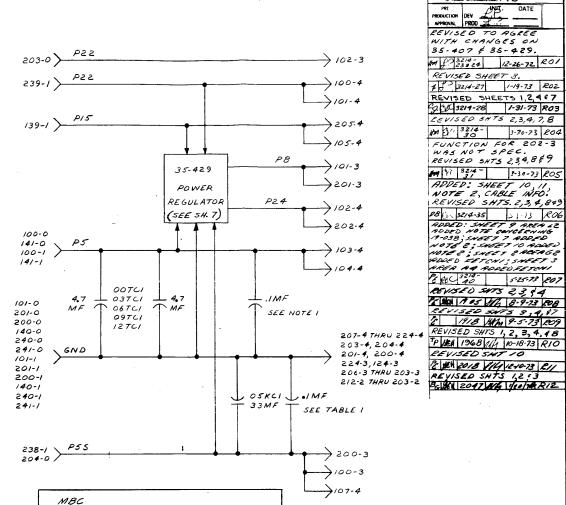

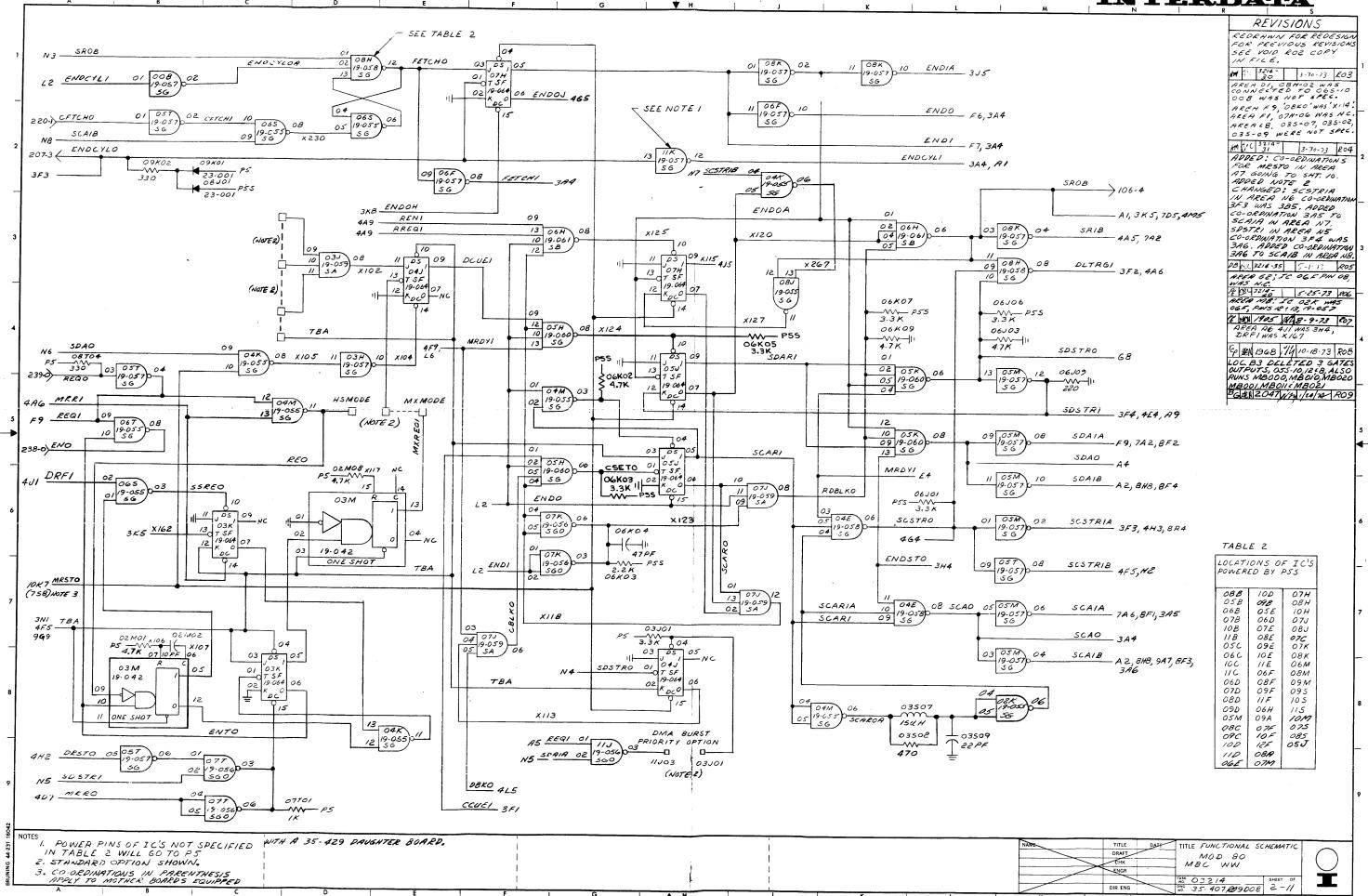

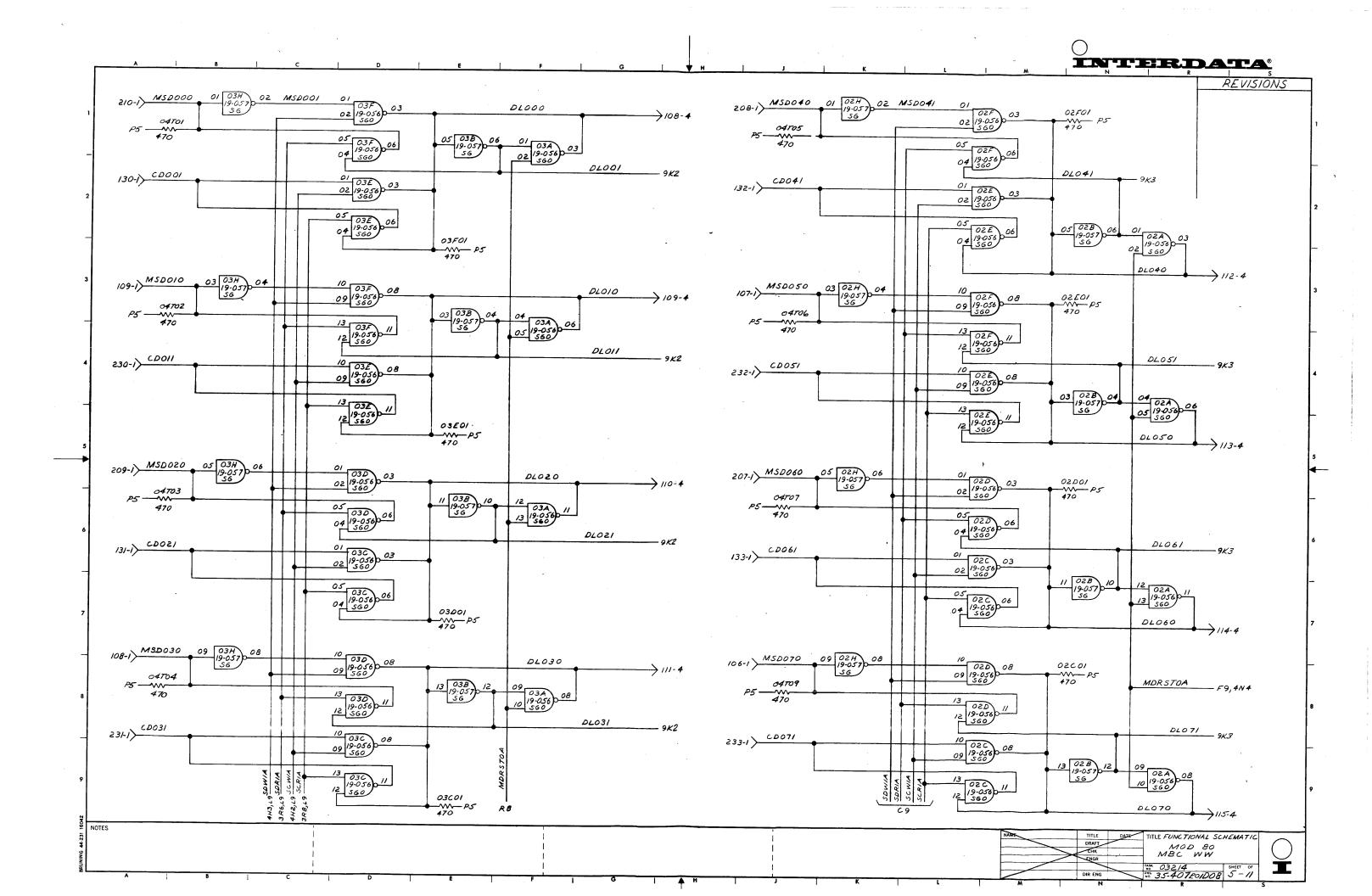

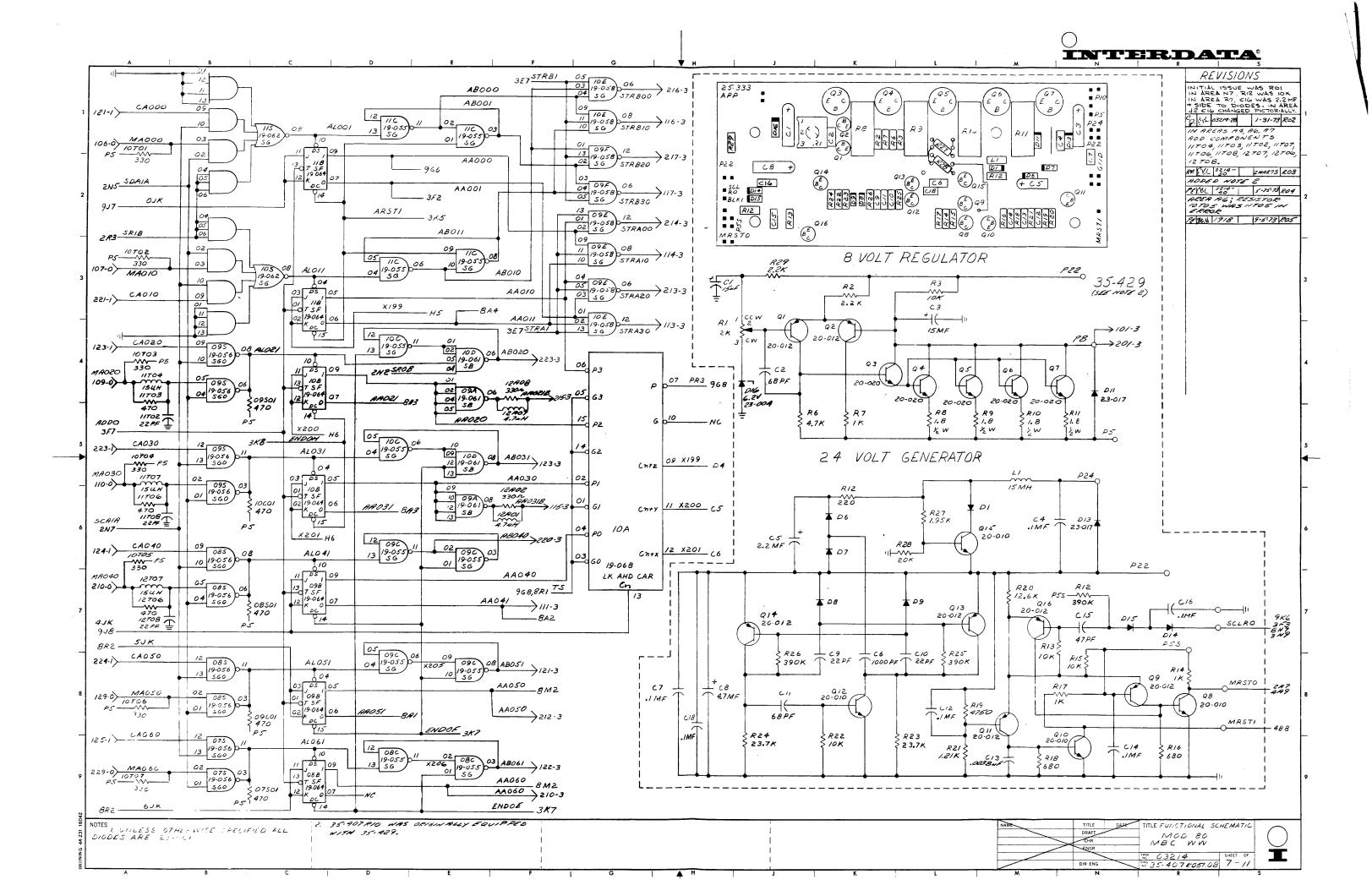

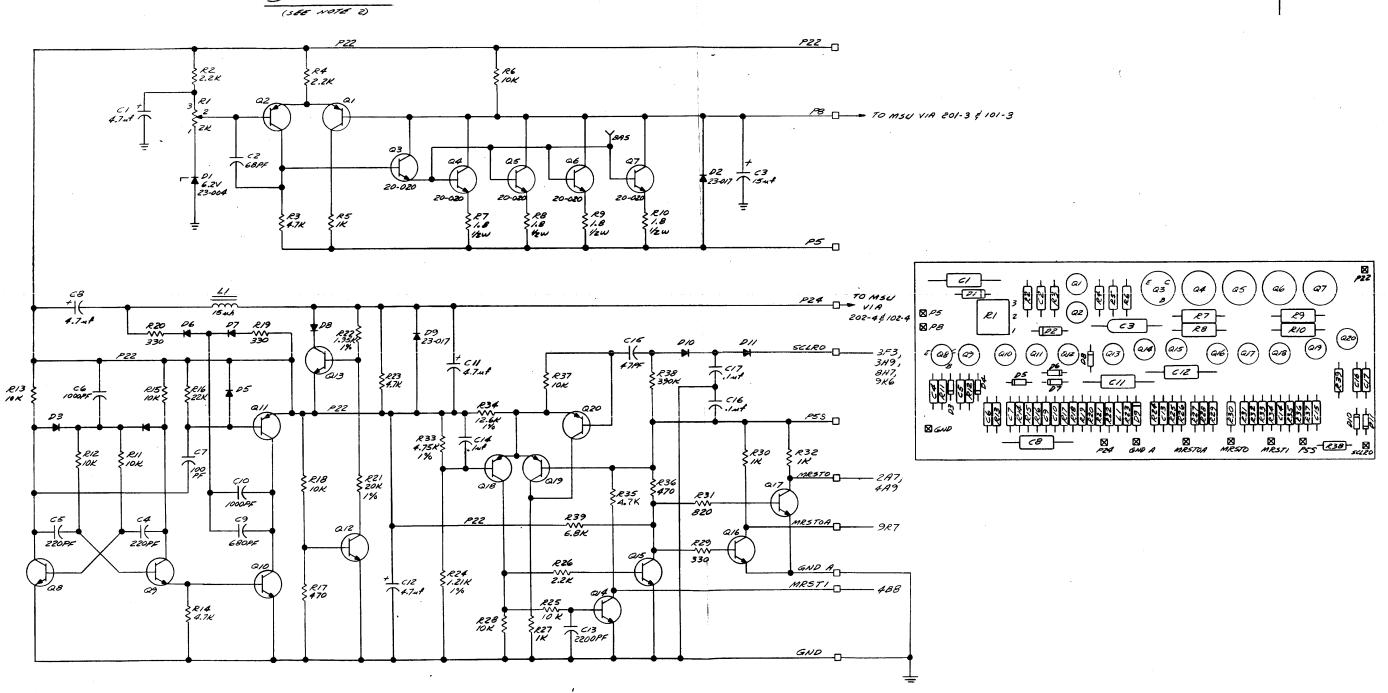

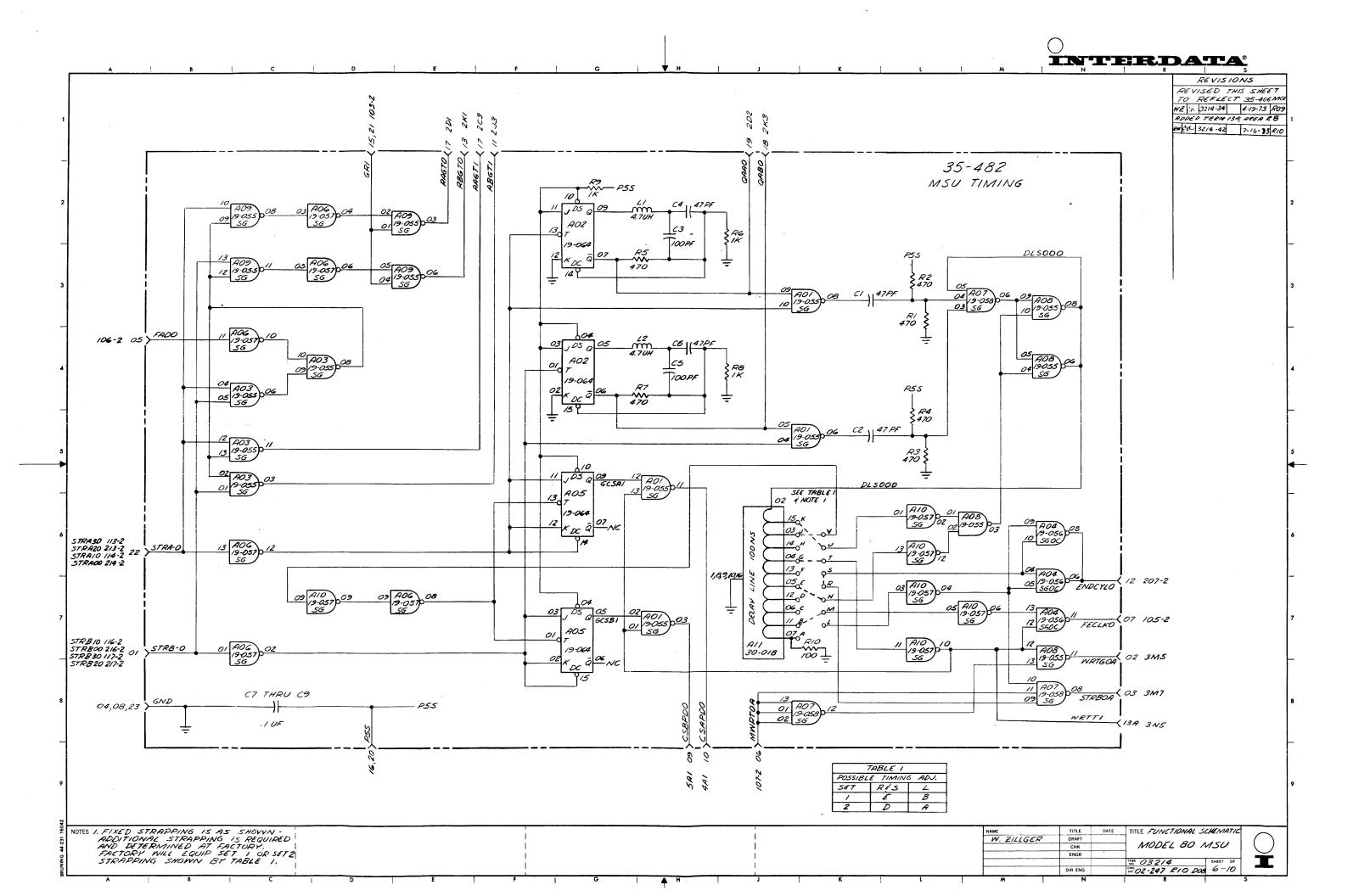

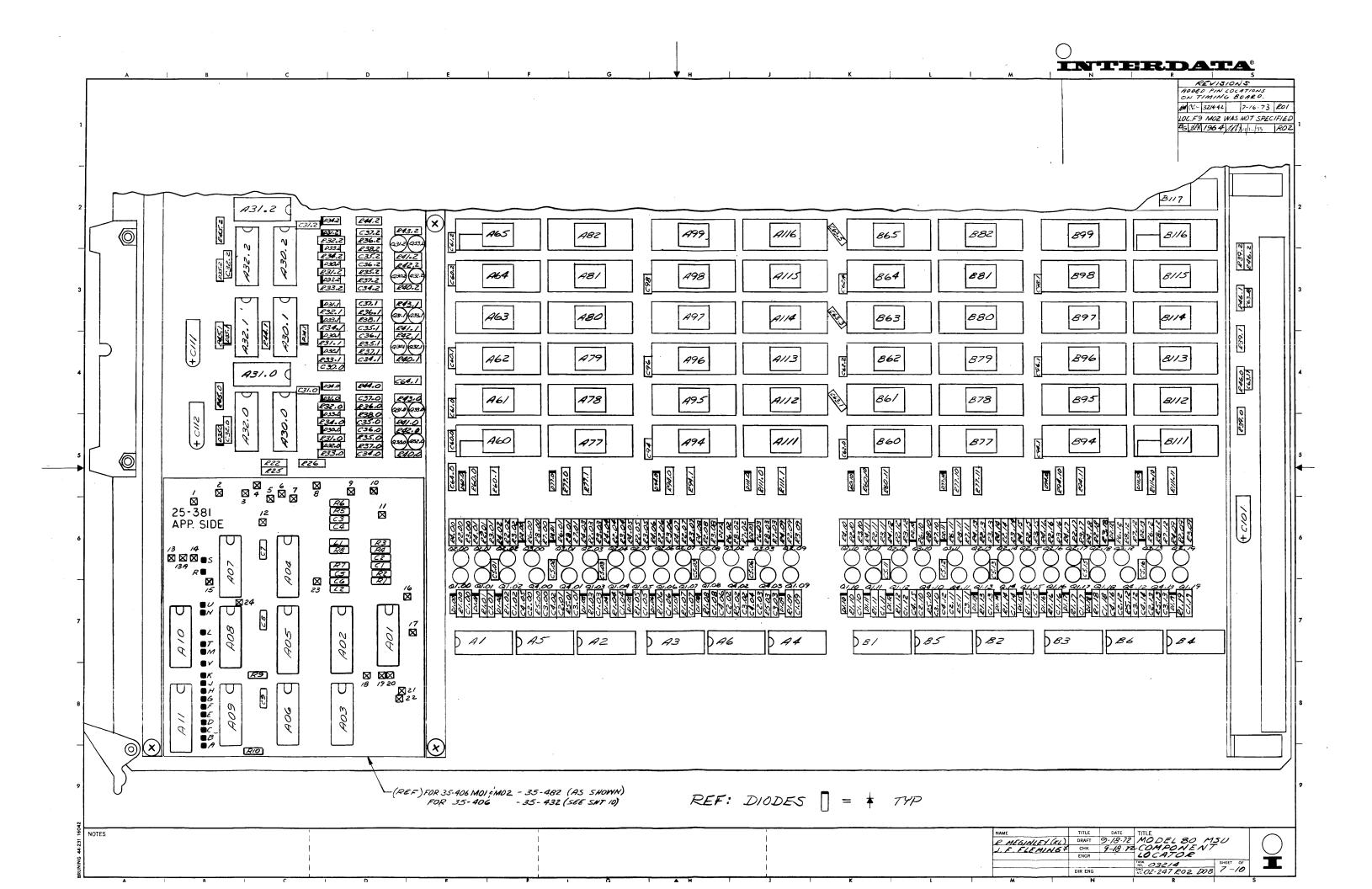

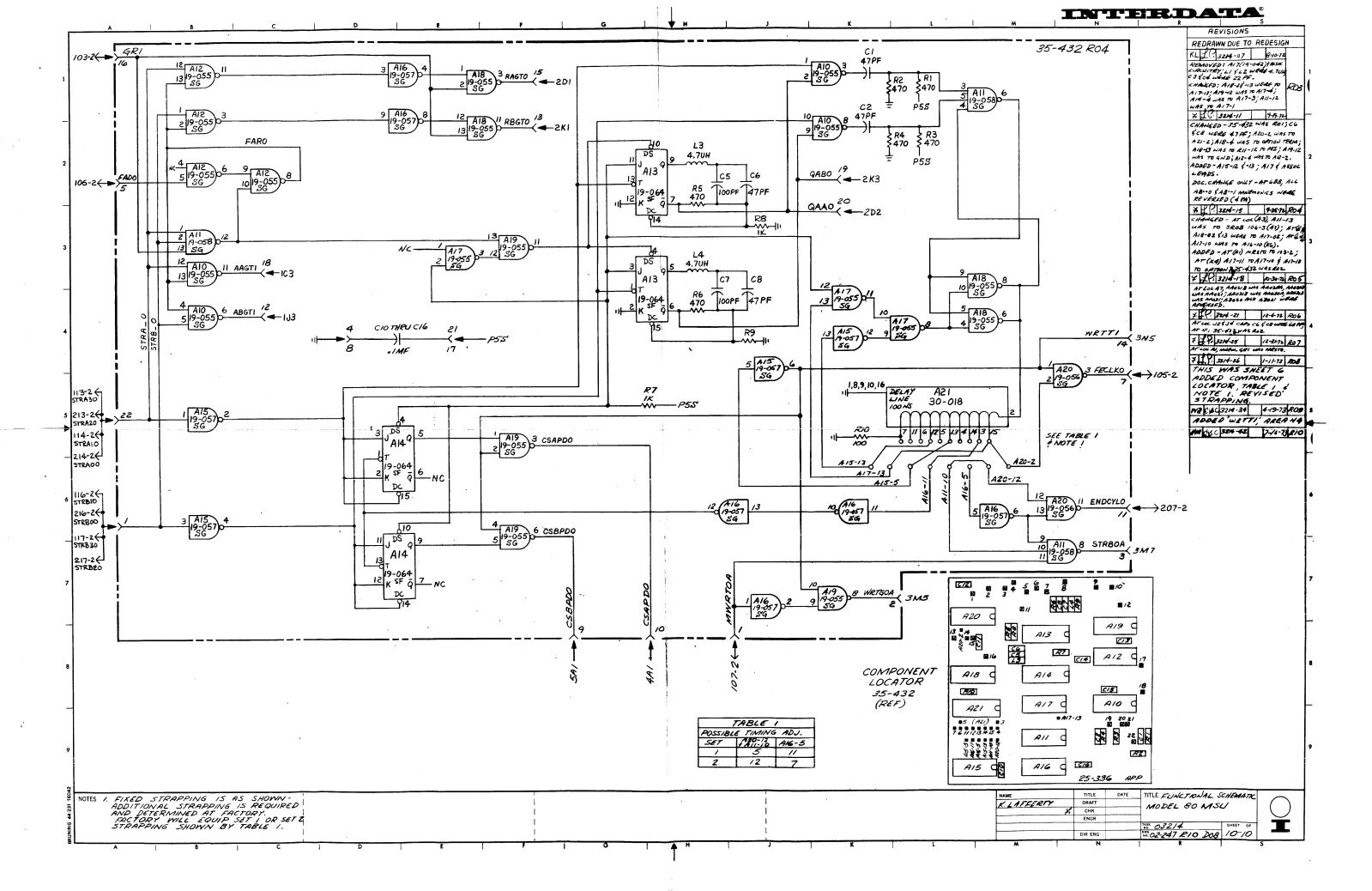

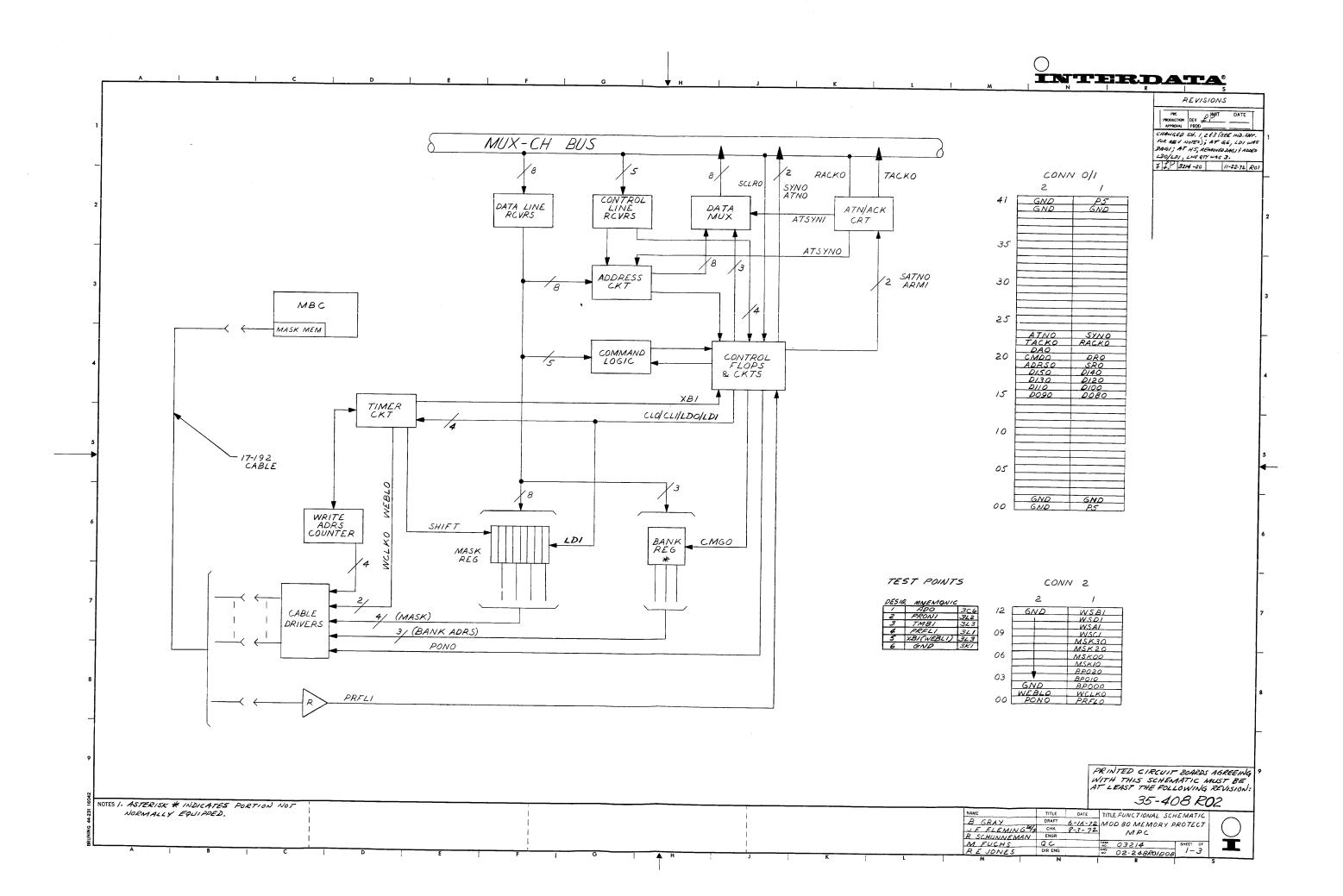

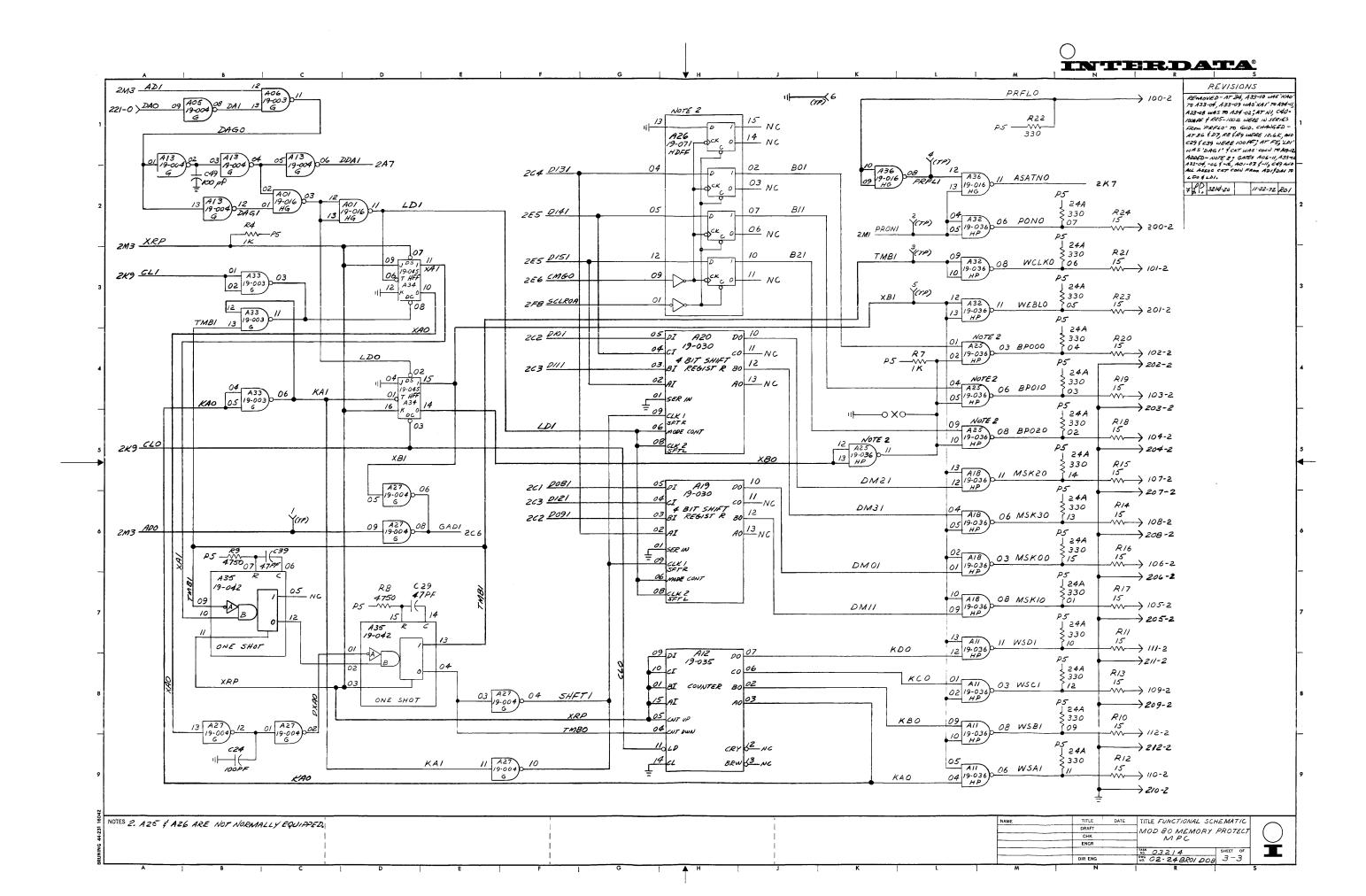

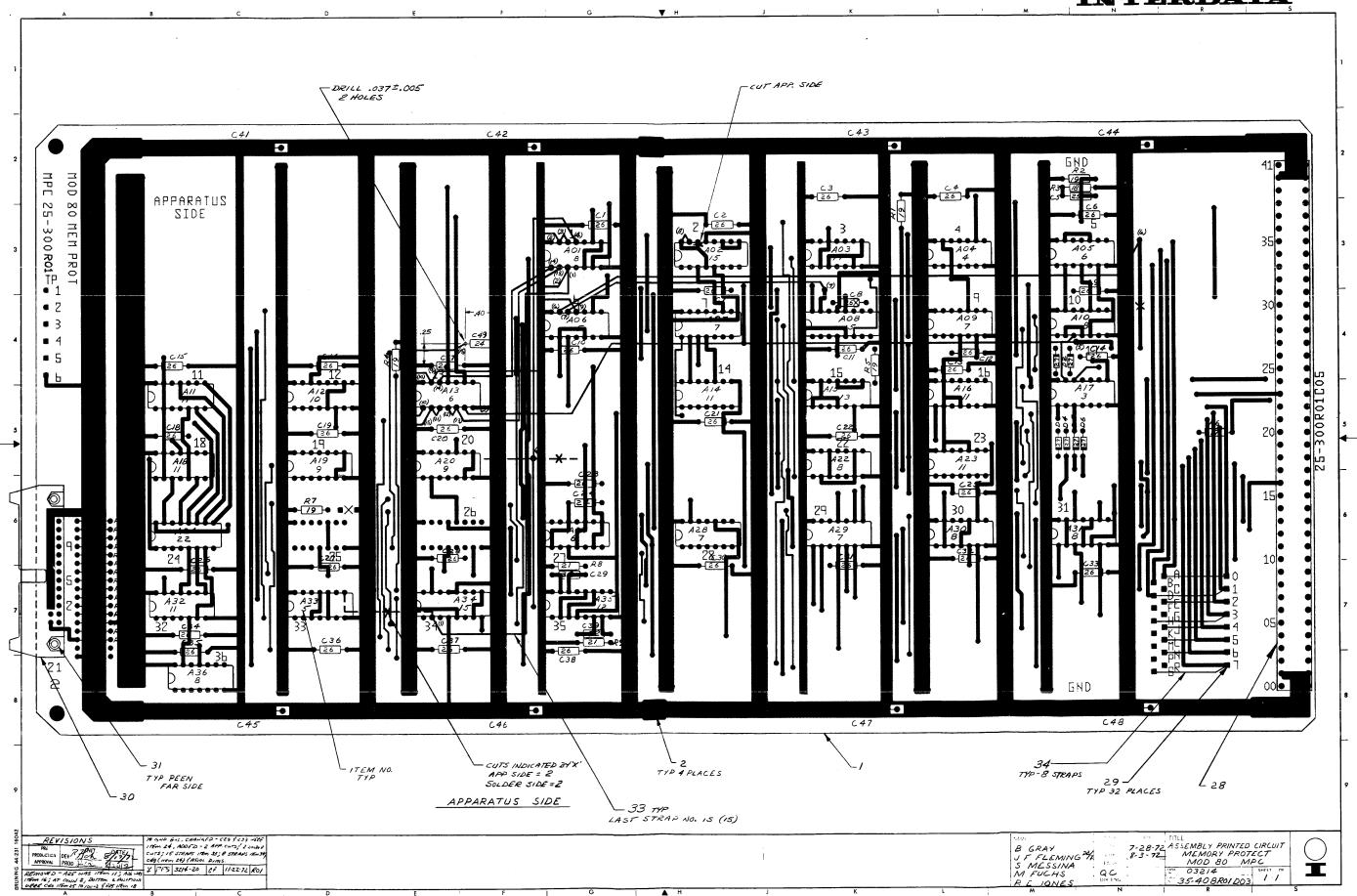

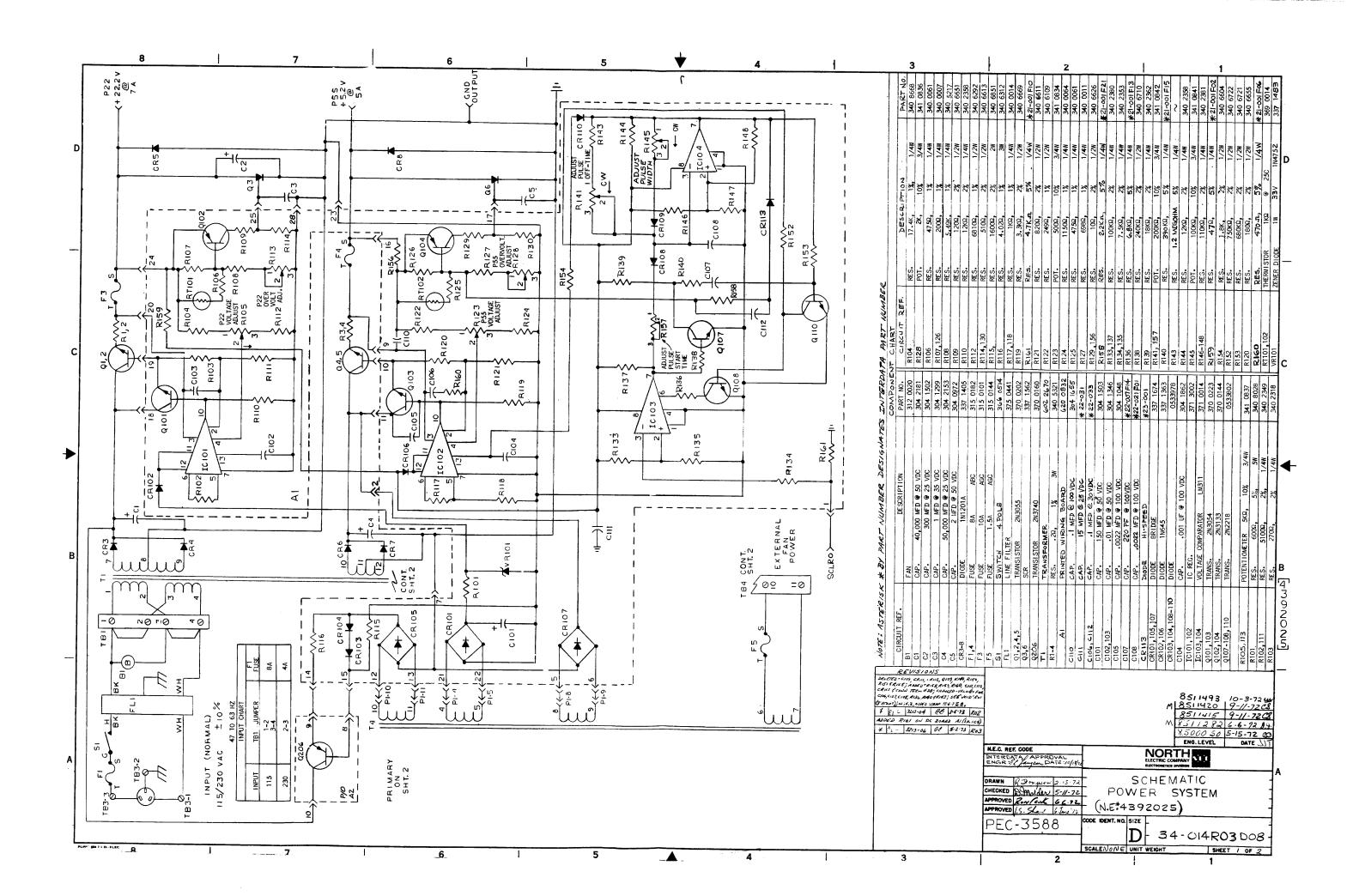

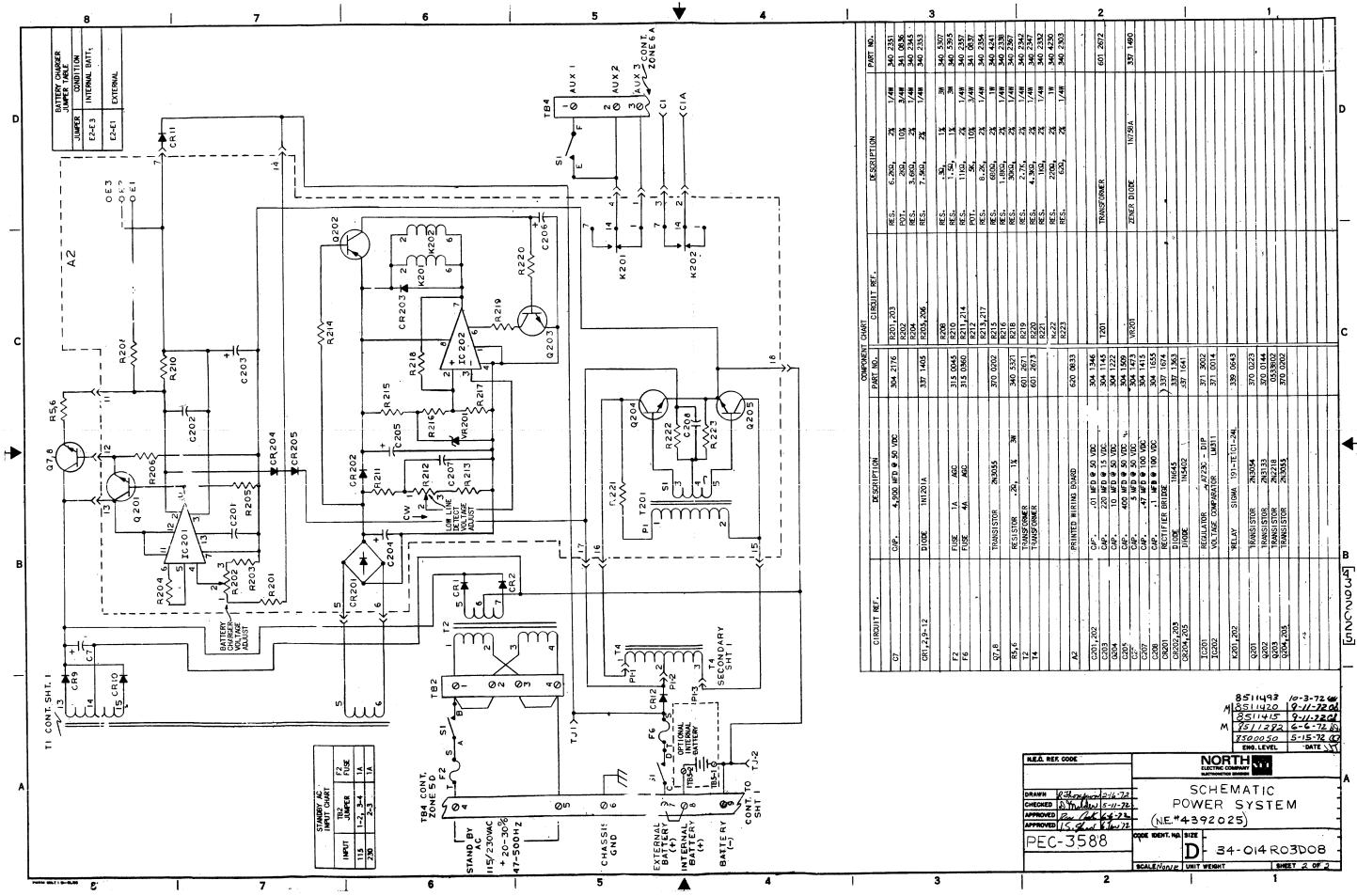

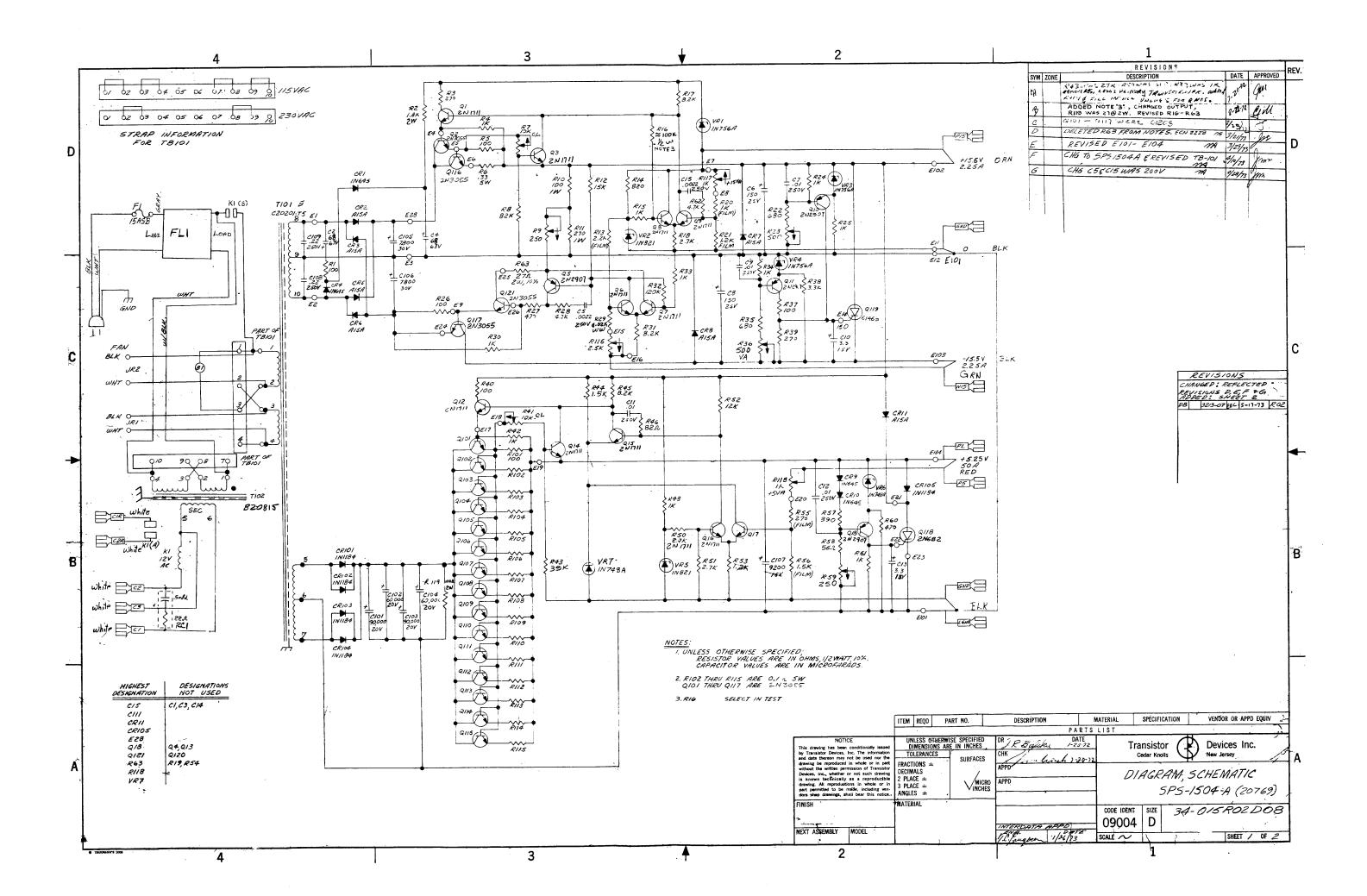

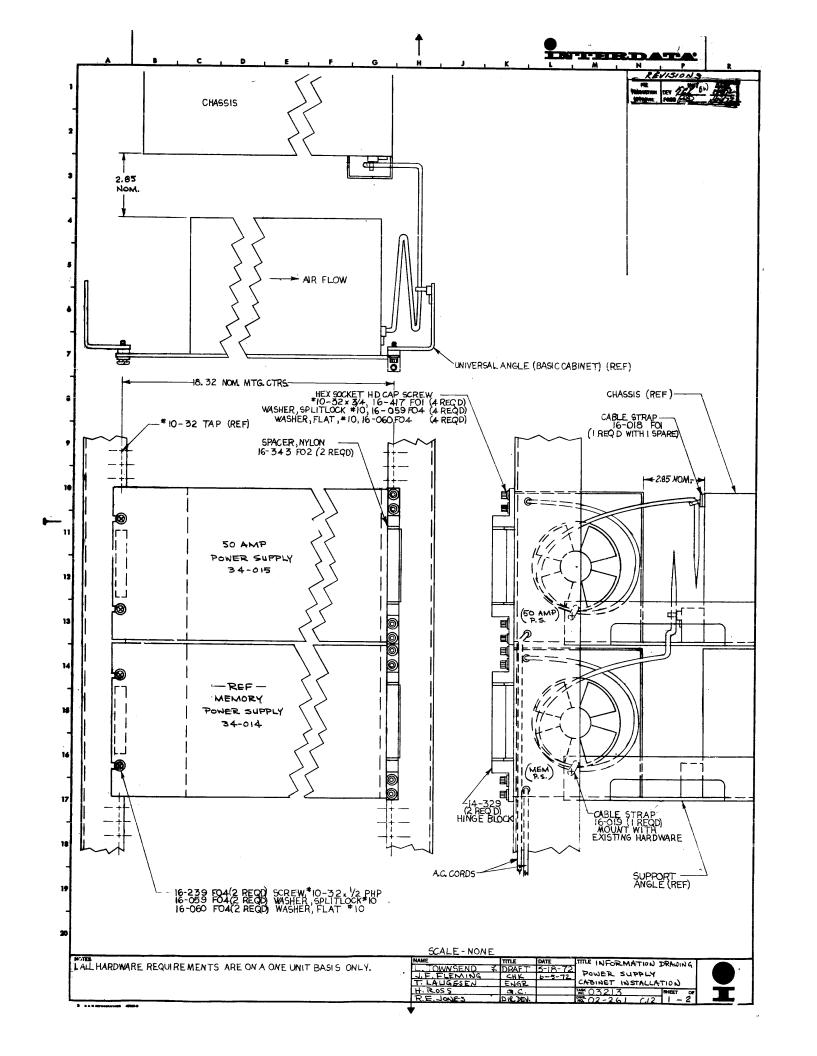

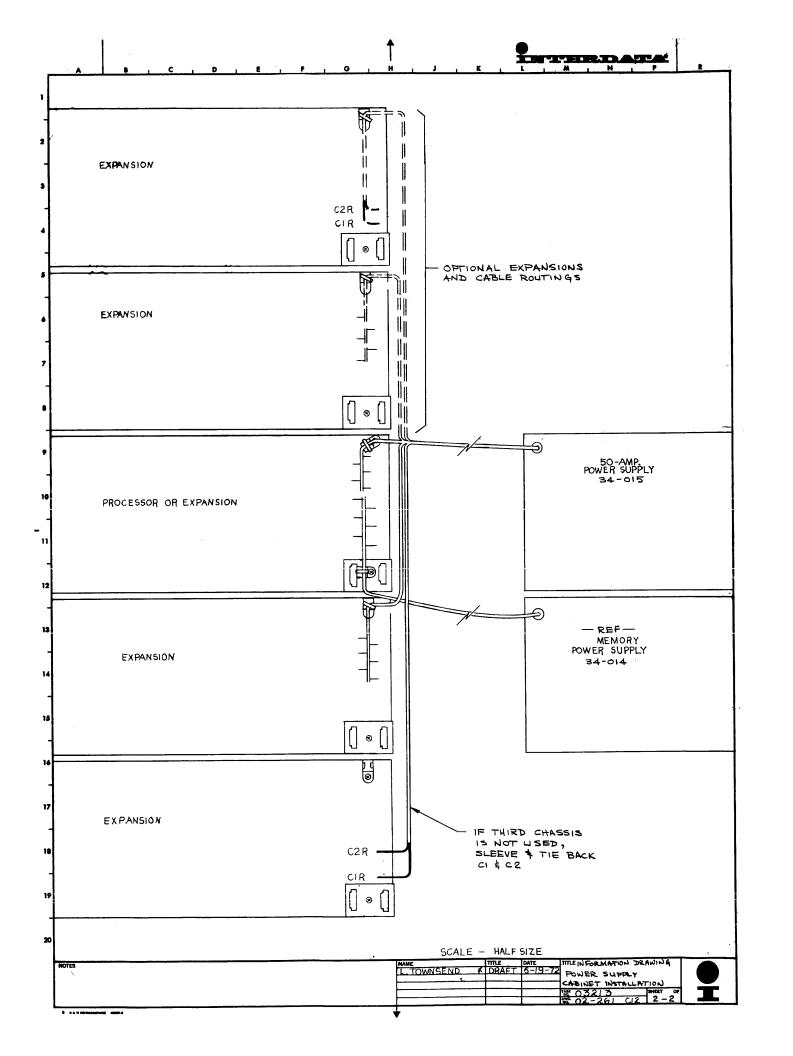

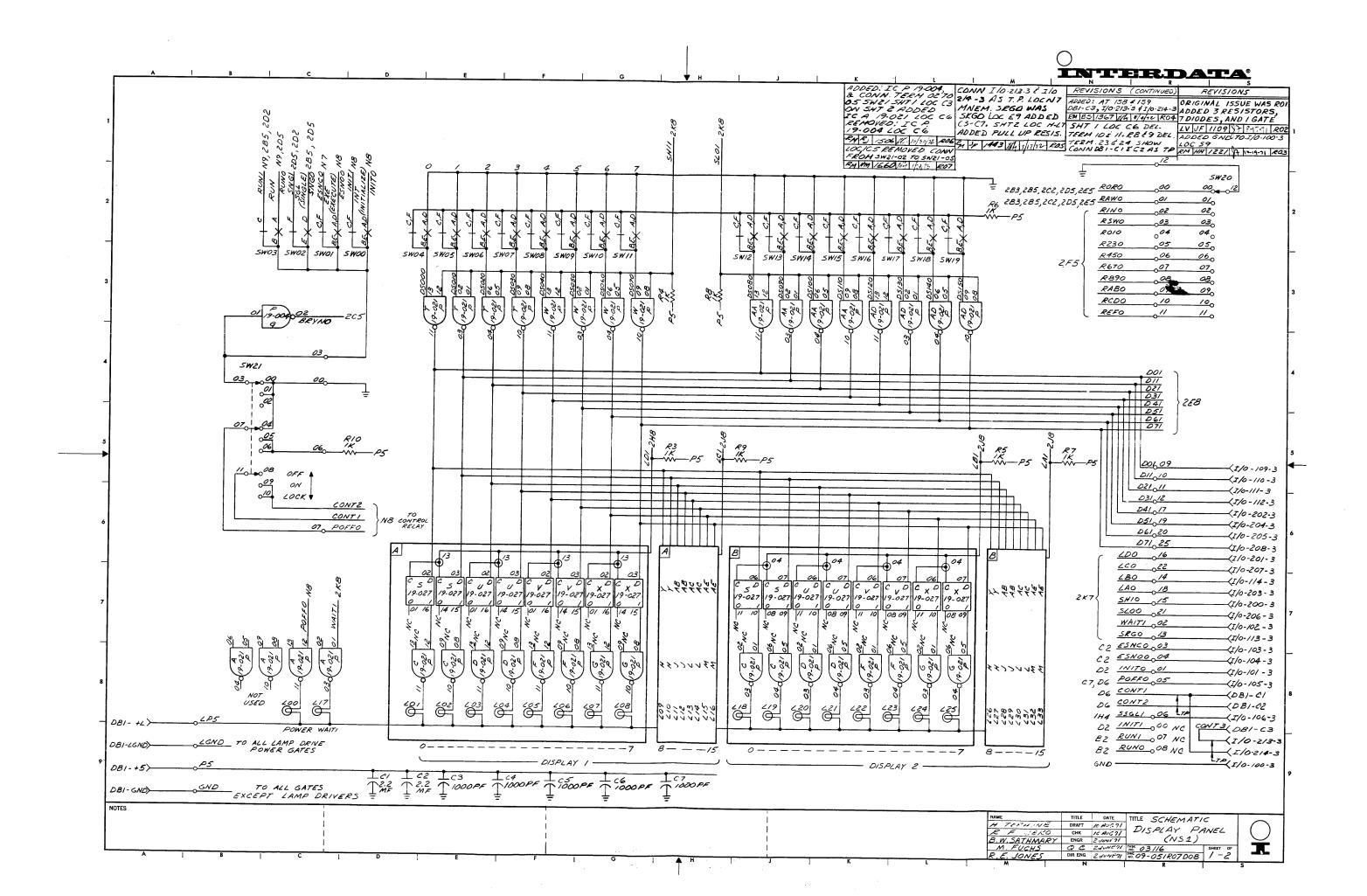

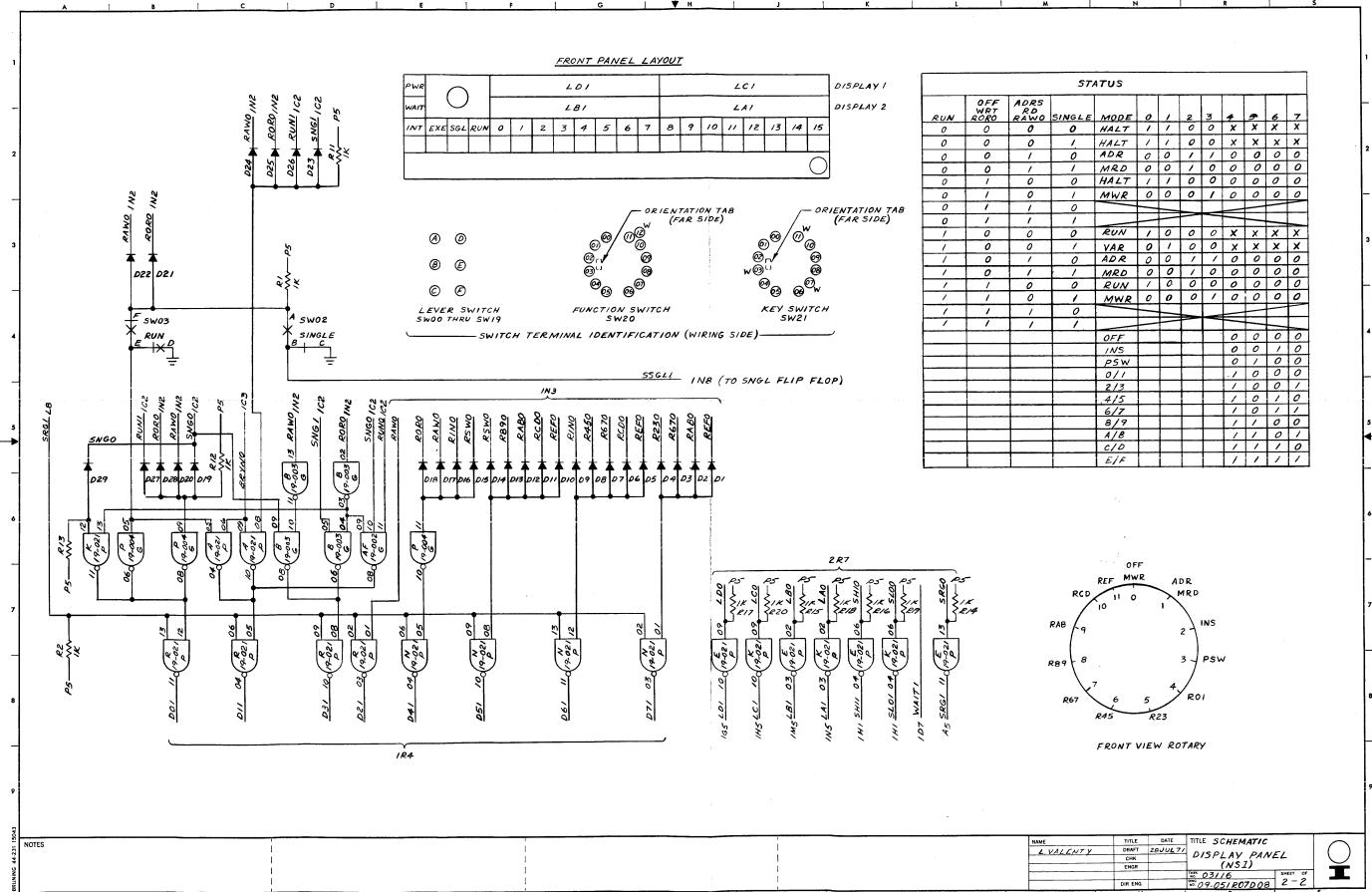

Model 80 Processor (Reference) 01-053D08 **Cable Information** 01-051R03C12 **Central Processing Unit Schematic** 35-403R12D08 Arithmetic Logic Unit Schematic 35-404R06D08 Input/Output Unit Schematic 35-405R09D08 Input/Output Unit Locator 35-405R05C12 Input/Output Unit Locator (M01) 35-405M01D12 **Selector Channel Schematic** 02-232M01D08 Memory Bank Controller Schematic 35-407R07D08 Memory Storage Unit Schematic 02-247R09D08 **Memory Protect Schematic** 02-248R01D08 Memory Protect Locator 35-408R01D03 Model 80 Memory Power Supply Schematic 34-014R03D08 50 Ampere Power Supply Schematic 34-015R02D08 **Power Supply Installation Information** 02-261C12 **External Battery Information** 39-019C20 **Display Panel Schematic** 09-051R07D08

2 Crescent Place, Oceanport, New Jersey 07757

29-280R03S-1-4 (1893, 1905) (1781) (1918, 1919, 1964) (1968, 2014, 2018) (2028, 2047) (2060)

## SUPPLEMENT TO MODEL 80 MAINTENANCE MANUAL

## **Publication Number 29-280R01**

Publication Number 29-280R03 consists of a 29-280R01 Manual and this Supplement.

In General Description 29-280A12, Appendix 1, add:

## **NOTE**

This is a comprehensive list of parts used in INTERDATA equipment. All parts are not used in every system. These parts may or may not be in your particular Processor.

In 01-053R01A21, Sheet 34, Change "AS011" to "AS001".

On Sheet 35, fourth line from top should read:

"IF (AWRT0 AZR01 RZR01) B00:15-0, A00:15-0

In 02-247A21, Sheet 22, Change:

In 02-247A21, Sheet 39, Paragraph 17.1:

Voltage Adjustments should be:

|        | P15   | P22   | P5    | P5S   |

|--------|-------|-------|-------|-------|

| 1.     | 15.3* | 21.0  | 5.10  | 5.10  |

| 2.     | 15.5* | 21.0  | 5.10  | 5.10  |

| 3.     | 15.4  | 19.5* | 5.10  | 5.10  |

| 4.     | 15.4  | 22.5* | 5.10  | 5.10  |

| 5.     | 15.4  | 21.0  | 4.85* | 5.10  |

| 6.     | 15.4  | 21.0  | 5.35* | 5.10  |

| 7.     | 15.4  | 21.0  | 5.10  | 4.85* |

| 8.     | 15.4  | 21.0  | 5.10  | 5.35* |

| Normal | 15.4  | 21.0  | 5.10  | 5.10  |

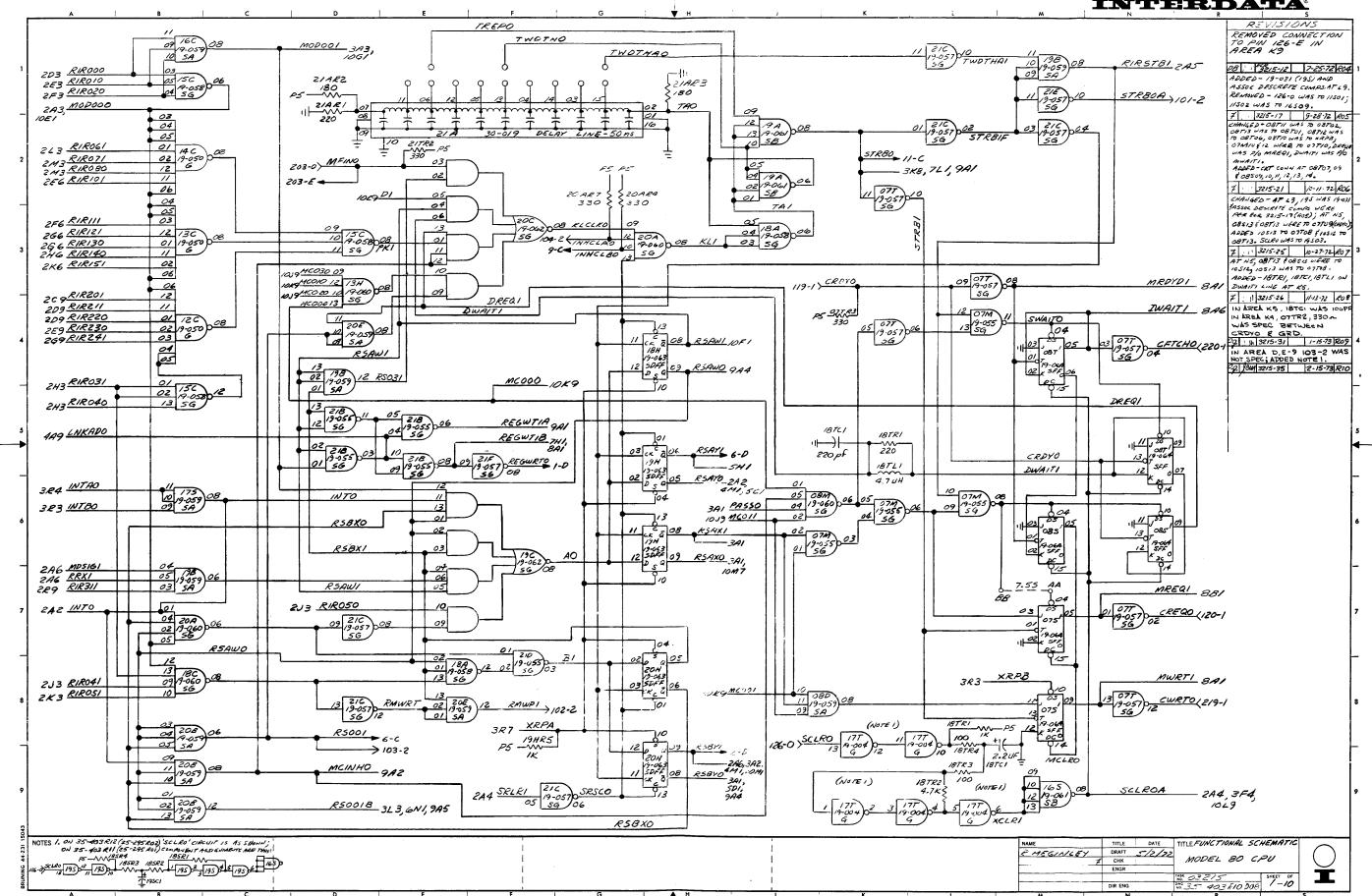

In 35-403R10D08, Sheet 1, Area FG1, Change Mnemonics TREPO to TWDTHO and TWDTHO to TREPO.

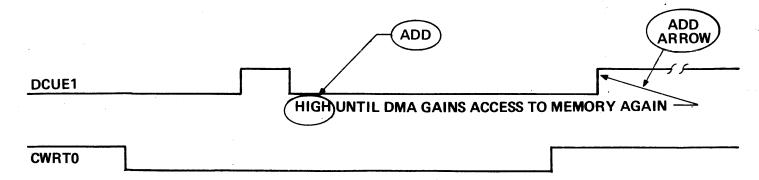

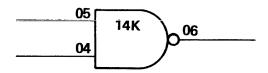

Sheet 3, Area M2 on 14K: Add Pin 6 designation:

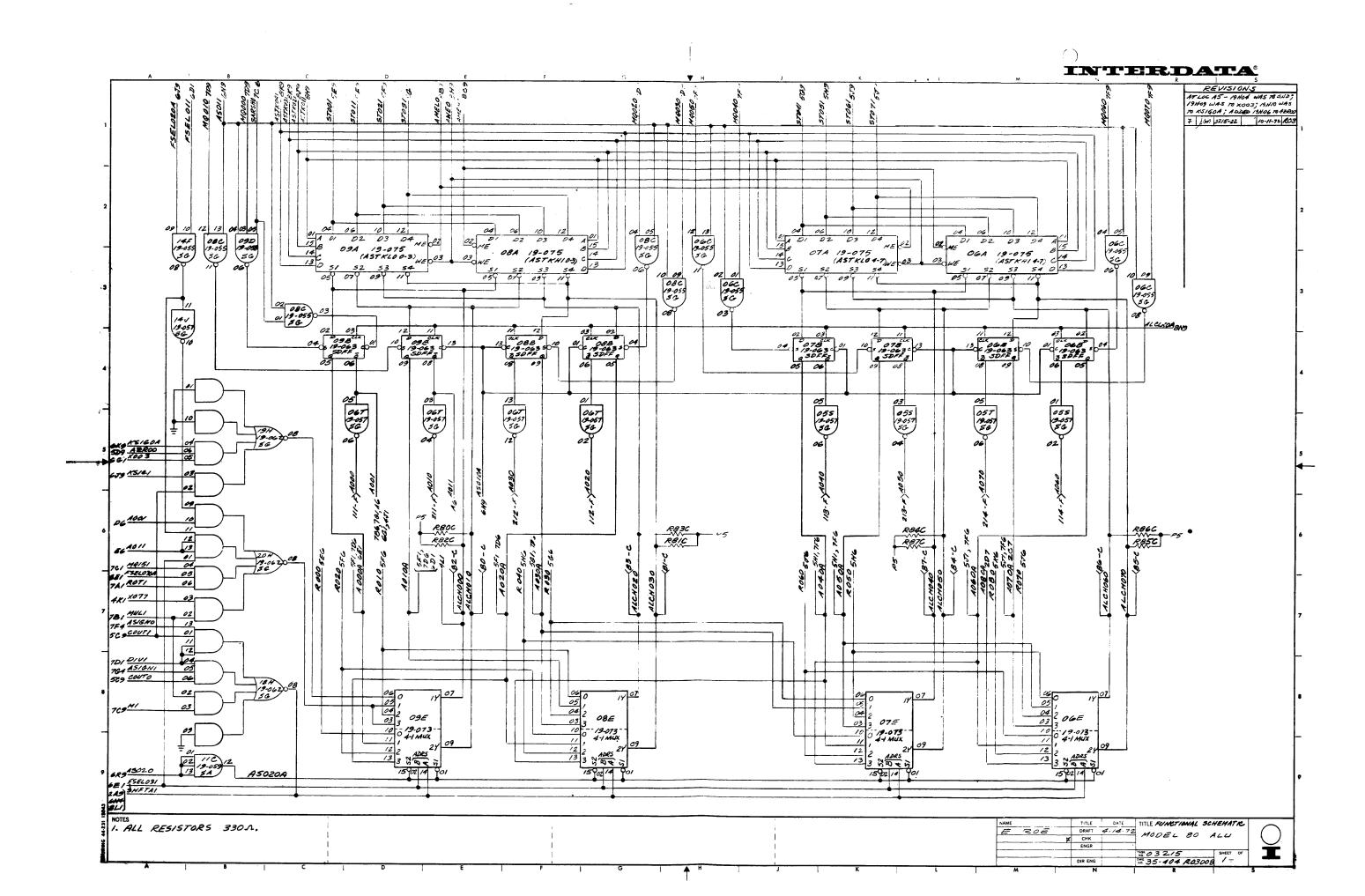

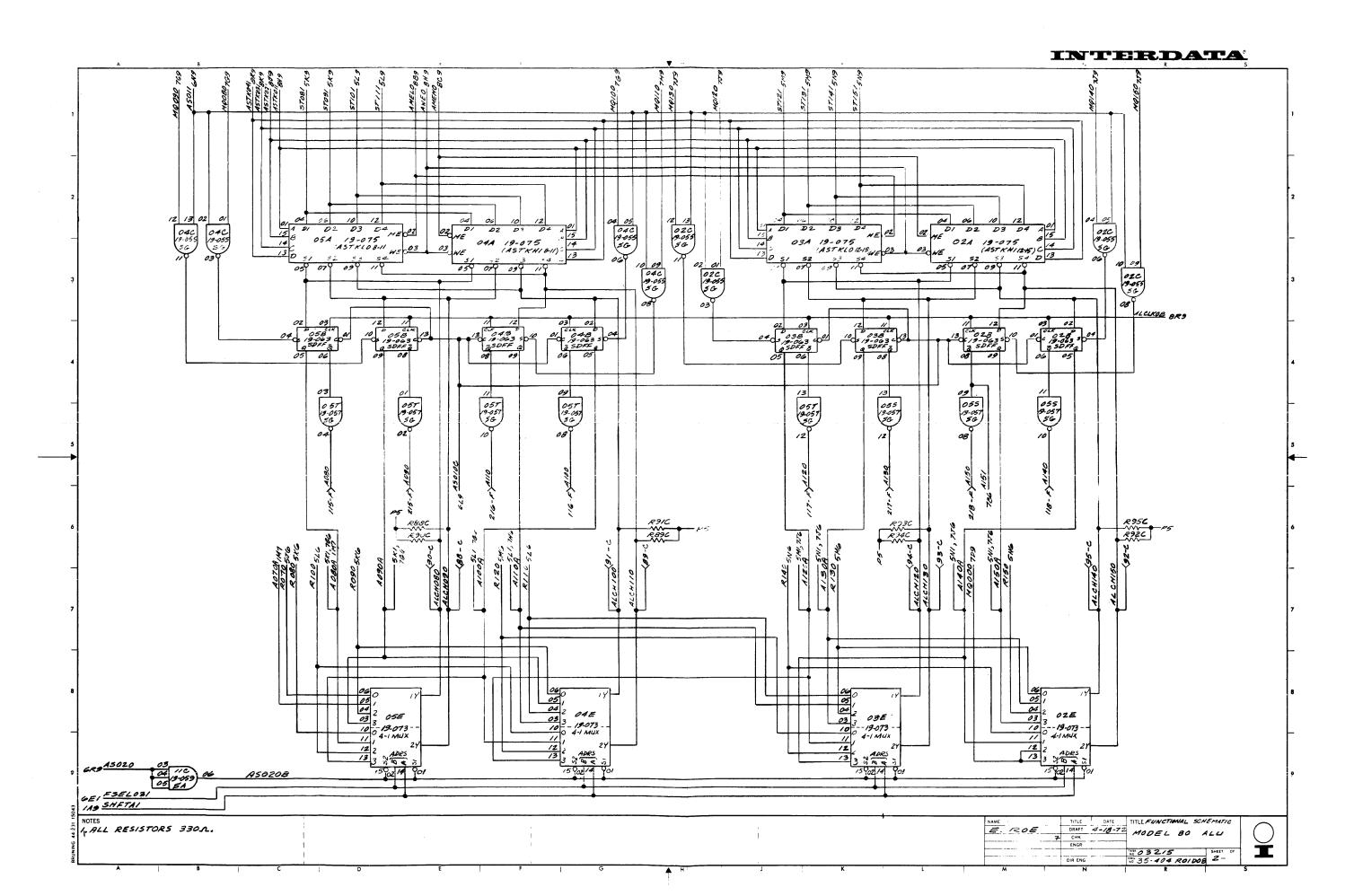

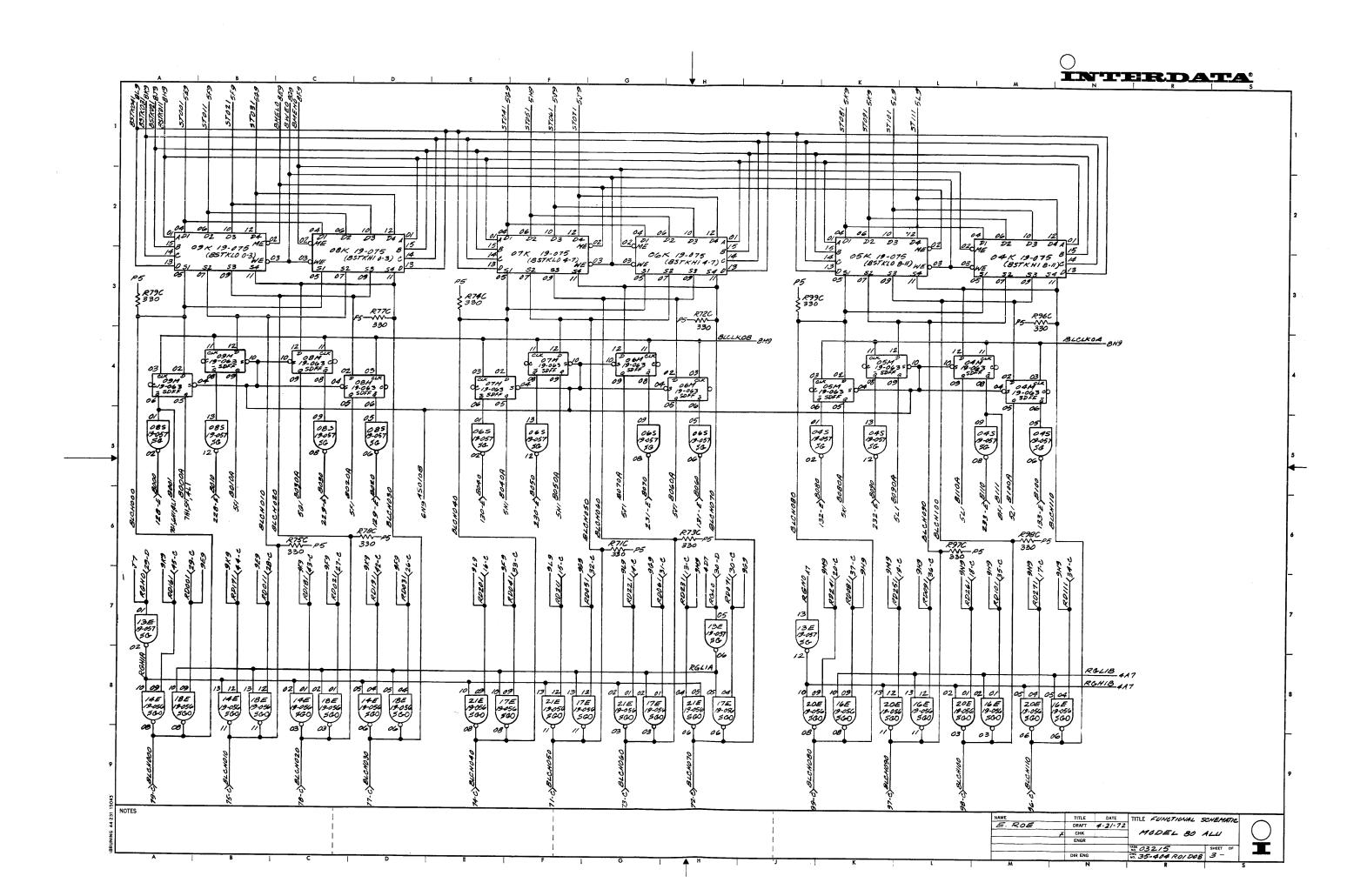

In 35-404R06D08, Sheet 7, Area L4 and 5, Change Mnemonics TREPO to TWDTHO and TWDTHO to TREPO.

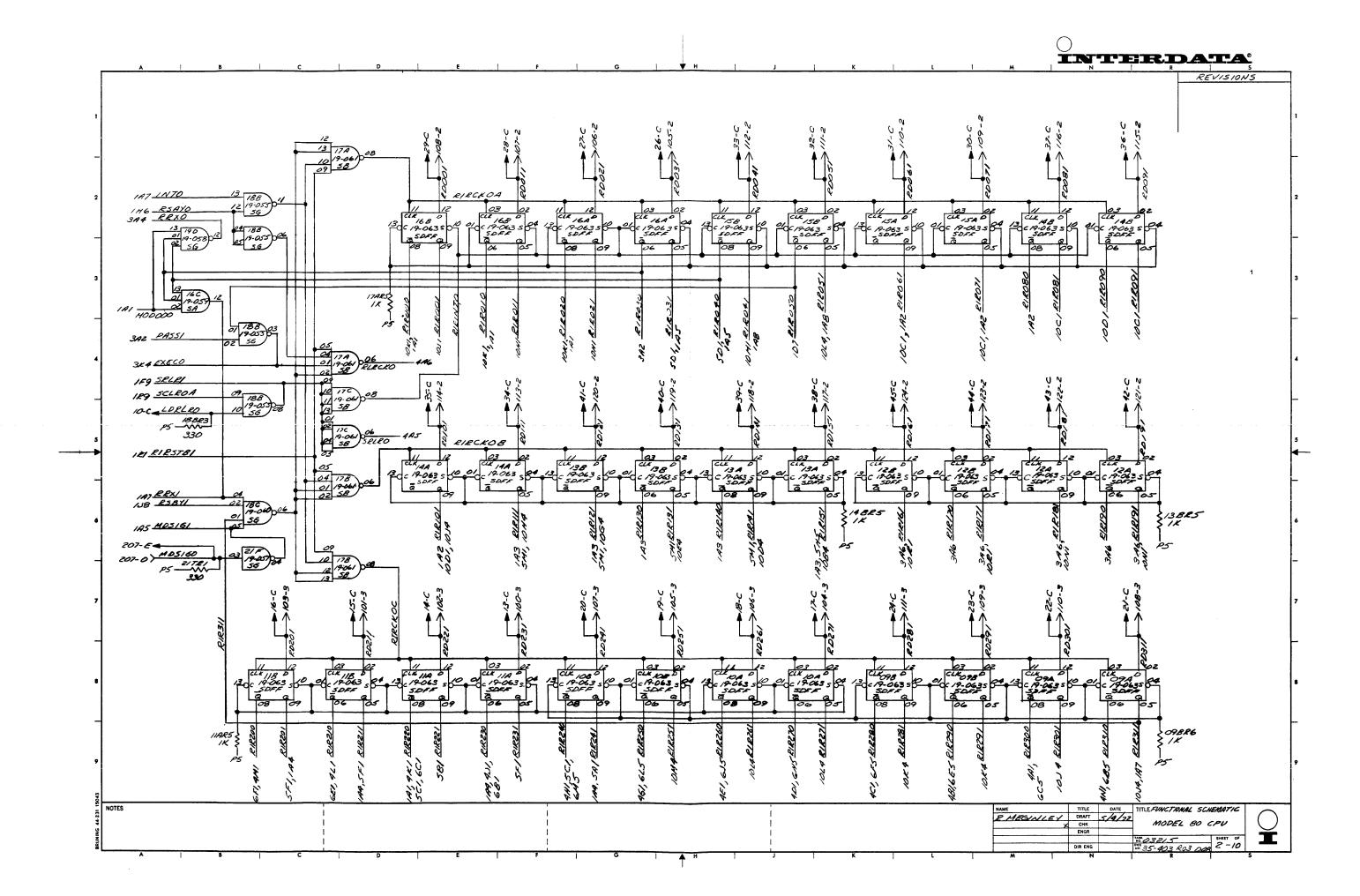

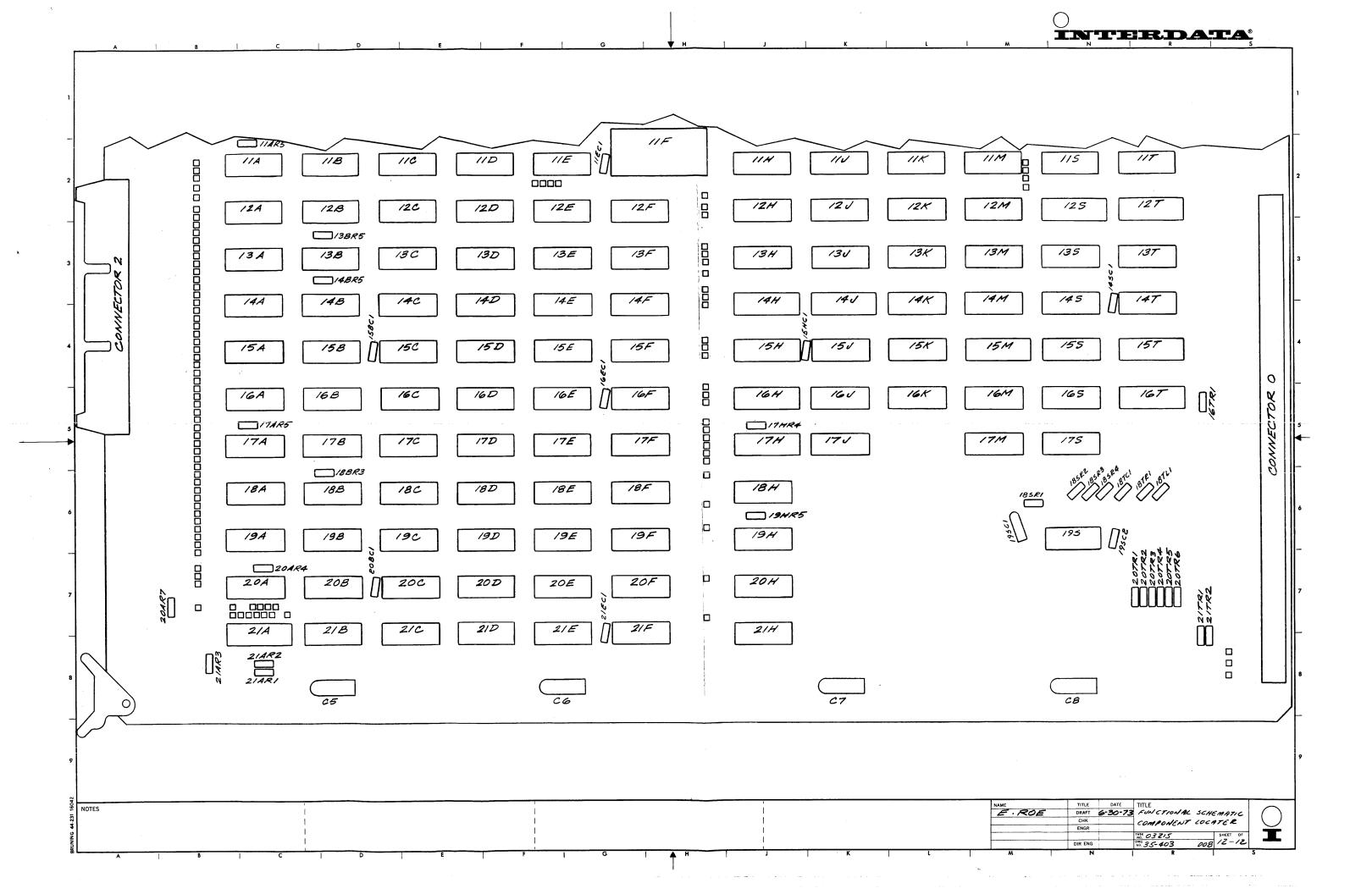

Add ACU Component Locator, Sheets 10 and 11 of 35-404D08 and CPU Component Locator, Sheets 11 and 12 of 35-403D08 to manual.

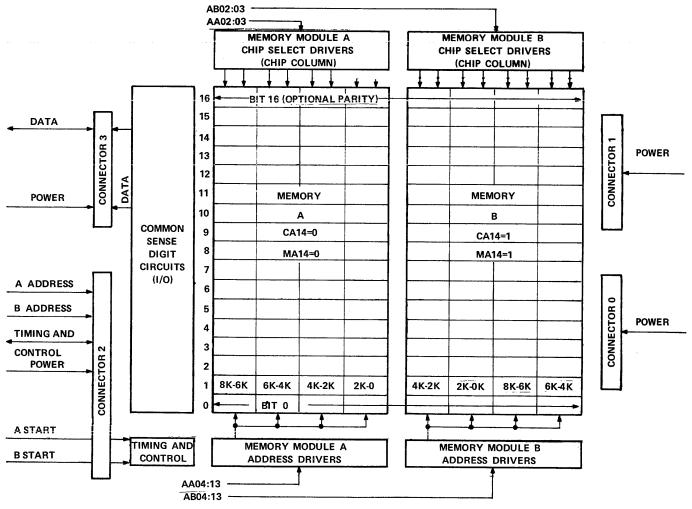

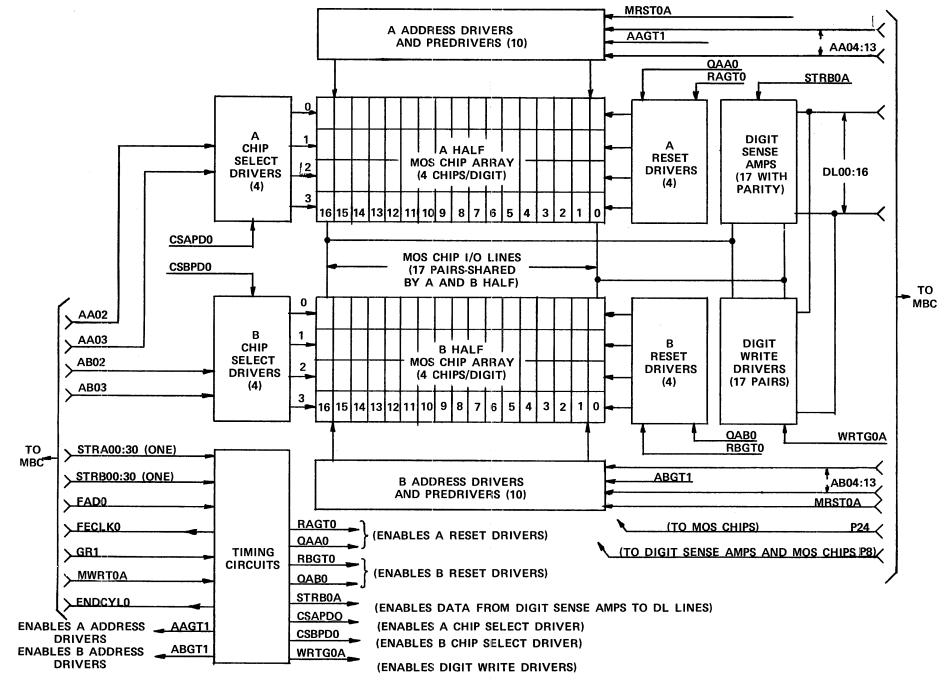

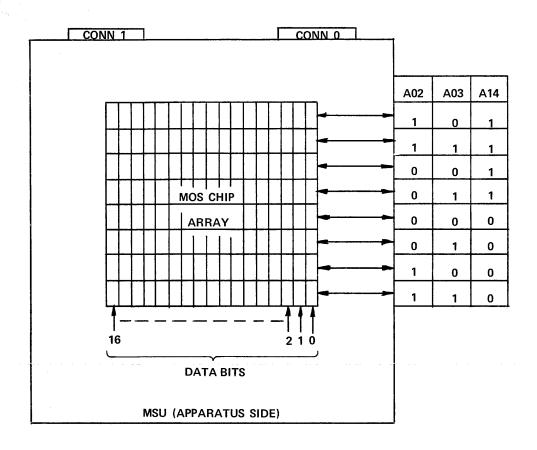

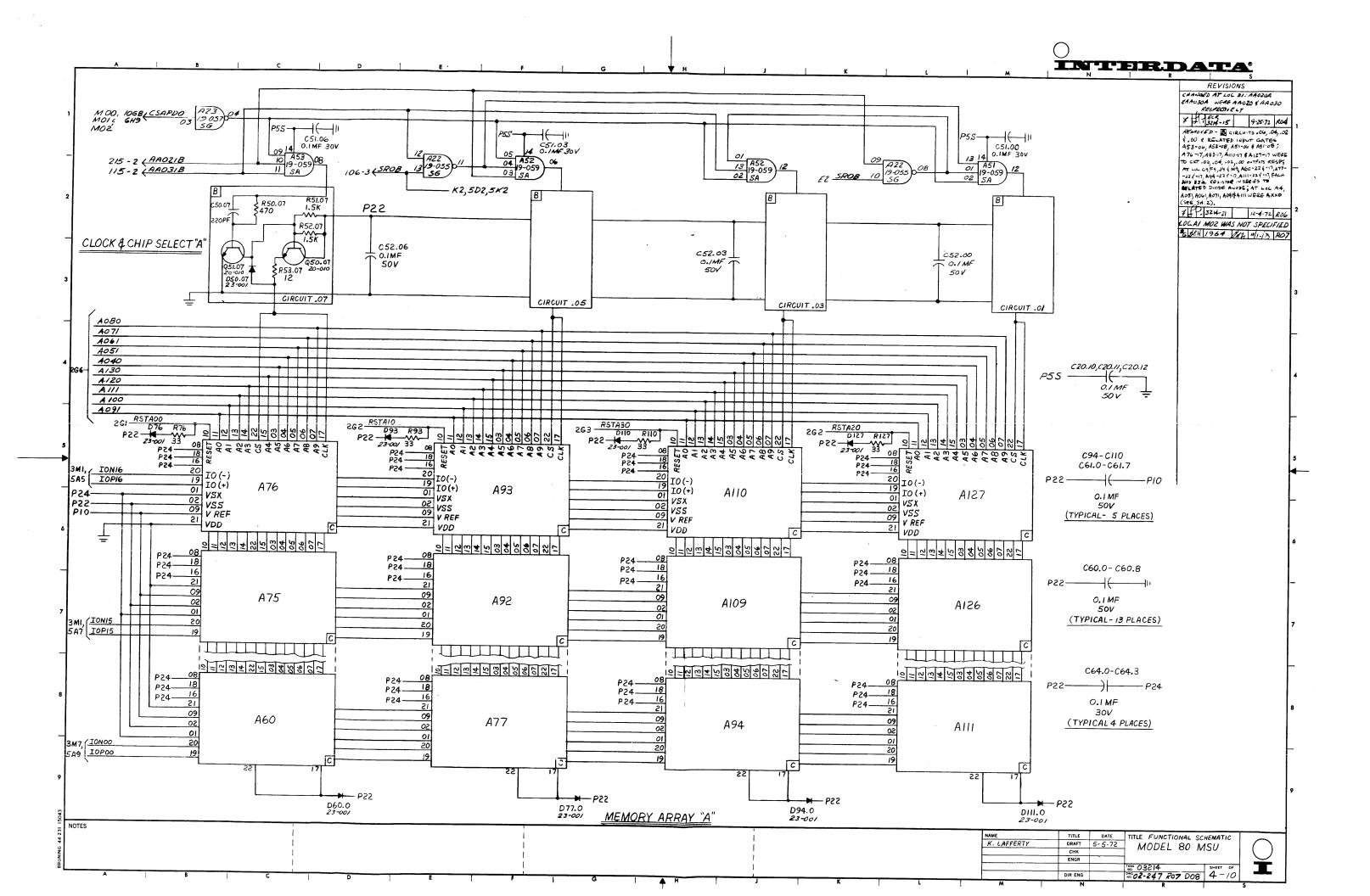

In 02-247A21, Sheet 34, Figure 19: Delete numbers on the four lines between (A)(B) Chip Select Drivers and (A)(B) Half MOS Chip Array.

In 02-247A21, Sheet 39, Paragraph 19.1, in the first and third lines and in Figure 23 title, change 11-127 to 28-015.

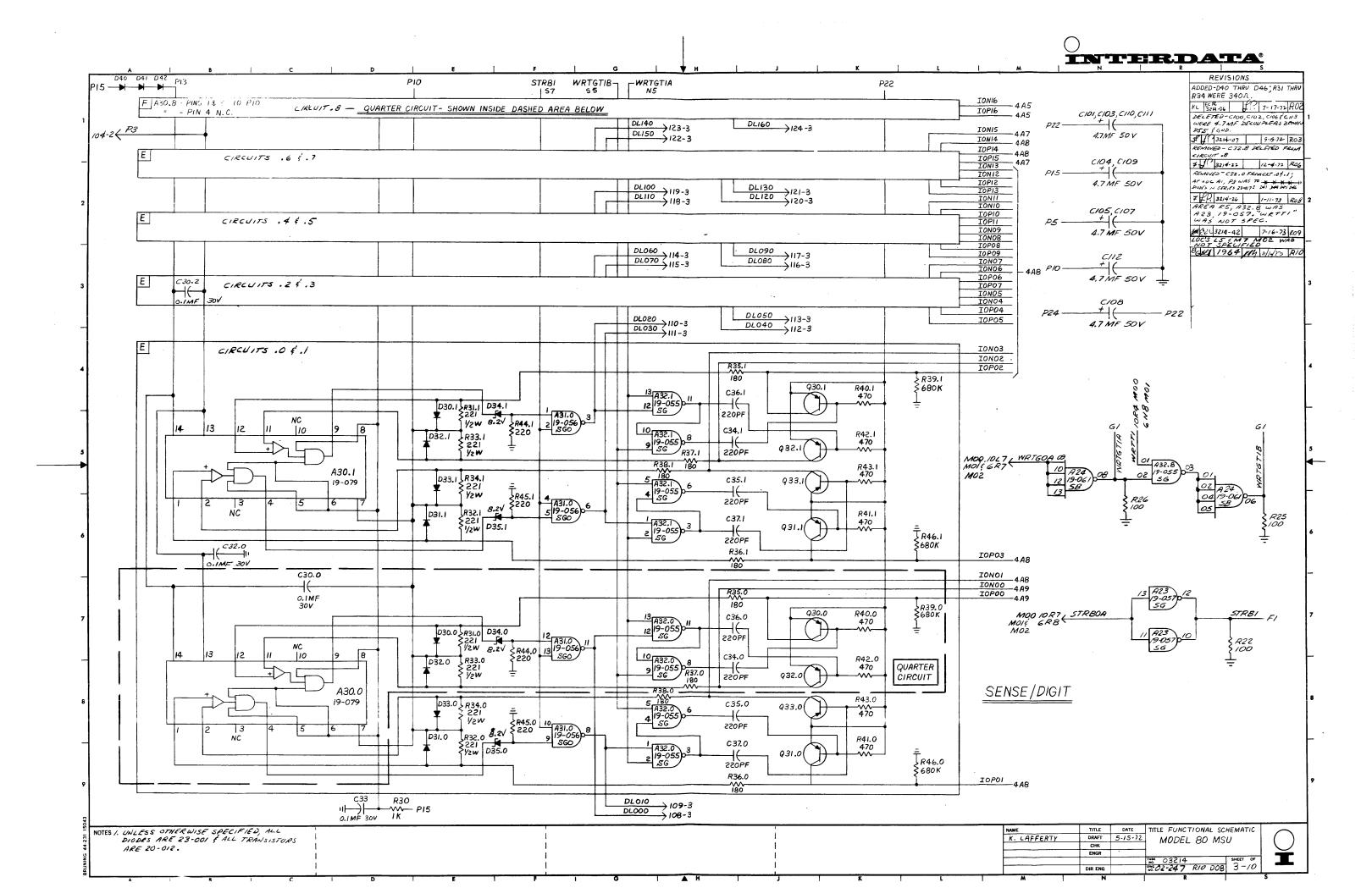

Replace Functional Schematic 02-247R09D08 by 02-247R10D08.

In Functional Schematic 34-014R03D08, Sheet 1, change R135 from 7.5K to 12.7K.

# Replace Functional Schematic 35-407R07D08 by 35-407R12D08

On Functional Schematic 09-051R07D08: Sheet 1, Area C5: Change SWITCH SW21 PIN DESIGNATIONS as follows:

| SW21-03 to SV | V21-1W |

|---------------|--------|

| 07            | 05W    |

| 11            | 09W    |

| 00            | 01     |

| 02            | 03     |

| SW21-04 to SW | V21-05 |

| 05            | 06     |

| 06            | 07     |

| 08            | 09     |

| 09            | 10     |

| 10            | 11     |

Show unused terminals, 04, 08, 12

On Functional Schematic 09-051R07D08, Sheet 1, Area BC8, remove two gates labeled "NOT USED"

On Functional Schematic 02-247R09D08 change the "M01" notation to read "M01 and M02" in the following eight places:

Sheet 1 Area H9, Area A5, Area C5 Sheet 3 Area L5, Area M7 Sheet 4 Area A1 Sheet 5 Area A1 Sheet 7 Area 9F

On Functional Schematic 35-403R12D08 Sheet 3 Area JK1, replace 07J part number with:

NOTE 1 M80 CPU - 07J is 19-047F70 M60 CPU - 07J is 19-084F66

On Functional Schematic 35-404D08 Sheet 0, Area J8, in P. C. Board latest revision box add the notation:

## 35-404M01

On Functional Schematic 35-404D08, Sheet 9, remove "F" vari numbers from all units on this sheet. Add 'see table' note above IC 18D and table below:

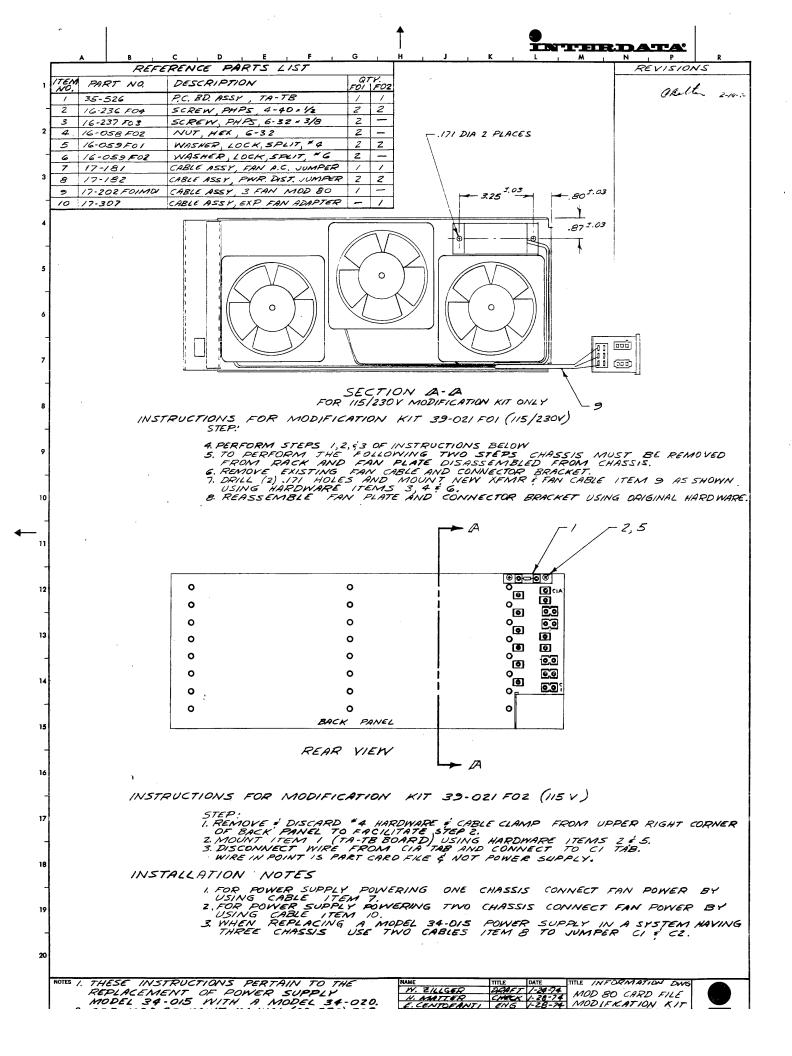

Add Installation Specification 02-261A20 to manual.

Add Kit Information 39-021C12 to manual.

|     | VARIATIC<br>19-084 US |        |

|-----|-----------------------|--------|

| POS | MOD 80                | MOD 60 |

| 18A | F01                   | F34    |

| 17A | F02                   | F35    |

| 16A | F03                   | F36    |

| 15A | F04                   | F37    |

| 14A | F05                   | F38    |

| 21A | F06                   | F39    |

| 20A | F07                   | F40    |

| 19A | F08                   | F41    |

| 18B | F09                   | F42    |

| 17B | F10                   | F43    |

| 16B | F11                   | F44    |

| 15B | F12                   | F45    |

| 14B | F13                   | F46    |

| 21B | F14                   | F47    |

| 20B | F15                   | F48    |

| 19B | F16                   | F49    |

| 18C | F17                   | · F50  |

| 17C | F18                   | F51    |

| 16C | F19                   | F52    |

| 15C | F20                   | F53    |

| 14C | F21                   | F54    |

| 21C | F22                   | F55    |

| 20C | F23                   | F56    |

| 19C | F24                   | F57    |

| 18D | F25                   | F58    |

| 17D | F26                   | F59    |

| 16D | F27                   | F60    |

| 15D | F28                   | F61    |

| 14D | F29                   | F62    |

| 21D | F30                   | F63    |

| 20D | F31                   | F64    |

| 19D | F32                   | F65    |

On Functional Schematic 35-405D08, Sheet 6, Area M8, add 'see Note 2' above 00E. Add Note 2

Connect 00E - 13 to 'B151' - Model 80 Connect 00E - 11 to X5 (108-3) Model 60

## NOTE

DO NOT USE I/O DEVICE NUMBER X'05' IN YOUR SYSTEM FOR ANYTHING OTHER THAN A LOADER STORAGE UNIT CONTROLLER. DEVICE NUMBER X'05' IS RESERVED FOR THE LSU CONTROLLER, A DEVICE WHICH IS TREATED SPECIALLY BY THE HARDWARE ON POWER-UP OR INITIALIZE SEQUENCES, WHICH AUTOMATICALLY LOADS A NEW PSW AND UP TO 2048 BYTES OF MAIN MEMORY. THE HARDWARE ASSUMES IF DEVICE NUMBER X'05' EXISTS IN A SYSTEM THAT IT IS AN LSU AND THE AUTOMATIC PSW AND MEMORY LOAD SEQUENCE OCCUR ON POWER UP. ACCORDINGLY, EXTRAORDINARY RESULTS CAN OCCUR IF DEVICE NUMBER '05' IS ASSIGNED TO ANY OTHER DEVICE CONTROLLER.

# QUICK REFERENCE INDEX

To aid in quickly locating a particular section, the index marks on the edge of this page are aligned with similar marks at the beginning of each section.

| GENERAL DESCRIPTION |  |

|---------------------|--|

| PROCESSOR           |  |

| MEMORY              |  |

| MEMORY PROTECT      |  |

| SELECTOR CHANNEL    |  |

| POWER SYSTEM        |  |

| DRAWINGS            |  |

# **GENERAL DESCRIPTION**

# MODEL 80 GENERAL DESCRIPTION

## Contents

| 1.     | INTRO | DDUCTION                                           | 1 |

|--------|-------|----------------------------------------------------|---|

| 2.     | SCOP  | E                                                  | 1 |

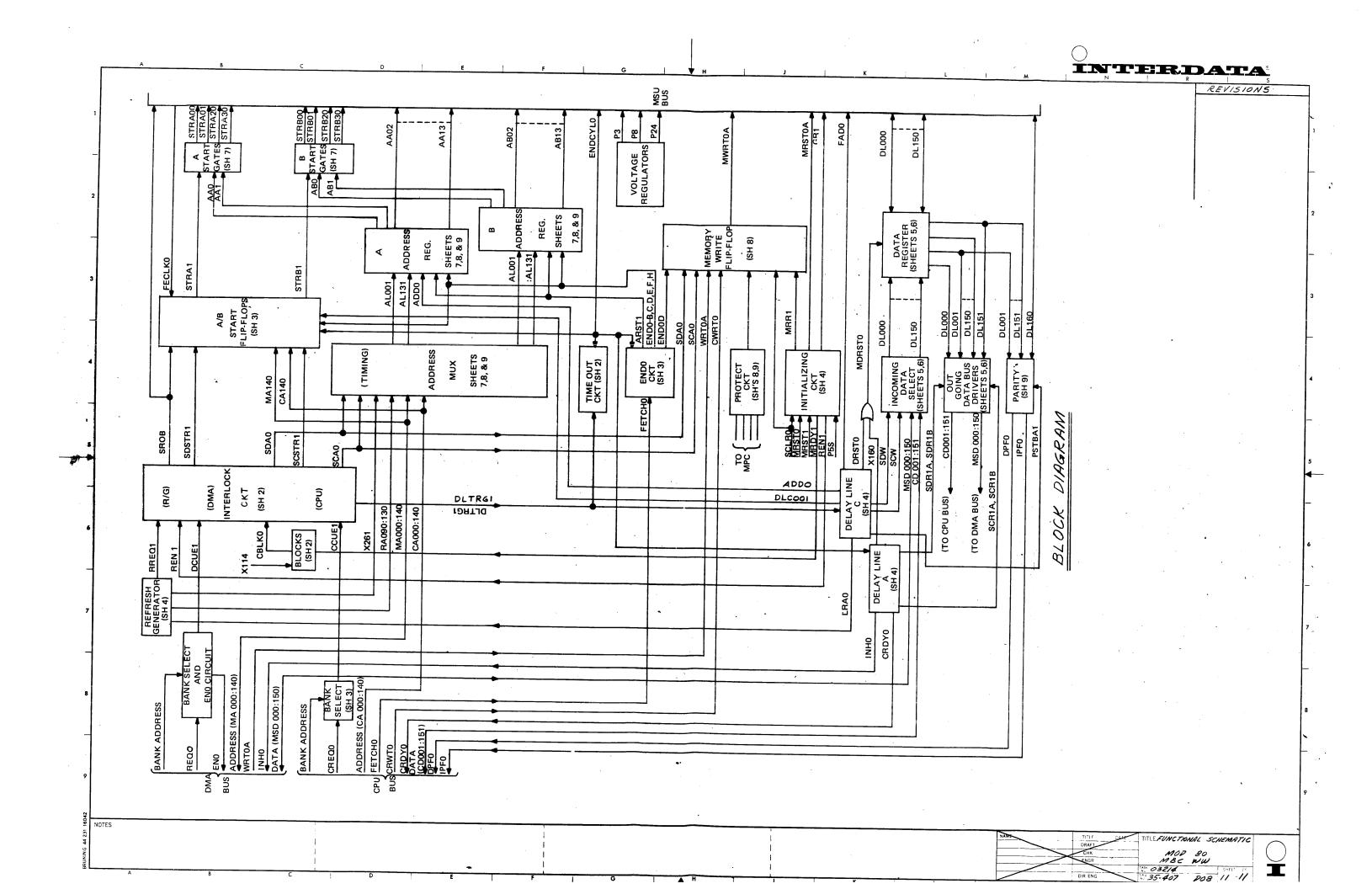

| 3.     | BLOC  | K DIAGRAM                                          | 2 |

| 4.     | DOCU  | MENTATION                                          | 2 |

|        | 4.2 P | umber Notation Part Numbering System Pawing System | 3 |

|        |       | ILLUSTRATIONS                                      |   |

| Figure | 1.    | Model 80 Simplified Block Diagram                  | 2 |

| Figure | 2.    | Part Number Format                                 | 3 |

| Figure | 3.    | Example of a Schottky Buffer                       | 6 |

| Figure | 4.    | Example of a Logic Board Layout                    | 6 |

| Figure | 5.    | Connector Pin Numbering                            | 7 |

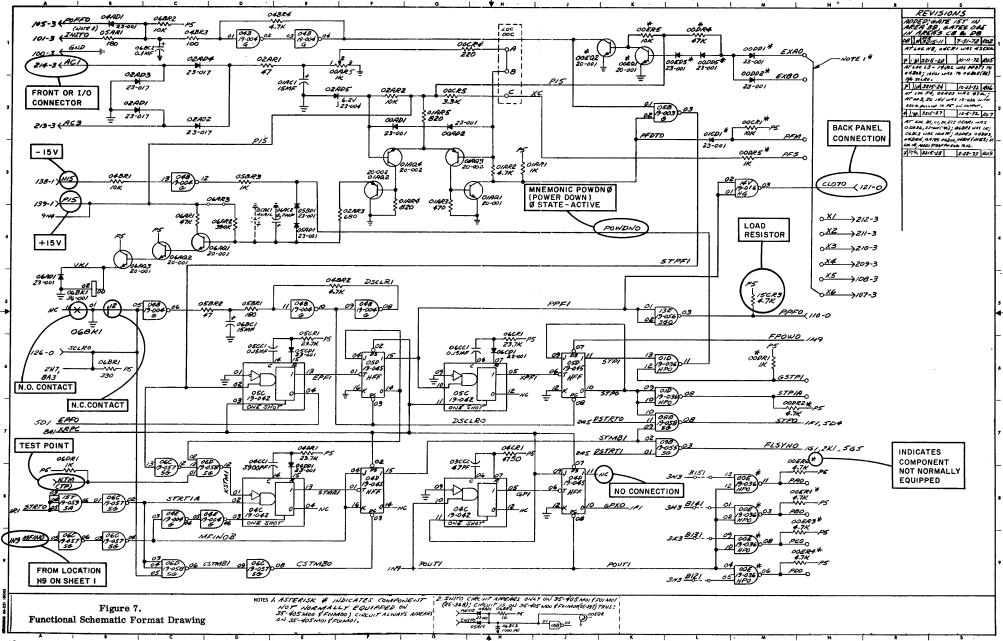

| Figure | 6.    | Functional Schematic Format Drawing                | 9 |

# MODEL 80 GENERAL DESCRIPTION

The Model 80 combines advanced circuitry and packaging designs to give the user a price/performance optimized machine. The Model 80 is completely upward compatible with INTERDATA Model 3, 4, 5 and 70 Processor user instructions, interrupt handling, input/output formats and control sequencing. Because of this compatability, the Model 80 can use the wide range of existing software and peripheral devices.

The Model 80 offers a comprehensive set of 113 instructions making the system both easy to program and efficient to operate. Through multi-function instructions and direct addressing, coding and debugging time is reduced to a minimum.

Memory is addressable to the eight-bit byte level. Memory is expandable from the basic 16,384 bytes to 65,536 bytes. All memory is directly addressable with the primary instructions, no paging or indirect addressing is required. Of the 16 (16-bit) General Registers used as Accumulators, 15 can also be used as Index Registers. Register-to-Register instructions permit operations between any of the 16 General Registers, eliminating redundant loads and stores.

The Protect Mode of the Model 80 enables Memory Protect and detection of Privileged instructions, and can be activated under program control. This mode is invaluable in process control, data communication, and time-sharing operations to guarantee that a running program cannot interfere with the integrity of the system.

The Model 80 also provides a flexible Input/Output system in addition to conventional means of programmed I/O. In the Automatic I/O Service Mode, the Processor acknowledges all I/O interrupts and automatically performs much of the overhead prior to activating the Interrupt Service Routine. In conjunction with the Automatic I/O Service, an I/O Channel can perform data transfers and signal counting without interrupting the running program until the specified sequence is completed.

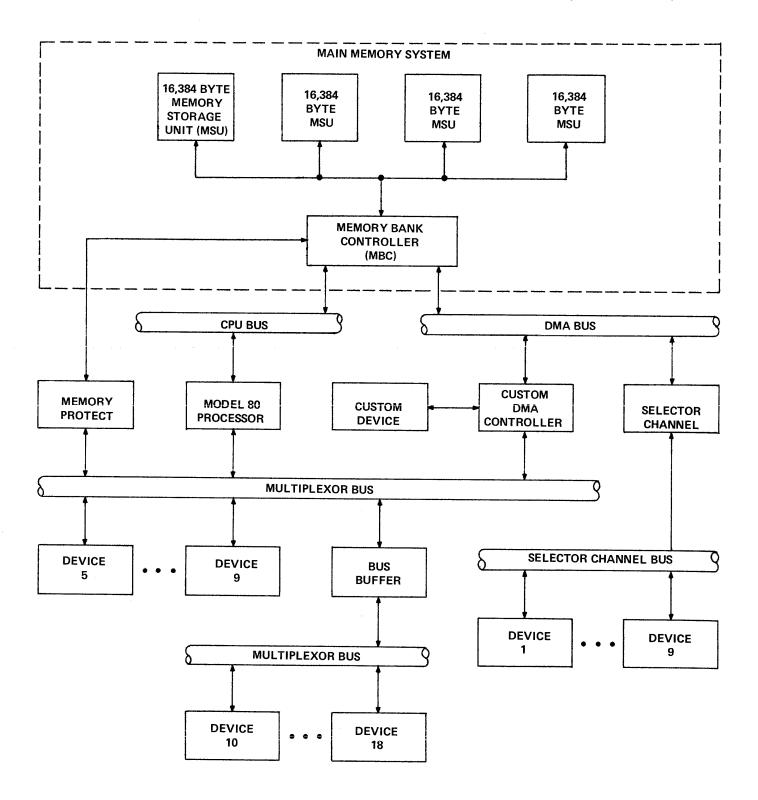

Up to four Direct Memory Access Channels (DMAC) can be added to a Model 80 Memory System. These channels operate over a private Memory Bus through a Direct Memory Access Port which is built into the Memory Controller. Two types of Direct Memory Access Channels can be used with the Model 80 System: The Selector Channel, which permits direct data transfer between any standard oriented INTERDATA device controller and memory; and the Direct Memory Access Channel custom designed by the user for special applications.

## 2. SCOPE

This specification is intended to enable the digital technician to understand the INTERDATA documentation system. Number Notation, the Part Numbering System, and the Drawing System are described. Illustrations are provided to help understand these systems. Other publications which may be of interest to Model 80 users are shown in Table 1.

A cross reference between INTERDATA part numbers and standard industry part numbers for the ICs and transistors is found in Appendix 1.

TABLE 1. RELATED PUBLICATIONS

| Title                                      | Publication Number |

|--------------------------------------------|--------------------|

| Universal Clock Instruction Manual         | 29-265             |

| Users Handbook                             | 29-261             |

| Model 80 Maintenance Manual                | 29-280*            |

| Multiplexor Bus Buffer Instruction Manual  | 29-267             |

| 8 Line Interrupt Module Instruction Manual | 29-268             |

| -                                          |                    |

<sup>\*</sup>This General Description is a part of 29-280.

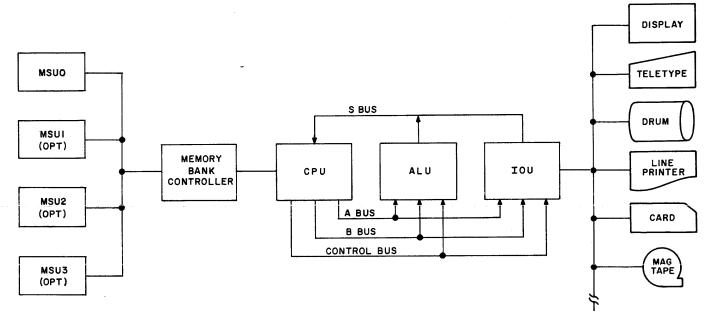

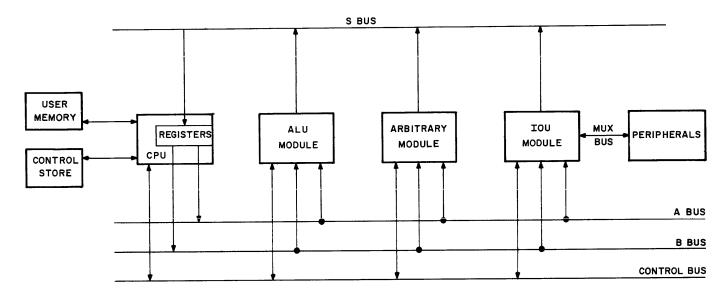

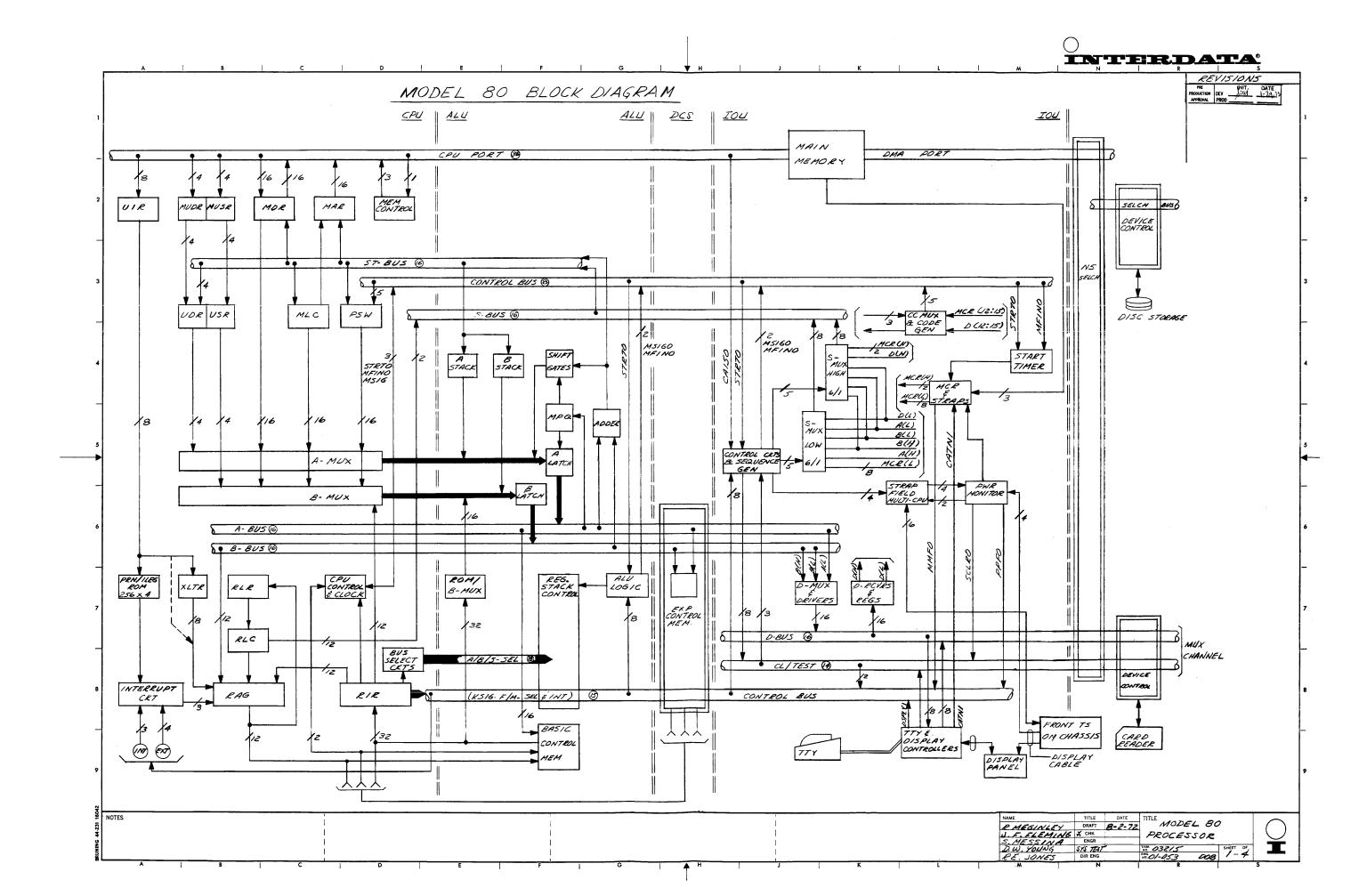

## 3. BLOCK DIAGRAM

A Model 80 simplified block diagram is shown in Figure 1. The basic Model 80 is a 16-bit digital computer contained on 5 PC boards:

| Part No. | Description            | Card File<br>Position |

|----------|------------------------|-----------------------|

| 35-406   | Memory Storage Unit    | 3                     |

| 35-407   | Memory Bank Controller | 4                     |

| 35-405   | IOU Board              | 5                     |

| 35-404   | ALU Board              | 6                     |

| 35-403   | CPU Board              | 7                     |

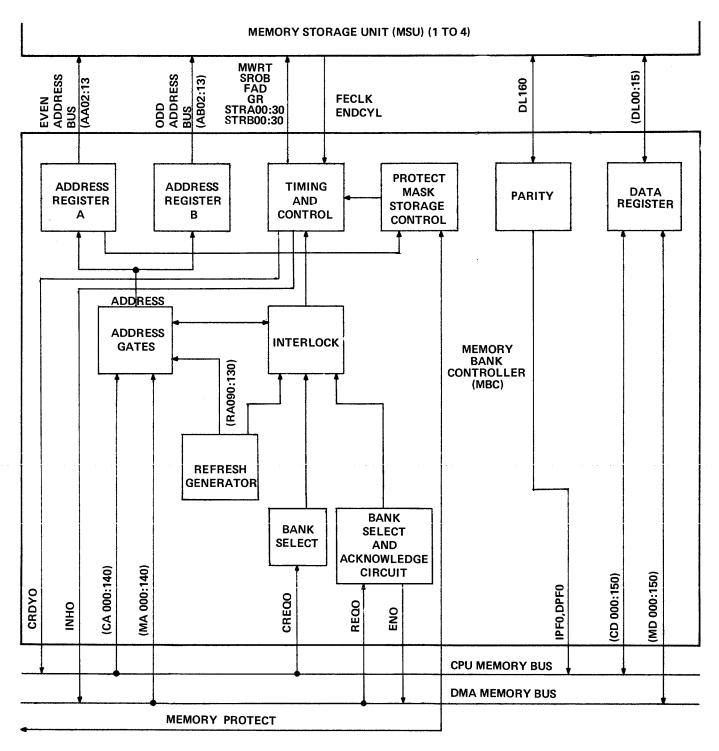

Figure 1. Model 80 Simplified Block Diagram

## 4. DOCUMENTATION

This section describes the style and conventions used with INTERDATA documentation.

## 4.1 Number Notation

The most common form of number notation used in INTERDATA documentation is hexadecimal notation. In this system, groups of four binary digits are represented by a single hexadecimal digit. Table 2 lists the hexadecimal characters employed.

| Binary | Decimal | Hexadecimal | Binary | Decimal | Hexadecimal | Binary | Decimal | Hexadecimal |

|--------|---------|-------------|--------|---------|-------------|--------|---------|-------------|

|        |         |             |        |         |             |        |         |             |

| 0000   | 0       | 0           | 0110   | 6       | 6           | 1100   | 12      | C           |

| 0001   | 1       | 1           | 0111   | 7       | 7           | 1101   | 13      | D           |

| 0010   | 2       | 2           | 1000   | 8       | 8           | 1110   | 14      | E           |

| 0011   | 3       | 3           | 1001   | 9       | 9           | 1111   | 15      | F           |

| 0100   | 4       | 4           | 1010   | 10      | A           |        | İ       | İ           |

| 0101   | 5       | 5           | 1011   | 11      | В           |        |         |             |

TABLE 2. HEXADECIMAL NOTATION DATA

To differentiate between decimal and hexadecimal numbers, hexadecimal numbers are preceded by the letter "X", and the number is enclosed in single quotation marks. Examples of hexadecimal numbers are: X'1234', X'2EC6', X'A340, X'EEFA', and X'10B9'.

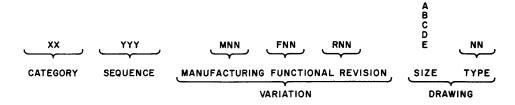

### 4.2 Part Numbering System

INTERDATA parts, drawings, and publications employ a common numbering system. The part number and drawing numbers for drawings which describe the part are related. The publication number is also often related to the part number of the device or program described. Figure 2 shows the format used for INTERDATA part numbers. The fields are described in the following paragraphs.

Figure 2. Part Number Format

4.2.1 <u>Category Field.</u> The two-digit Category number indicates the broad class or category to which a part belongs. Typical examples of category number assignments are:

| 01 - Basic Hardware Systems         | 13 - Panels                           |

|-------------------------------------|---------------------------------------|

| 02 - Basic Hardware Expansions      | 17 - Wire and Cables                  |

| 03 - Basic Software Systems         | 19 - Integrated Circuits              |

| 04 - Basic Software Packages        | 20 - Transistors                      |

| 05 - Micro-Programs                 | 27 - Peripheral Equipment             |

| 06 - Test Programs                  | 29 - Manuals                          |

| 07 - Subroutines of General Utility | 34 - Power Supplies                   |

| 10 - Spare Parts Packages           | 35 - Assembled Printed Circuit Boards |

| 12 - Card File Assemblies           | 36 - Electro-Mechanical Devices       |

4.2.2 <u>Sequence Field.</u> The Sequence number identifies a particular item within the category. Sequence numbers are assigned serially, and have no other significance.

# NOTE

The Sequence Field, like all other part number fields, may be lengthened as required. The field lengths shown on Figure 2 are minimum lengths (insignificant zeros must be added to maintain these minimums).

4.2.3 Manufacturing Variation Field. The optional Manufacturing Variation Field consists of the letter "M" followed by two digits.

## NOTE

A part number must contain a Category number and a Sequence number. All other fields are optional.

The M Field is used to distinguish between parts which are electrically and mechanically equivalent (interchangeable), but which vary in method of manufacture. For example, if leads are welded instead of soldered on an assembly, the M Field changes.

An important exception to the meaning of the M Field exists for categories related to software. Here the M Field number, when used, indicates the form in which a particular program is presented. For example, define a program as a set of machine instructions. These same identical instructions may be presented on punched cards, paper tape, or magnetic tape; and for any of these they could be in symbolic form. Thus, there are many ways to represent the same identical program. These ways are identified by the M Field numbers as follows:

M01 - Symbolic Punched Cards

M02 - Relative Binary Punched Cards

M03 - Absolute Binary Punched Cards

M04 - Symbolic Magnetic Tape

M05 - Relative Binary Magnetic Tape

M06 - Absolute Binary Magnetic Tape

M07 - Symbolic Punched Paper Tape

M08 - Relative Binary Punched Paper Tape

M09 - Absolute Binary Punched Paper Tape

M10 - Bootstrap Binary Object Punched Paper Tape

M11 - Read-Only-Memory (ROM) Absolute Binary Object Punched Paper Tape

M12 - ROM Wiring and Test Set (ROMWATS) Wiring Punched Paper Tape

M13 - ROMWATS Check Punched Paper Tape

M14 - Éight-Bit Paper Tape

M15 - DROM Absolute Binary Object Punched Paper Tape

M16 - Relocatable Non-Zoned Loader Format Paper Tape

M17 - Absolute Non-Zoned Loader Format Paper Tape

M18 - Non-Zoned Established Task Object Tape

- 4.2.4 <u>Functional Variation Field.</u> The optional Functional Variation Field consists of the letter "F" followed by two digits. The F Field is used to distinguish between parts which are not necessarily electrically or mechanically equivalent, but which are described by the same set of drawings. For example, a power supply may be strapped internally to operate on either 110 VAC or 220 VAC. Except for this strap, all power supplies of this type are identical. Therefore, strapping option is easily described by a note on the assembly and test specification drawings.

- 4.2.5 Revision Field. The optional Revision Field consists of the letter "R" followed by two digits. The R Field is used to indicate minor electrical or mechanical changes to a part which do not change the part's original character. R Field changes often reflect improvements. A part with a revision level HIGHER than the one specified will work. A part with a revision level LOWER than specified should not be used.

- 4.2.6 <u>Drawing Field.</u> The optional Drawing Field consists of a letter from "A" to "E" followed by two digits. The letter indicates the size of the original drawing. The sizes for each letter are:

A -  $8\frac{1}{2}$ " X 11"

B - 11" X 17"

C - 17" X 22"

D - 22" X 34"

E - 34" X 44"

The two digits indicate the drawing type as follows:

01 - Parts List

02 - Machine Details

03 - Assembly Details

05 - Art Details

06 - Wire Run List

08 - Schematic

09 - Test Specification

10 - Purchase Specification

11 - Bill of Material

12 - Information

13 - Program Listing

14 - Abstracts

15 - Program Description

16 - Operating Instructions

17 - Program Design Specification

18 - Flow Charts

19 - Product Specification

20 - Installation Specification

21 - Maintenance Specification

22 - Programming Specification

4.2.7 Examples. The following list provides some examples of the part numbering system. The numbers were arbitrarily selected, and in most cases are fictitious.

35-060 The 60th printed-circuit board assigned a part number under this system.

35-060M01 A printed circuit board electrically and mechanically interchangeable with the 35-060, but differing in method of manufacture.

35-060F01 A printed-circuit board not electrically and mechanically interchangeable with the 35-060, but described by the same set of drawings.

35-060R01 A revised 35-060 printed-circuit board. Probably supercedes the 35-060.

35-060A01 The  $8\frac{1}{2}$  by 11 inch parts list for a 35-060.

35-060B08 The 11 by 17 inch schematic for a 35-060.

06-072 The 72nd utility program assigned a part number.

06-072A13 An  $8\frac{1}{2}$  by 11 inch listing of the 06-072 program.

06-072M03 An absolute binary deck of punched cards for the 06-072 program.

06-072A12 An  $8\frac{1}{2}$  by 11 inch information drawing on the 06-072 program. Probably a part of the program.

The 60th manual assigned a number under this system. Note that this number is not referenced in any way to the part number of equipment described in the manual.

# 4.3 Drawing System

This section describes the drawings provided with INTERDATA equipment. Note that drawings provided with peripheral devices and other purchased items may vary from the system described in this section.

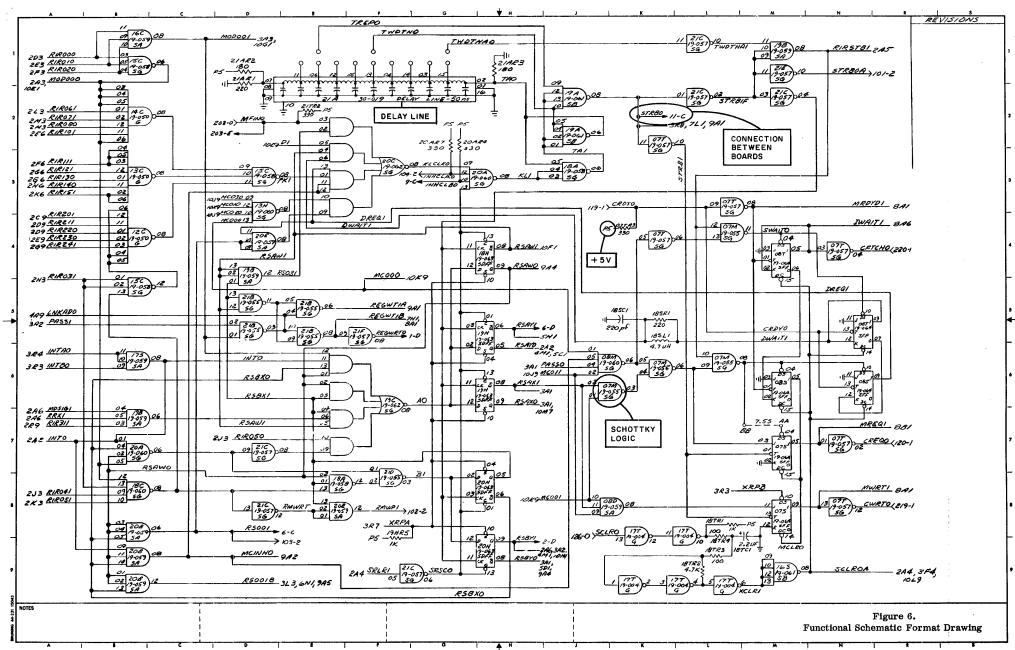

A digital system may be divided into a collection of functionally independent circuits such as memory, Processor, and I/O device controllers. These circuits may or may not be saleable units in their own right, but in the electrical sense they are essentially self contained and capable of performing their function with minimum dependence on other functional circuits in the system. Hence a functional circuit is treated as a building block. Each functional circuit is described electrically by a detailed functional schematic. Each schematic contains a variety of information including type and location of discrete integrated circuits (IC's), pin connections, all interconnections within the schematic connector pin numbers and connections to other schematics. Further, the schematics are drawn to reflect, in an orderly fashion, all logical operations performed by the circuits. Generally, symbols used on schematics conform to MIL-STD-806B.

# Registers are named according to the following rules:

- 1. The register mnemonic name has a maximum of three letters.

- 2. Each bit in the register is numbered, usually starting at 00 on the left, or most significant position, and continuing to N-1 on the right, where N is the number of bits in the register.

- 3. The 00 bit is the Most Significant Bit and the N-1 is the Least Significant Bit.

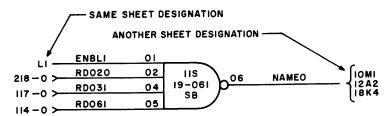

The IC's, mounted directly on the logic board, are represented on the schematic drawings by logic symbols. Each symbol contains the reference designation, device part number (category and sequence), and symbol mnemonic designation. Refer to Figure 3.

Figure 3. Example of a Schottky Buffer

The designations, numbers, and references shown in Figure 3 are:

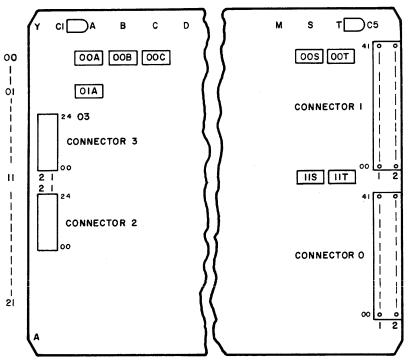

11S - This indicates the component location on the logic board. Figure 4 illustrates the method generally used to determine component location on a logic board. With the logic board oriented so that the header connectors (Connector 0 and Connector 1) are on the right, the components are lettered from left to right starting in the upper left corner. That is, the first IC in the upper left corner is A01 and the first capacitor is C1. Test points are lettered bottom to top from A-Y (omitting I, O, L, E).

19-061 - The number 19 is the category number of ICs, and the 061 is the sequence number of the component.

SB - Indicates this component is a Schottky Buffer. Some common designations used are:

SA - Schottky AND Gate

SB - Schottky Buffer

SG - Schottky Gate

SGO - Schottky Gate, Open Collector

HG - High Speed Gate

HPO - High Speed Power Gate, Open Collector

L1 - This input lead is from area L1 on the same schematic sheet.

10M1, 12A1, and 18K4 - Indicate outputs to another logic schematic sheet.

218-0, 117-0, and 114-0 - Indicate inputs from Connector 0.

Note that the pin numbers (01, 02, 04, 05, and 06) correspond directly to the actual IC pin numbers.

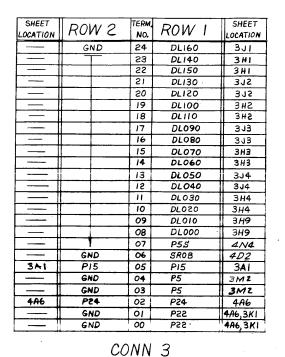

Figure 4 also shows the locations of the header connectors (Connector 0 and Connector 1) and the cable connectors (Connector 2 and Connector 3). All logic boards always contain Header Connectors 0 and 1, however, any combination (either, both, or none) of cable connectors (Connector 2 and Connector 3) may be provided.

Figure 4. Example of a Logic Board Layout

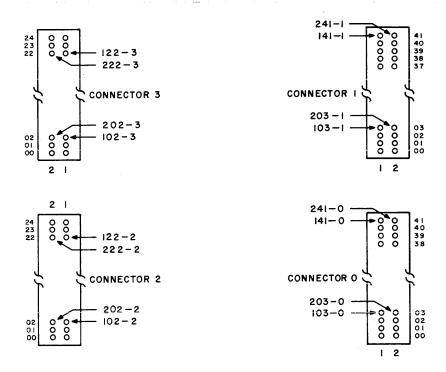

Figure 5 provides the pin numbering scheme for the header and cable connectors. Header connectors always have 2 rows of pins and 42 positions. Cable connectors always have 2 rows of pins but may vary in the number of positions.

Figure 5. Connector Pin Numbering

A net is defined as an electrical connection between two or more points in a circuit. Ordinarily, a net has an originating end (usually a collector where the signal is generated) and one or more terminating ends. Often it is convenient to assign descriptive mnemonic names to nets as a way of identifying them on schematics. Whether a net is named or not is sometimes arbitrary. However, a net is always assigned a name if:

- 1. The net is contained on one drawing sheet but is not shown as a complete solid line on that sheet.

- 2. Part of the net appears on more than one sheet.

- 3. Part of the net connects with a different schematic.

- 4. Part of the net leaves a logic board.

If a nef is named, the following rules are observed.

- 1. All mnemonic names are a maximum of six characters.

- 2. All decimal digits and upper case letters except the letters "I, O, Q, and Z" are permitted.

- 3. No other characters permitted.

- 4. Where possible, mnemonics are descriptive. However, it should be recognized that descriptive names are not always possible and a danger of misinterpreting a mnemonic exists.

- 5. Mnemonic names are not repeated within a schematic.

- 6. Every mnemonic is suffixed by a state indicator. This indicator consists of the digit "1" for the logically true state, or the digit "0" for the logically false state. For example, the set side of a flip-flop would have the "1" state indicator, while the reset side would have the "0" state indicator. The state indicator for a function changes each time that function is inverted. Thus, the state indicator permits assigning the same mnemonic to functions that are identical except for an inversion.

- 7. When a logical function is inverted, an inversion indicator is added after the state indicator. This allows for functionally equivalent, but electrically different nets to have the same mnemonic name. For example, assume a signal NAME1. NAME1 may be inverted to produce NAME0. If NAME0 is then inverted, NAME1A is produced. NAME1 and NAME1A are functionally equivalent, but physically different nets.

Sometimes a net fans-out to many sheets in a schematic. It is also possible for a net to fan-out to sheets in different schematics. In these situations, the net is assigned a mnemonic name. The net is also "zoned" from sheet to sheet to allow for properly identifying the originating and terminating ends of the net. The originating end of a net is defined as the collector at which a signal is generated. All other points to which the net connects are called terminating ends. When a lead leaves a sheet at the originating end, it is zoned to each and every sheet on which the net reappears, by indicating first the page number, followed by the schematic number that contains the page. For example, assume that the gate shown on Figure 3 is on a schematic, Sheet 20. The output, NAMEO, appears on Sheets 10, 12 and 18 of the schematic. Note that the schematic number is implied. When a net enters a sheet from another sheet, it is labeled with the same mnemonic name, and is zoned back to the originating end of the net only. Thus, on Figure 3, ENBL1 may, however, have many other terminations in addition to the one shown. Generally then, when a net leaves the sheet where it originates, it is zoned to every other sheet where the net terminates, while the terminating end is zoned only to the originating sheet. Note that in the Model 80 schematics, signals are co-ordinated between sheets only when the sheets are related to the same board. When a signal leaves a board, the back panel map must be used.

When a lead leaves a logic board, it usually does so through a logic board back panel connector pin. These connector pins must be shown on the schematic even if the complete net is shown on one drawing sheet. Only the connector pin number need be indicated under the pin symbol, since the connector number itself is implied by the logic board location number in the logic symbol or in the footnote. Thus, on Figure 3, RD061 enters the logic board on Pin 114 of Header Connector 0.

Figures 6 and 7 are typical schematic sheets with call-outs illustrating many of the conventions described in this section.

The schematic drawings for the basic digital system and some of the more common expansions are commonly included in the rear of the appropriate digital system maintenance manual. Schematic drawings for other expansions are included with the expansion or with the publications that describe the expansion.

# APPENDIX 1

# PART NUMBER CROSS REFERENCE TABLE

| INTERDATA Part Number | Туре                                                   | JEDIC Number       |

|-----------------------|--------------------------------------------------------|--------------------|

| 19-001                | Dual 4 Input Nand DTL                                  | 15861              |

| 19-002                | Triple 3 Input Nand DTL                                | 15863              |

| 19-003                | Quad 2 Input Nand DTL                                  | 15849N             |

| 19-004                | Hex 1 Input Nand DTL                                   | 15837N             |

| 19-005                | Dual Power Gate DOC                                    | 863 <b>3</b> N     |

| 19-006                | Dual Buffer DTL                                        | 1582N              |

| 19-007                | Flip-Flop DTL                                          | 15848N             |

| 19-008                | Gate Expander Dual 4 Input DTL                         | 15833N             |

| 19-009                | 8 Bit Stack DTL                                        | 903059 (Fairchild) |

| 19-010                | Differential Compartor LIN                             | 72710L             |

| 19-012                | Dual 4 Input Buffer TTL                                | 74H40H             |

| 19-013                | Quad 2 Input Nand DTL                                  | 15846              |

| 19-014                | Dual J-K Flip-Flop DTL                                 | 158097N            |

| 19-015                | Hex Inverter 1 Input                                   | 74H04H             |

| 19-016                | Quad 2 Input TTL                                       | 74H00N             |

| 19-017                | Triple 3 Input TTL                                     | 74H10N             |

| 19-018                | Dual 4 Input TTL                                       | 74H20N             |

| 19-019                | Single 8 Input TTL                                     | MC3015 (Motorola)  |

| 19-020                | Operational Amplifier LIN                              | MC1709C (Motorola) |

| 19-021                | Quad 2 Input Power DOC                                 | 15858N             |

| 19-022                | Dual J-K Flip-Flop TTL                                 | MC3061P (Motorola) |

| 19-023                | Selected Dual Buffer 19-006 with 20-30 nsec. delay DTL | 158 <b>32</b> N    |

| 19-024                | Triple 3 Input AND TTL                                 | 74H11N             |

| 19-025                | Dual 4 Input AND TTL                                   | 74H21N             |

| 19-026                | 2-2-2-3 Input AND-OR TTL                               | 7475N              |

| INTERDATA Part Number | Туре                                  | JEDIC Number           |

|-----------------------|---------------------------------------|------------------------|

| 19-027                | 4 Bit Latch TTL                       | 7475N                  |

| 19-028                | 4 Bit Adder TTL                       | 7483N                  |

| 19-029                | Quad Exclusive - OR TTL               | 7486N                  |

| 19-030                | 4 Bit Shift Register TTL              | 7495N                  |

| 19-031                | One Shot TTL                          | 7412N                  |

| 19-032                | 1 out of 10 Decoder TOC               | 74145N<br>5445<br>7445 |

| 19-033                | Sense Amplifier LIN                   | 7524N                  |

| 19-034                | Retriggerable One Shot TTL            | 74122N                 |

| 19-035                | 4 Bit Counter TTL                     | 74193N                 |

| 19-036                | Quad 2 Input Open Collector TTL       | 7438N                  |

| 19-037                | High Performance Operational Amp      | 7748393 (Fairchild)    |

| 19-038                | Dual 4 line to 1 line Mux TTL         | 74153                  |

| 19-039                | 4 Bit ALU TTL                         | 74181                  |

| 19-040                | Look Ahead Carry TTL                  | 74182                  |

| 19-041                | 4 x 4 Register Stack TTL              | 74170                  |

| 19-042                | Dual Retriggerable One Shot TTL       | 74123N                 |

| 19-043                | Quad 2 Input Open Collector TTL       | 74H01N                 |

| 19-044                | Hex Inverter Open Collector TTL       | 74H05N                 |

| 19-045                | Dual J-K Flip-Flop TTL                | 74H106                 |

| 19-046                | Quad RS-232C Line Driver              | MC1488L (Motorola)     |

| 19-047                | Quad RS-232C Line Receiver            | MC1489AL (Motorola)    |

| 19-048                | 8 Bit Shifter                         | 74198N                 |

| 19-050                | 8 Input Nand TTL                      | 74H30                  |

| 19-051                | 1024 Bit PROM TTL                     | 74187 (Fairchild)      |

| 19-055                | Quad 2 Input Nand STTL                | 74S00                  |

| 19-056                | Quad 2 Input Nand Open Collector STTL | 74S03                  |

| 19-057                | Hex 1 Input Inverter STTL             | 74804                  |

| 19-058                | Triple 3 Input Nand STTL              | 74810                  |

| 19-059                | Triple 3 Input AND STTL               | 7 <b>4</b> S11         |

| 19-060                | Dual 4 Input Nand STTL                | 74S20                  |

| INTERDATA Part Number | _Type_                                             | JEDIC Number                            |

|-----------------------|----------------------------------------------------|-----------------------------------------|

| 19-061                | Dual 4 Input Buffer STTL                           | 74S40                                   |

| 19-062                | 2-2-3-4 Input AND-OR Inverter STTL                 | 74S64                                   |

| 19-063                | Dual D Edge Triggered Flip-Flop STTL               | 74874                                   |

| 19-064                | Dual J-K Flip-Flop STTL                            | 74S112                                  |

| 19-065                | Quad 2:1 Max Non-inverting STTL                    | 74S157                                  |

| 19-066                | Quad 2:1 Mux Inverting STTL                        | <b>74S15</b> 8                          |

| 19-067                | 4 Bit ALU STTL                                     | 74S181                                  |

| 19-068                | Carry Look Ahead STTL                              | 74S182                                  |

| 19-069                | 8 line to 1 line Mux STTL                          | 74151                                   |

| 19-070                | 4 Bit Syncronous Counter TTL                       | 74161                                   |

| 19-071                | Quad D Edge Triggered Flip-Flop                    | 74175                                   |

| 19-072                | 4 Bit Left/Right Shift Register TTL                | 74194                                   |

| 19-073                | Dual 4:1 Mux Tri-State TTL                         | 8214 (National)                         |

| 19-074                | 8 Bit Priority Encoder TTL                         | 9318 (Fairchild)                        |

| 19-075                | 16 x 4 Register Stack TTL                          | 3101A (Intel)                           |

| 19-076                | 1024 Bit Memory MOS                                | TM54062                                 |

| 19-077                | 256 Bit Memory TTL                                 | 6531 (Monolithic Memories)              |

| 19-078                | Dual 4 Input Nand-OC                               | 74822                                   |

| 19-080                | High-Speed PROM                                    | 82S29 (Signetics)                       |

| 19-081                | Univ. Asynchronous Receiver/Transmitters           | TR1042A (Western Digital)               |

| 19-082                | 2-2-3-4 Input AND-OR Invert Open<br>Collector STTL | 74S65                                   |

| 19-083                | 9 Bit Parity Generator/Checker STTL                | 82S62 (Signetics)                       |

| 19-085                | Monolithic Timing Circuit                          | MC1555 (Motorola)<br>NE555V (Signetics) |

| 19-086                | 741 C DIP Operational Amplifier                    | U6A7741393 (Fairchild)                  |

| 19-087                | 747 DIP Operational Amplifier                      | U7A774 (Fairchild)                      |

| 19-088                | 737 C DIP Operational Amplifier                    | U6A773393 (Fairchild)                   |

| 19-089                | Dual D Edge Triggered Flip-Flop                    | 74H74                                   |

| 19-090                | High Speed (710) Differential Comparator DIP       | U6A771093 (Fiarchild)                   |

| 19-091                | Retriggerable Single One Shot                      | 9600 (Fairchild)                        |

| INTERDATA Part Number | Type                                              | JEDIC Number                                  |

|-----------------------|---------------------------------------------------|-----------------------------------------------|

| 19-092                | Negative Voltages Regulator                       | MC1463R (Motorola)                            |

| 19-093                | Positive Voltages Regulator                       | MC1469R (Motorola)                            |

| 19-094                | Voltage Regulator                                 | U6A7723393 (Fairchild)<br>MC1723CL (Motorola) |

| 19-095                | Linear Positive Voltage Regulator                 | U9H7805393 (Fairchild)                        |

| 19-096                | First In-First Out Serial Memory<br>64 Word 4 Bit | 3341 (Fairchild)                              |

| 19-097                | Amplifier                                         | LH0002H (National)                            |

| 19-098                | Quad 2:1 Multiplexor Non-Inverting                | 74157                                         |

| 19-099                | Dual Sense Amplifier                              | 75234N                                        |

| 19-100                | Driver                                            | 75452N                                        |

| 19-101                | 4-2 Input Buffer                                  | 7437N                                         |

| 19-102                | 6-1 Input Buffer OC                               | 7407N                                         |

| 19-103                | 1 out of 10 Decoder                               | 7442N                                         |

| 19-104                | Current Switch                                    | 75325N                                        |

| 20-001                | Transistor NPN High Speed Switch                  | 2N3646                                        |

| 20-002                | Transistor PNP 500 MA                             | MPS6534 (Motorola)                            |

| 20-003                | Transistor                                        | 2N3902                                        |

| 20-004                | Transistor NPN                                    | 2N5189                                        |

| 20-006                | Transistor NPN 15 Amps 100W T03 case              | 2N3055 (RCA)                                  |

| 20-007                | Transistor NPN 3 Amps                             | TIP31A                                        |

| 20-008                | Transistor PNP 3 Amps                             | TIP32A                                        |

| 20-009                | Transistor Triac 2 Amps 100V                      | A03001 (Electronic Control Corp).             |

| 20-010                | Transistor NPN 500 MA Code Driver                 | 2N5845                                        |

| 20-011                | Transistor Photo                                  | 2N5777                                        |

| 20-012                | Transistor PNP High Current Switch                | 2N2907                                        |

| 20-013                | Transistor NPN                                    | 2N3303                                        |

| 20-014                | Transistor NPN                                    | 2N4238                                        |

| 20-015                | Transistor PNP                                    | 2N4235                                        |

| 20-016                | Transistor PNP                                    | 2N3740                                        |

| 20-017                | Transistor NPN                                    | 2N3766                                        |

| INTERDATA Part Number | Type                               | JEDIC Number                 |

|-----------------------|------------------------------------|------------------------------|

| 20-018                | Transistor, Power Silicon NPN      | 2N3054                       |

| 20-019                | Transistor NPN Fast PWR Switch     | 2N6308 (Motorola)            |

| 20-020                | Transistor Switching 1 Amp T05 can | 2N3725                       |

| 20-021                | Transistor NPN Silicon             | MPS3646 (Motorola)           |

| 20-022                | Transistor NPN                     | 1N1711                       |

| 20-023                | Transistor PNP                     | 2N2905A                      |

| 20-024                | Transistor Switch                  | 2N3776                       |

| 21-025F01             | 1K ohm-15 to Common DIP            | 898-1-1K ohm (Beckman)       |

| 21-025F02             | 470 ohm-15 to Common DIP           | 898-1-470 ohm (Beckman)      |

| 21-025F03             | 330 ohm-15 to Common DIP           | 898-1-330 ohm (Beckman)      |

| 23-001                | Diode High Speed-High Current      | 1N914                        |

| 23-002                | Diode 5.1 V Zener                  | 1M5. 1ZS5 (Motorola)         |

| 23-003                | Diode 10V Zener                    | 1M10ZS5 (Motorola)           |

| 23-004                | Diode 6.2 V Zener                  | 1M6. 2ZS5 (Motorola)         |

| 23-007                | Diode Mot Bridge                   | MDA962-2 (Motorola)          |

| 23-008                | Diode Int. Rectifier               | 40HF-5R                      |

| 23-009                | Diode                              | 1N4735                       |

| 23-010                | Diode Int. Rectifier               | S1Y1P                        |

| 23-011                | Diode Rectifier                    | 2N681                        |

| 23-012                | Diode Thermister                   | KA31J1 (Fenwall)             |

| 23-013                | Diode 9.4V                         | 1N2163                       |

| 23-014                | Diode                              | 1N3880                       |

| 23-015                | Diode                              | 1N3889                       |

| 23-016                | Diode Bridge Recitifer             | VS448 (Varo)                 |

| 23-017                | Diode                              | 1N2070                       |

| 23-018                | Diode 18 V Zener                   | 1N4746A                      |

| 23-019                | Diode                              | 1N3615                       |

| 23-020                | Diode 8.2V Zener                   | 1N756A                       |

| 23-021                | Diode 9.1 V Zener                  | 1N757A                       |

| 23-022                | Diode 3.3V Zener                   | 1N746A                       |

| 23-023                | Diode Bridge Rectifier             | KBH2506 (General Instrument) |

| INTERDATA Part Number | Type                            | JEDIC Number                     |

|-----------------------|---------------------------------|----------------------------------|

| 23-024                | Diode, Power Fast Rec. 30 Amps. | 1N3909                           |

| 23-025                | Diode, Power Fast Rec. 3 Amps.  | A115A (General Electric)         |

| 23-026                | Triac 600V 30 Amps              | 2N6162                           |

| 23-027                | Diac 32V                        | 1N5761                           |

| 23-028                | Power SCR Thyristor             | 2N4441                           |

| 23-029                | Diode                           | 1N4607                           |

| 23-030                | Diode                           | 1N4156                           |

| 23-031                | Diode 6.6 V Zener               | 1N4736                           |

| 23-032                | Diode 8.8 V Zener               | 1N4739                           |

| 23-033                | 16 Diode Array                  | 45190 (Litton)                   |

| 30-018                | 100 nsec. Delay Line 10 taps    | 30-018 (Princeton Advanced Eng.) |

| 30-019                | 50 nsec. Delay Line 10 taps     | 30-018 (Princeton Advanced Eng.) |

# **PROCESSOR**

# M80-000 AND M80-001 MODEL 80 INSTALLATION SPECIFICATION

### 1. INTRODUCTION

This specification provides installation information for INTERDATA Model 80 Digital Systems.

The INTERDATA Model 80 Digital System features a highly modular structure which permits configuration to suit the user's exact needs. It provides the means for convenient expansion as the user's requirements grow. This document describes the Processor and expansion chassis, power supply mounting, filler and display panel mounting, and the interconnecting cables. Integrated circuit boards are discussed with respect to cabling and location only. Circuit descriptions of these boards are provided in the appropriate maintenance or instruction manuals. Note that the following discussion assumes that the equipment is mounted in standard INTERDATA cabinets.

### 2. UNPACKING

To avoid damage to the Model 80 or its peripherals, read the following procedures before starting an installation.

- 1. Carefully remove each component from its carton or crate, observing any special unpacking instructions included with the component.

- 2. Inspect all components for physical damage.

- 3. If the system is shipped from INTERDATA already rack mounted, simply check to insure that all terminals and connectors are secured properly.

- 4. The Model 80 should be located with sufficient free space (sides and back) to insure unobstructed air flow. A minimum clearance of two inches on each side and six inches at the back is required.

## 3. MECHANICAL CONFIGURATION

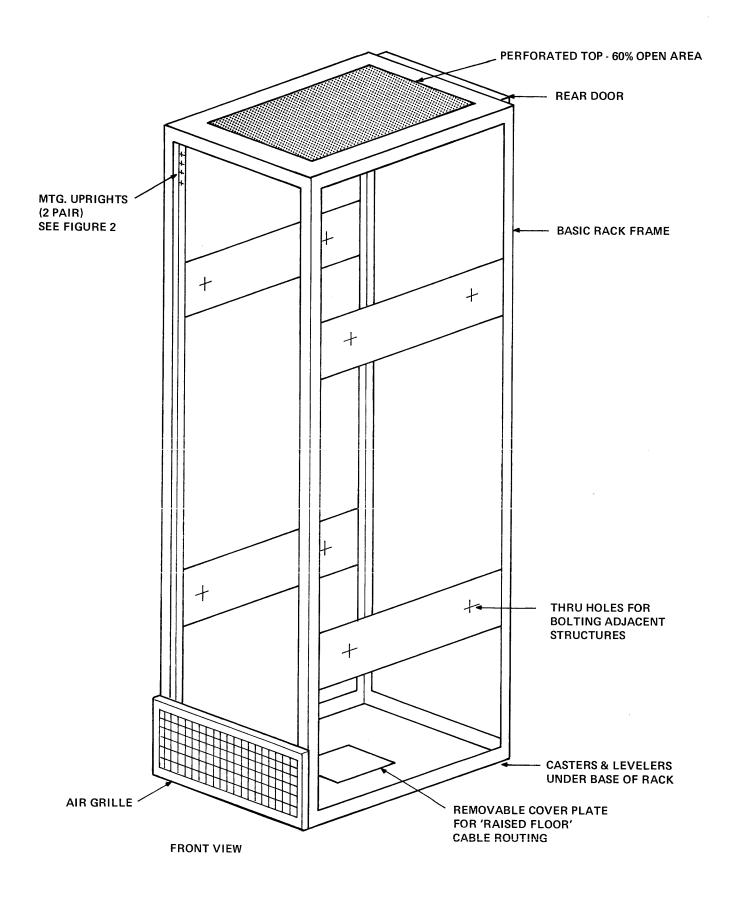

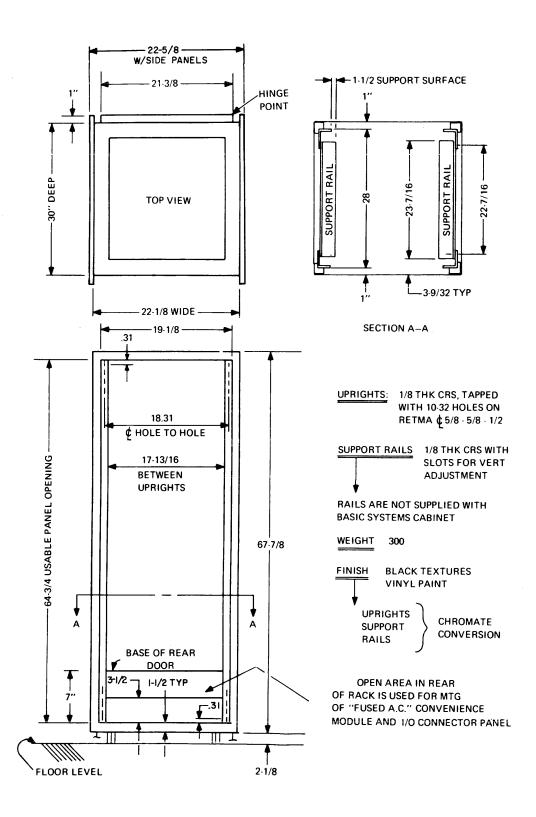

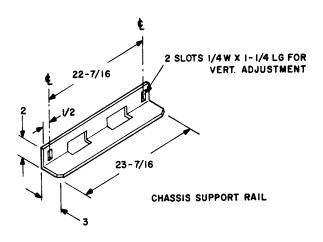

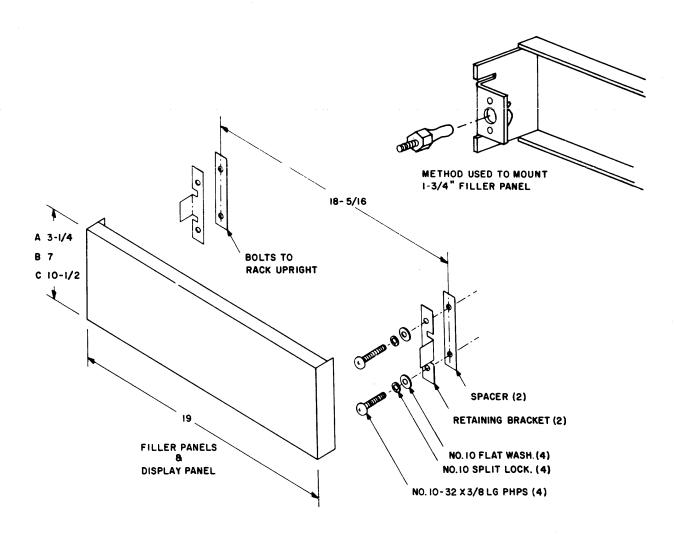

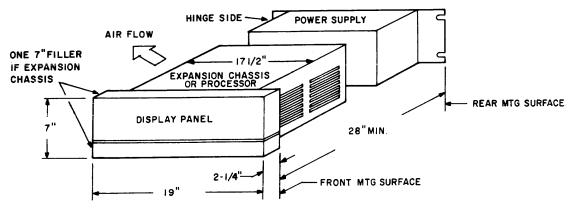

Figures 1 through 4 are intended to familiarize the reader with the mechanical components of a typical INTERDATA Digital System. Dimensions and mounting information are provided for the Basic Cabinet, Chassis Support Rails, Display Panels, and Filler Panels. Note in Figure 4 that while the  $5\frac{1}{4}$  inch, 7 inch, and  $10\frac{1}{2}$  inch Filler Panels and the Display Panel Mount the same way (via retaining brackets), the smaller 13/4 inch Filler Panel mounts with spring clips.

## 4. POWER SUPPLY INSTALLATION

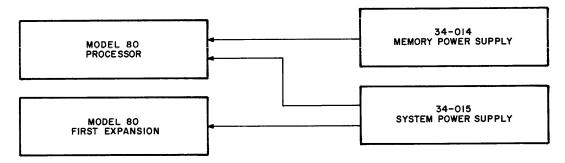

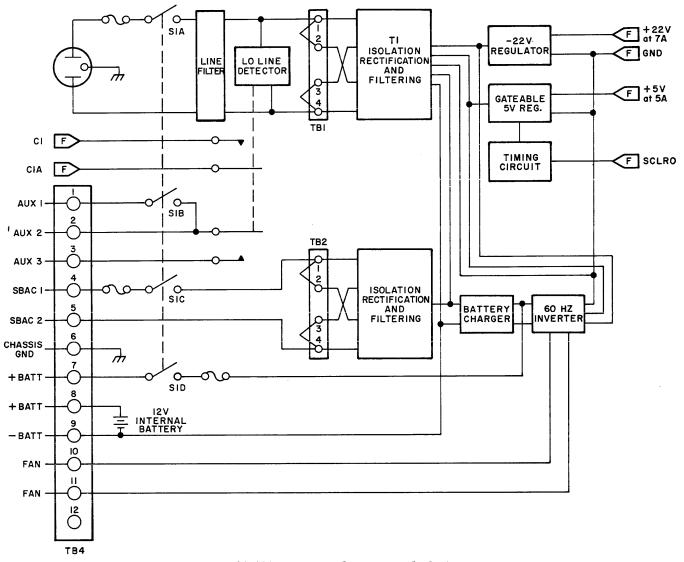

This section describes the installation of the Model 80 Power Supplies. Mounting information and cabling instructions are provided for both the 34-015 Logic Power Supply and the 34-014 Memory Power Supply.

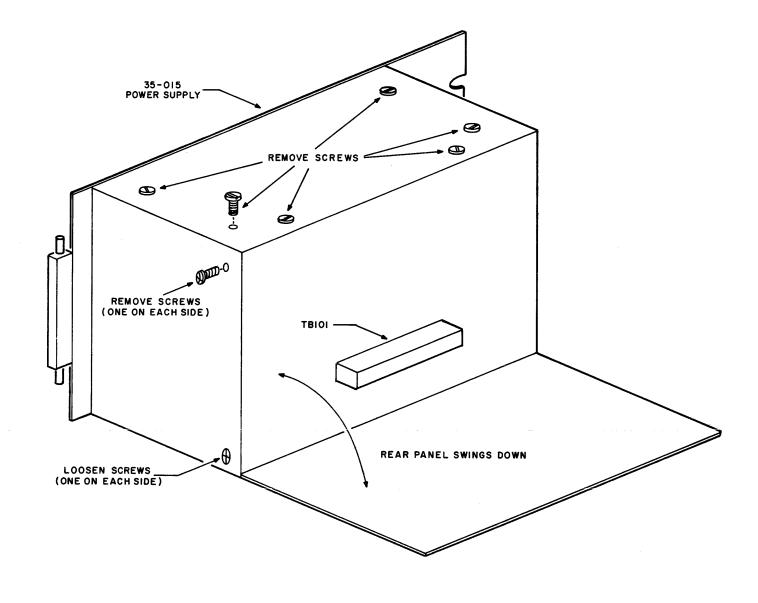

#### 4.1 Mounting

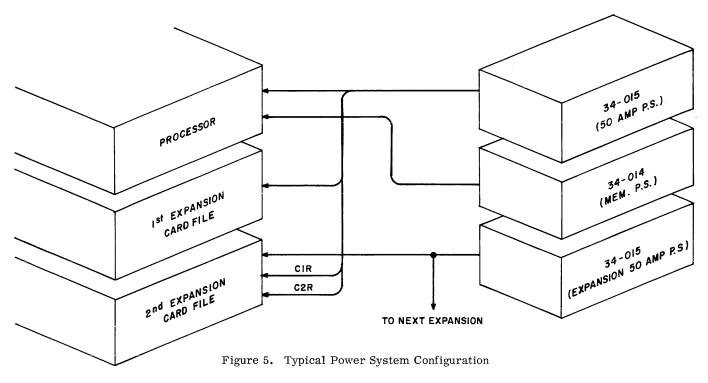

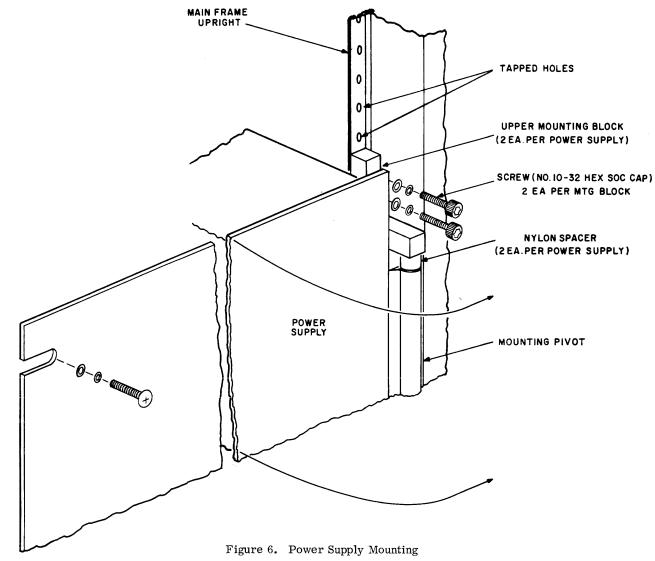

The Power Supplies mount directly behind the Processor and Expansion Chassis. (See Figure 5.) They are attached to the right mounting upright (looking from the rear) via two mounting blocks and two nylon spacers. (See Figure 6.)

### WARNING

Before hinging out the power supplies, the rack levelling feet should be lowered. Up to three power supplies can be hinged out at one time after the levellers are in contact with the floor surface.

The Power Supplies may be swung in or out on their mounting pivots for easy access to the back plane. When they are in the operating position, they are secured by two 10-32 screws which attach to the left mounting upright (viewed from the rear).

Figure 1. Basic Cabinet

Figure 2. Basic Cabinet Physical Dimensions

Figure 3. Chassis Support Rail

Figure 4. Typical Mounting Configuration for Display and Filler Panels

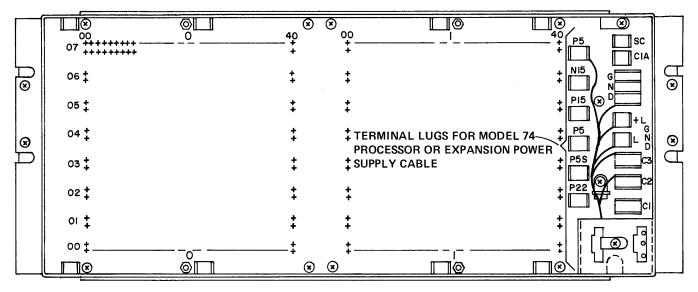

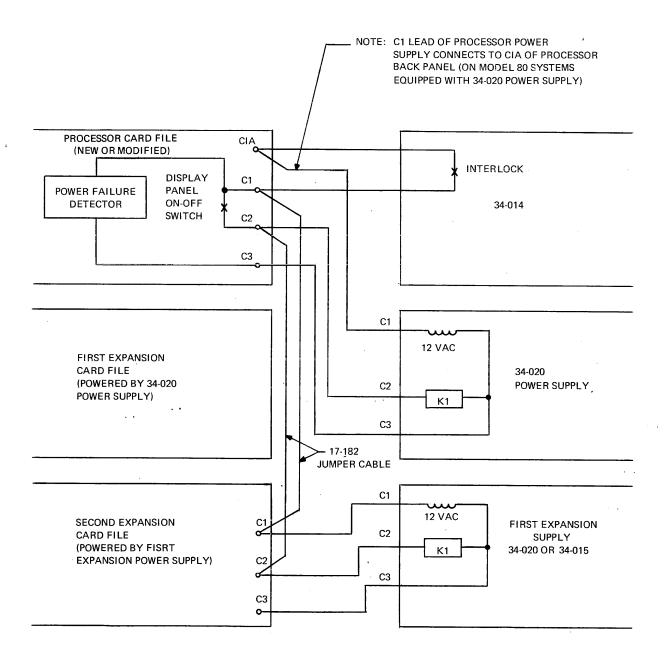

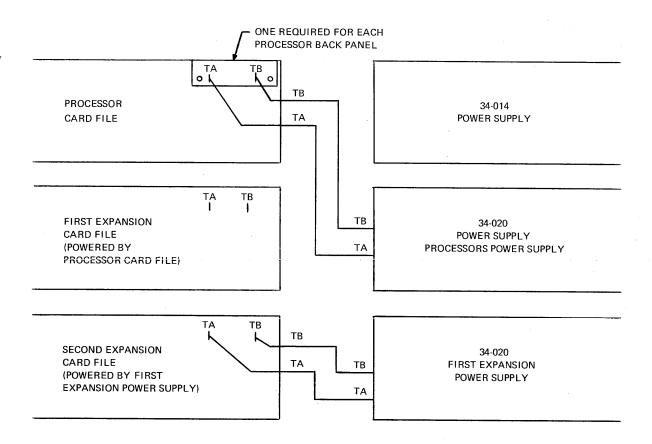

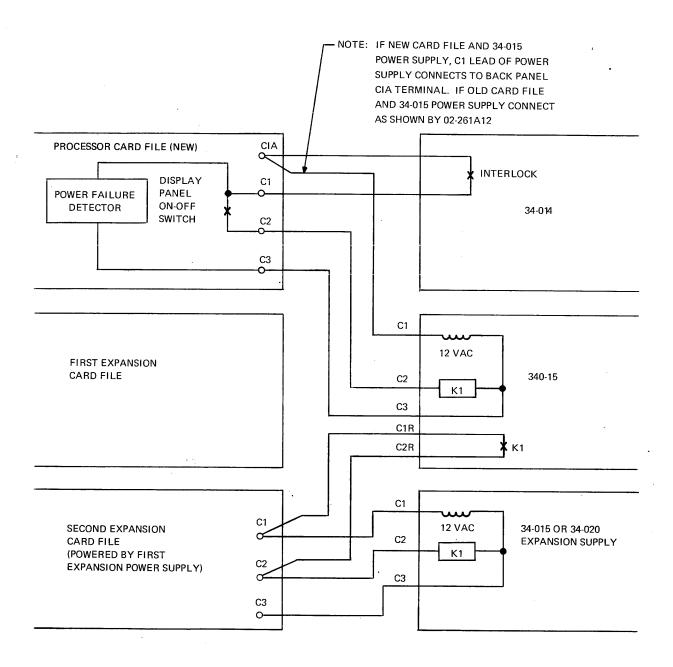

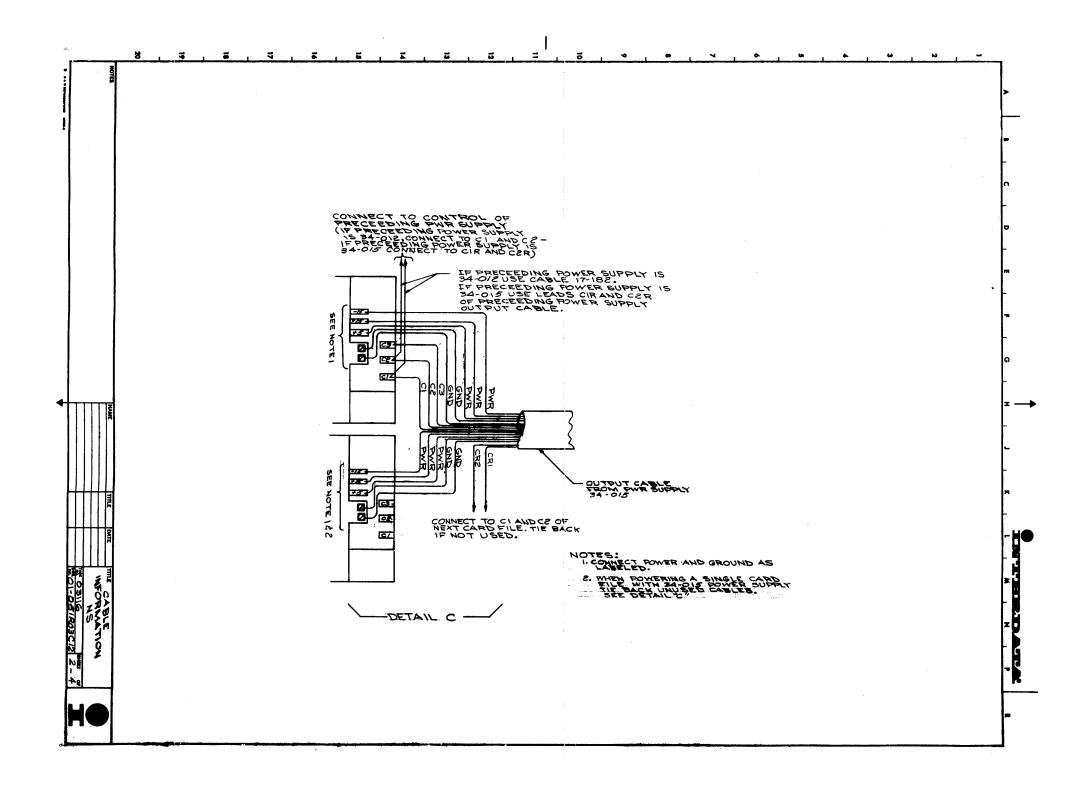

## 4.2 Power Supply/Chassis Cabling

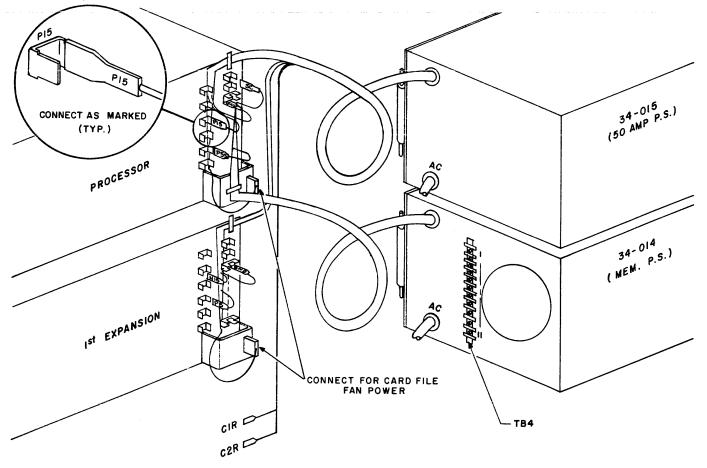

A typical Model 80 Power Supply/Chassis configuration is shown in Figure 7. (The power supplies may be reversed if required.) A cable from each power supply terminates at the Processor and Expansion Chassis back panel as indicated. Refer to the Model 80 Power System Description, 02-261A12, which is contained in the Model 80 Maintenance Manual, Publication Number 29-280 for details. The installation sequence for the Power System is:

- 1. Mount the power supply chassis. Refer to Figures 5 and 6.

- 2. Connect the cables to the Processor and Expansion Chassis as shown in Figure 7. Fan power must be connected as shown before system is powered. If no first Expansion Chassis, secure unused connectors to prevent shorting.

#### 5. PROCESSOR AND EXPANSION CHASSIS MOUNTING

Two Expansion Chassis (10 inch and 15 inch) are available for expanding the INTERDATA Digital System. The 15 inch Expansion Chassis has the same overall dimensions as the Processor Chassis. See Sections 3 and 8 on Configuration. The Expansion or Processor Chassis slides into the rack on the two Chassis Support Rails (see Figures 2 and 3) on the front of the rack.

#### CAUTION

No chassis should be mounted in cantilever fashion. Chassis support rails MUST be used. If a rack cabinet other than an INTER-DATA cabinet is used, consult the rack manufacturer for proper support rails.

The chassis support rails are fastened to the mounting uprights of the front and rear of the rack. Slots are provided in the rails to allow vertical adjustment. The Expansion or Processor Chassis are screwed in place at the mounting uprights in front of the rack. All Expansion Chassis mount below the Processor Chassis. Expansion Chassis cabling is discussed later in this document. Figure 8 shows Expansion Chassis location with respect to the filler panel and power supply.

Figure 7. Power System Cabling

Figure 8. Processor or Expansion Chassis Location

#### 5.1 Processor Installation

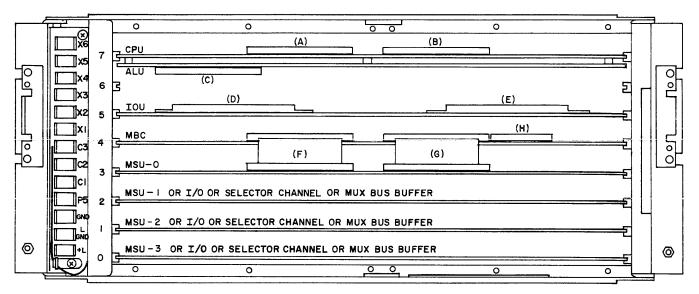

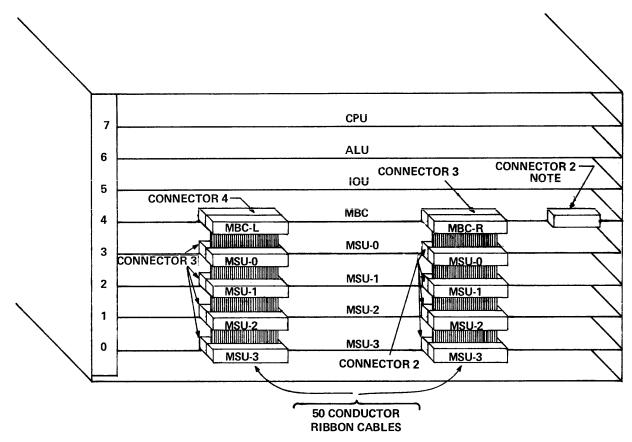

The basic Model 80 with 16KB of memory (see Figure 9) is comprised of:

| 1. | CPU | 35-403   | slot #7 |

|----|-----|----------|---------|

| 2. | ALU | 35-404   | slot #6 |

| 3. | IOU | 35 - 405 | slot #5 |

| 4. | MBC | 35-407   | slot #4 |

| 5. | MSU | 35-406   | slot #3 |

The remaining three slots are used to expand memory to the maximum of three additional MSUs or 64 KB of memory. The remaining slots in the basic chassis, after the memory has been expanded, may be used to expand the I/O. Full or halfboard I/O may be plugged into these slots. If a Selector Channel or Multiplexor Bus Buffer (MBFR) is plugged into the basic chassis, all I/O slots on Connector 1 are dedicated to the private Selector Channel or Buffered Bus. Only one of these two devices may be contained in the basic chassis as the private I/O Bus in Connector 1 connects Slots 0, 1, and 2 together.

Figure 9 is a configuration of the Processor Chassis. It is viewed from the Display Panel side, and correlates applicable cables to the associated Processor connectors.

## 5.2 15 Inch Expansion Chassis

The 15 inch Expansion Chassis contains eight universal expansion slots which can accept combinations of single board peripheral controllers, system modules, selector channels, or user designed interfaces. Included with this chassis are the cooling fans and interconnecting cables. The chassis may be ordered with or without a power supply.

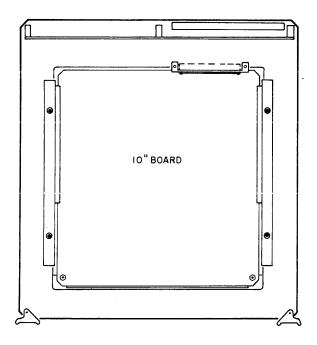

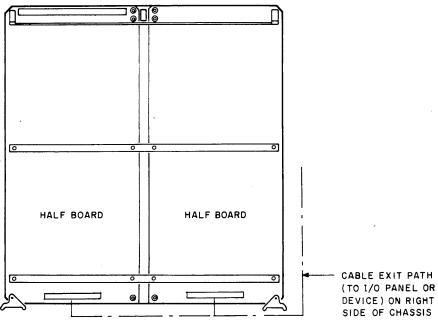

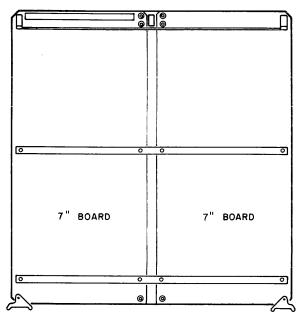

5.2.1 7 and 10 Inch Boards in a 15 Inch Chassis. A 10 inch I/O Controller (provided it does not use Connector 1) may be inserted into a 15 inch chassis via the 02-234 I/O Adapter Kit. (See Figure 10.) One or two 7 inch boards (halfboards) may be inserted into a 15 inch chassis via the 16-398 Half Board Adapter Kit (see Figure 11.) The Half Board Adapter Kit may hold two active 7 inch boards or one active and one blank 7 inch board, depending on requirements. No wiring takes place between the boards and the adapters. The adapters are designed such that the connectors on the boards plug directly into the Expansion Chassis.

### 5.3 10 Inch Expansion Chassis

The 10 inch Expansion Chassis contains six 10 inch I/O expansion slots which can accept any combination of up to six 10 inch wire-wrap or copper peripheral controllers, systems, modules, or user designed interfaces. Included with the chassis are the cooling fans and system interconnecting cables. The Power Supply is separate.

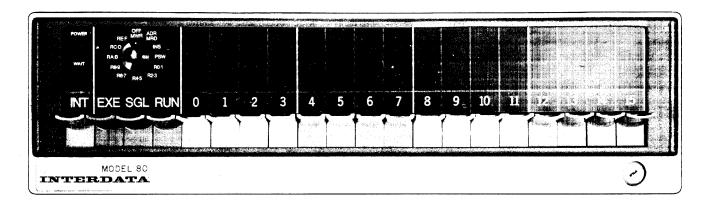

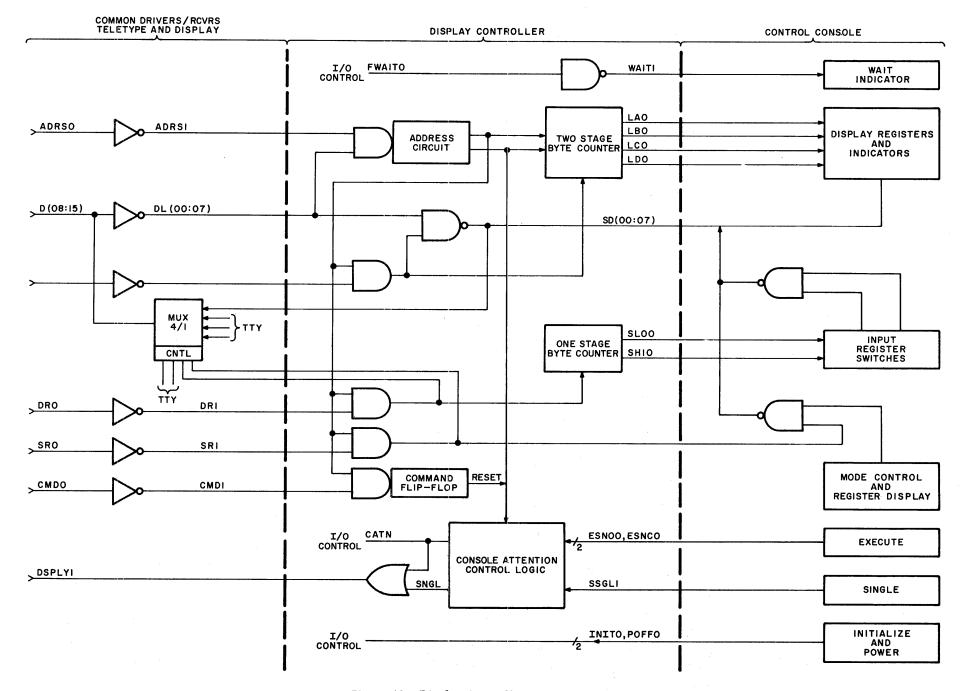

### 6. DISPLAY PANEL INSTALLATION

The Model 80 Display Panel is electrically tied to the Processor via a connector and Faston lugs. The connector is installed on Connector 3 of the IOU board (35-405) and the terminal lugs mate into a terminal strip on the left side of the Processor Chassis. The terminal lugs are identified at the Faston connector and are mated to their corresponding terminal pin (C1, C2, etc.) on the chassis. See Figure 9. The Display Console is physically mounted to the brackets provided on the Processor Chassis. The 1 3 4 inch Filler Panel is mounted directly below the Display Console on the same chassis. Refer to Figure 8.

Rear View

Front View

| MODEL 80 PROCESSOR CHASSIS CONFIGURATION |                 |                            |              |

|------------------------------------------|-----------------|----------------------------|--------------|

| CONNECTOR                                | CABLE           | FUNCTION                   | TYPE         |

| (A) CPU-3                                | DCS OR TEST SET | ROM ADDRESS                | RIBBON       |

| (B) CPU-2                                | DCS OR TEST SET | ROM DATA                   | RIBBON       |

| (C) ALU-2                                | TEST SET        | TEST                       | RIBBON       |

| (D) IOU-3                                | 17-152 ASSEMBLY |                            |              |

|                                          | (P/O 09-051)    | DISPLAY                    | BUNDLED WIRE |

| (E) IOU-2                                | 17-180          | TTY                        | BUNDLED WIRE |

| (F) MBC-4 to MSU-3                       | 17-191F01       | (16KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-191F02       | (32KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-191F03       | (48KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-191F04       | (64KB) MEMORY INTERCONNECT | RIBBON       |

| (G) MBC-3 to MSU-2                       | 17-212F01       | (16KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-212F02       | (32KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-212F03       | (48KB) MEMORY INTERCONNECT | RIBBON       |

|                                          | 17-212F04       | (64KB) MEMORY INTERCONNECT | RIBBON       |

| (H) MBC-2                                | 17-192          | MEMORY PROTECT             | RIBBON       |

Figure 9. Model 80 Processor Chassis Configuration (Front of Chassis)

Figure 10. 02-234 I/O Adapter (Top View)

NOTE: 35-398 HALF BOARD CAN BE LOCATED ON EITHER SIDE.

Figure 11. 16-398 Half Board Adapter

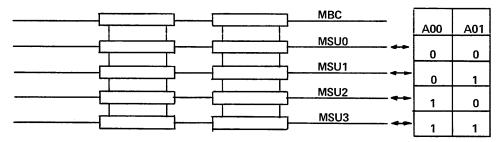

# 7. MEMORY INSTALLATION AND EXPANSION

The Memory Bus Controller (MBC) must be installed in Slot 4 of the Processor card file. All Memory Storage Units (MSUs) are installed in adjacent slots in this chassis. See Figure 9. Processor Card File Slots 0, 1, and 2 may also be used for I/O controllers, an MBFR, or a Selector Channel. Note, however, that using these slots reduces the maximum permitted memory size.

### 8. CONFIGURATION

#### 8.1 System Expansion Chassis

When configuring a multi-chassis system, there are four rules that must be followed:

- 1. The System Expansion Chassis must be mounted below the basic Processor chassis.

- 2. All chassis must be contiguous.

- 3. All 15 inch System Expansion Chassis must be mounted above any 10 inch System Expansion Chassis.

- 4. Multiboard peripheral device controllers (on 10 inch circuit boards) can only be used in the 10 inch system expansion chassis.

#### 8.2 Circuit Board Distribution

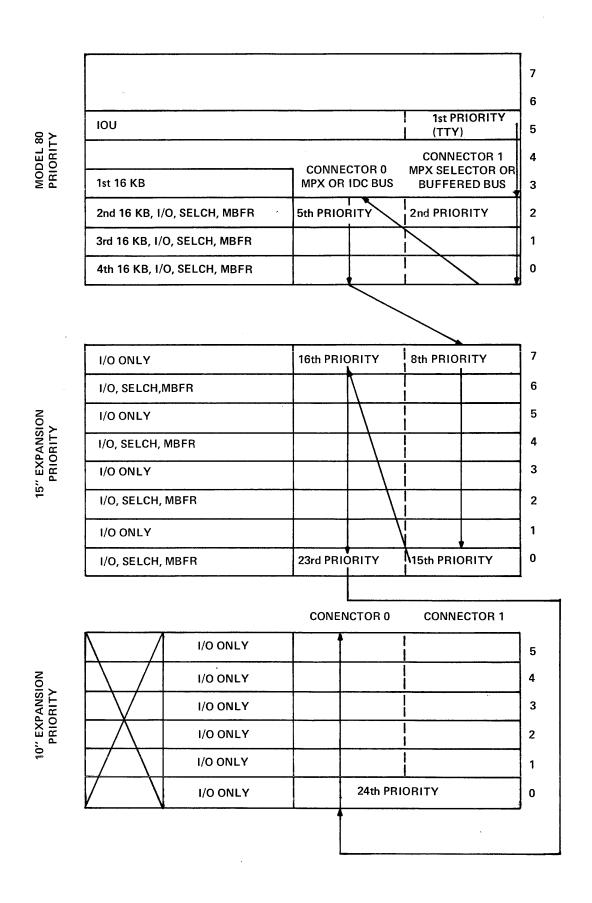

Model 80 Digital Systems may be configured in a variety of ways. However, the following factors must be considered when determining circuit board distribution within the basic Processor and the System Expansion Chassis. See Figure 12.

- 1. The Selector Channel can be placed in Slot 0, 1, or 2 of the Processor Chassis, or Slots 6, 4, 2, or 0 of the System Expansion Chassis. Only one Selector Channel may be contained in the basic Processor.

- 2. In the System Expansion Chassis, all contiguous slots on Connector 1 below the position where the SELCH is inserted become SELCH Bus slots. (This only applies within the chassis containing the SELCH.) The SELCH Bus extends down the left side connectors (front view). Note that all device controllers on 10 inch adapter boards connect to the Multiplexor Bus from the right side connectors (front view). Therefore, these device controllers may be inserted in vacant SELCH Bus slots, but will not be on the SELCH bus. This also applies to all 7 inch boards on adapters, installed on the right side. In the Processor Chassis, Connector 1 of Slots 0, 1, and 2 becomes the SELCH Bus when the SELCH is in any of the 3 slots.

- 3. The SELCH Bus can be extended by cable to any even numbered slot in an I/O chassis adjacent to the chassis containing the SELCH controller.

- 4. All device addresses are hard-wired on the device controller cards, (device addresses may be changed at option) so that the distribution of I/O device controllers in the chassis normally need only be considered as a matter of priority in the RACKO/TACKO "daisy-chain" and convenience.

- 5. The 15 inch System Expansion Chassis, and the basic Processor chassis may only be used for single board I/O device controllers unless the interconnection between boards takes place via cables installed on the outer edge of the board. No back panel stitch pattern is provided. For multi-board 10 inch device controllers, the 10 inch System Expansion Chassis must be used.

- 6. Priority is established by the physical placement within a chassis. Priority for interrupt driven devices should normally be established in order of descending speed, i.e., drum higher than magnetic tape, and card reader higher than a paper tape reader, etc.

- 7. The Multiplexor Bus Buffer (MBFR) may be installed in the Processor Chassis or Systems Expansion Chassis in any slot that can be used by the SELCH. This creates a Buffered Bus on Connector 1 where the SELCH created a SELCH Bus. (See items 1, 2, and 3 above.) Only one MBFR may be contained in the Processor Chassis. When an MBFR is housed in the Processor Chassis, the Processor SCLRO line must be removed from Connector 1 as this signal is regenerated on the MBFR card. In the System Expansion Chassis, the bus on Connector 1 may be cut into up to five separate sections to accommodate several SELCH and/or MBFR combinations. Each section can be cabled to another chassis and the 2 slot sections can also handle a SELCH or Buffered MUX controller.

## NOTE

Connector 1 on Slots 0, 1, and 2 of the Processor Chassis is a common copper bus that cannot be cut. Only a single SELCH or MBFR can be installed in the Processor Chassis.

Figure 12. System Chassis Configuration and I/O Priority

#### 8.3 Back Panel Wiring

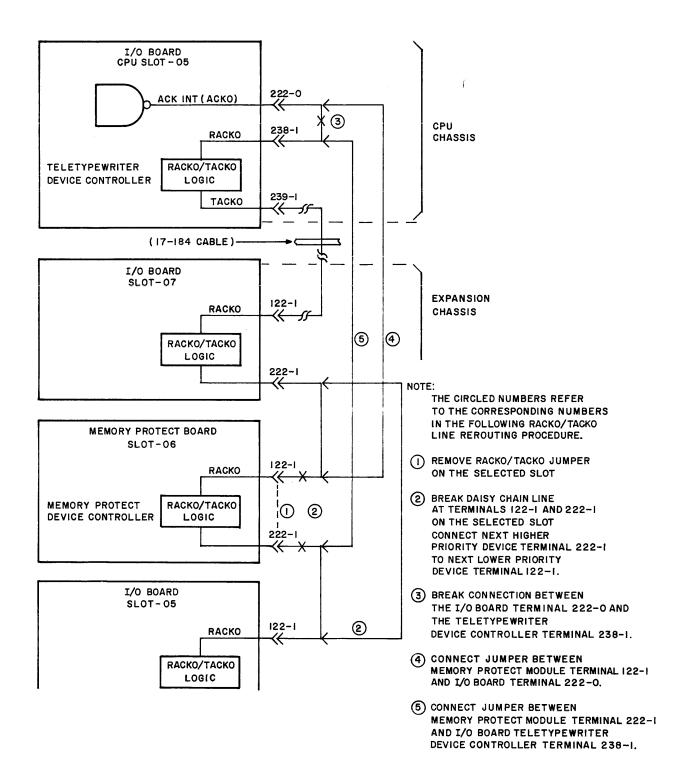

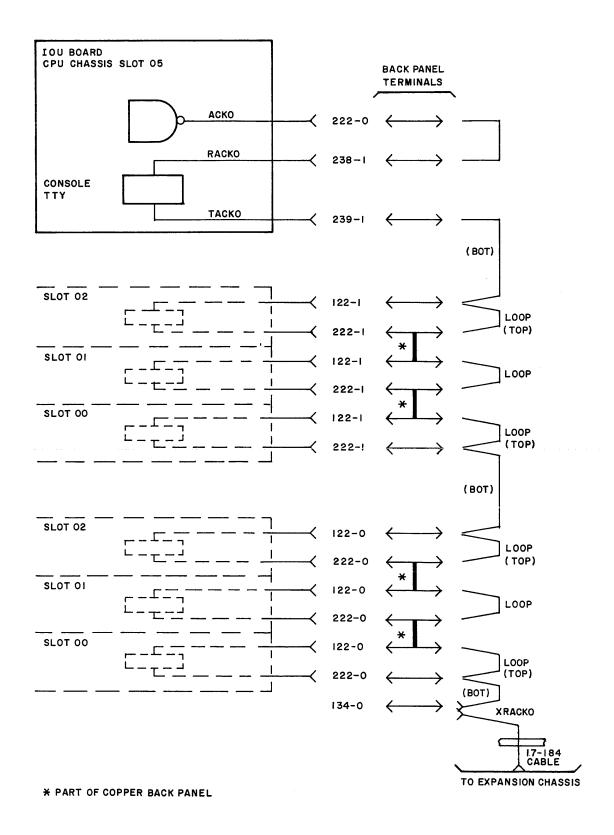

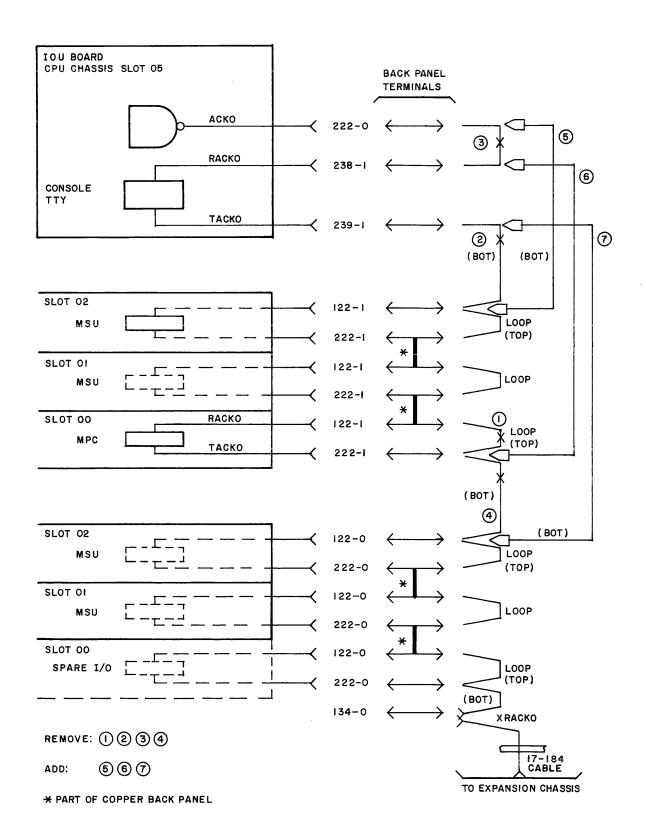

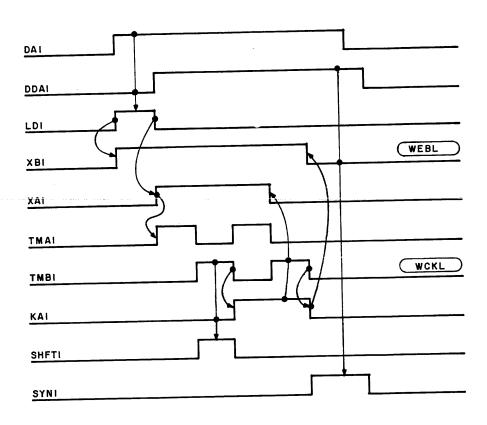

The Acknowledge Control Line from the Processor carries the Interrupt acknowledge (ACK) signal. This line breaks up into a series of short lines to form the "daisy-chain" priority system. The ACK signal must pass through every controller that is equipped with Interrupt Control circuits. Refer to Figure 12 to determine order of priority. Back Panel wiring for interrupt control at a given position is: The Received ACK (RACKO) at Pin 122-1 and the Transmitted ACK (TACKO) at Pin 222-1. The daisy-chain bus is formed by a series of isolated lines which connect Terminal 222-1 of a given I/O position to Terminal 122-1 of the next position (lower priority). On unequipped positions, a jumper shorts 122-1 and 222-1 of the same connector to complete the bus. Back Panels are wired with jumpers from 122-1 and 222-1 must be removed from the Back Panel at that position.

On the IOU board location in the Processor Chassis, the daisy-chain starts at Terminal 220-0 (Slot 5) and normally goes to the Console TTY RACKO, Terminal 238-1 of the same slot. The TTY TACKO (239-1) is wired to Pin 122-1 at Slot 2 and continues through the I/O slots as described previously.

For controllers that occupy several positions, the jumper is removed only at the position where the controller board has ATN/ACK circuits. For details on the various devices, see the appropriate installation specification.

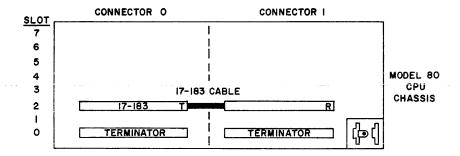

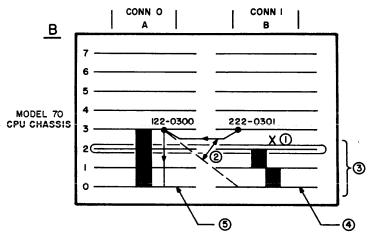

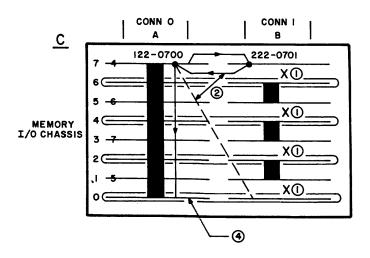

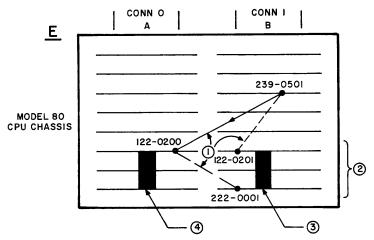

The Multiplexor Channel (I/O Bus), generated by the IOU Board, appears on Connector 0 of the Processor Chassis. It is connected to the copper wiring pattern on Connector 1 by the 17-183 cable. This cable is omitted when the SELCH or MBFR is installed in the Processor Chassis; Connector 1 then has the SELCH or Buffered Bus as the case may be. Connector 1 in Slots 00, 01, and 02 also has unidirectional DMA data busses which are wire wrapped together to form the bi-directional MSD Bus for the memory DMA port. See Figure 13.

Figure 13. Multiplexor/SELCH Bus Cabling

#### 8.4 System Configuration

System configuration data is provided in the User's Manual, Publication Number 29-261. Typical Configurations are shown in Figure 9.

#### 8.5 Terminators

The termination end of both legs, Connector 0 and 1, of the Multiplexor Bus must have a standard INTERDATA termination card (35-433) installed. These cards are installed on the back panel at the lowest numbered slot of both connectors of the Multiplexor Bus that exists. For example, if a Selector Channel or Bus Buffer is installed in Slot 4 on the first expansion chassis and only the Processor Chassis and one expansion chassis is used in the system, the Multiplexor Bus must be terminated at Slot 0, Connector 0; and Slot 5, Connector 1 of the expansion chassis. In addition, the Buffered Bus or the SELCH Bus should be terminated at Slot 0 and Connector 1 of this chassis.

Depending upon system configuration, any SELCH Bus or Buffered Bus may be terminated by a 15 inch Terminator (35-433) or a 10 inch Terminator (35-434). The choice of terminators depends on the type of chassis in which the last slot of the Bus is present.

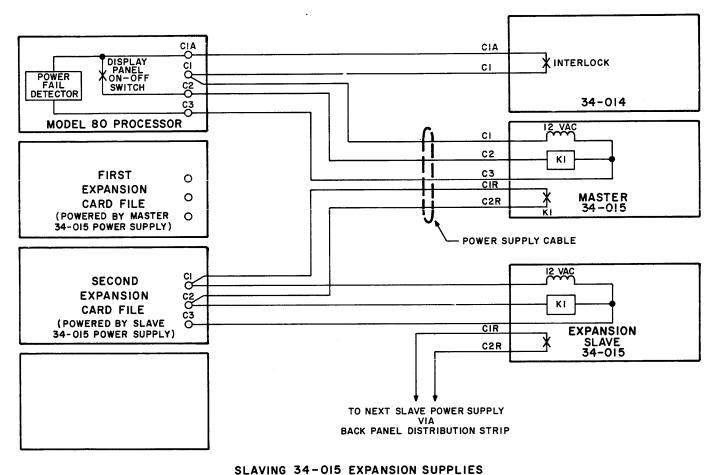

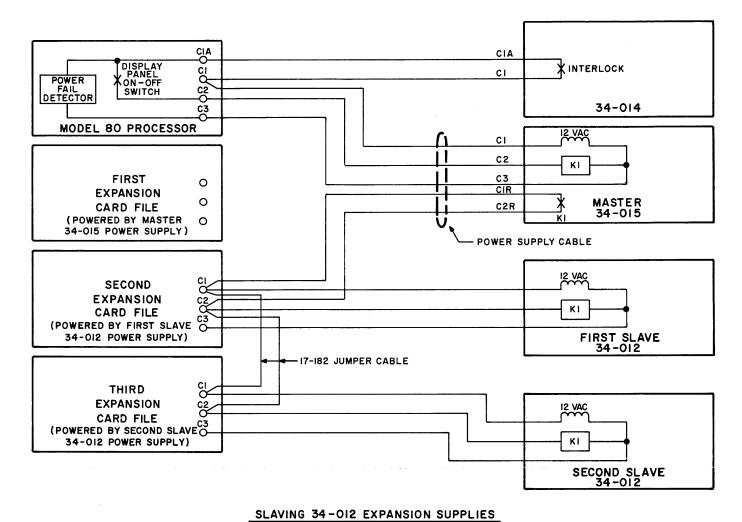

#### 8.6 Power Supply Configuration

The 34-015 logic power supply is capable of supplying 50 A of +5 VDC and can be used to drive the Processor and up to two Expansion Chassis at 115 VAC or the basic Processor Chassis and one Expansion Chassis at 230 VAC. The 34-015 and 34-012 supplies may be mixed as described for I/O expansion to reach an optimum power match to any configuration.

#### 9. CABLES

#### 9.1 Power Cable

The standard INTERDATA Cabinet is wired for 20 Amp service. On the main power cable (part of the AC Distribution Panel), the 20 Amp UL plug has one blade perpendicular to the other. A three wire, grounding, 20 Amp, 125 VAC receptable (Hubbel #5362 or equivalent) is required to accept this plug.

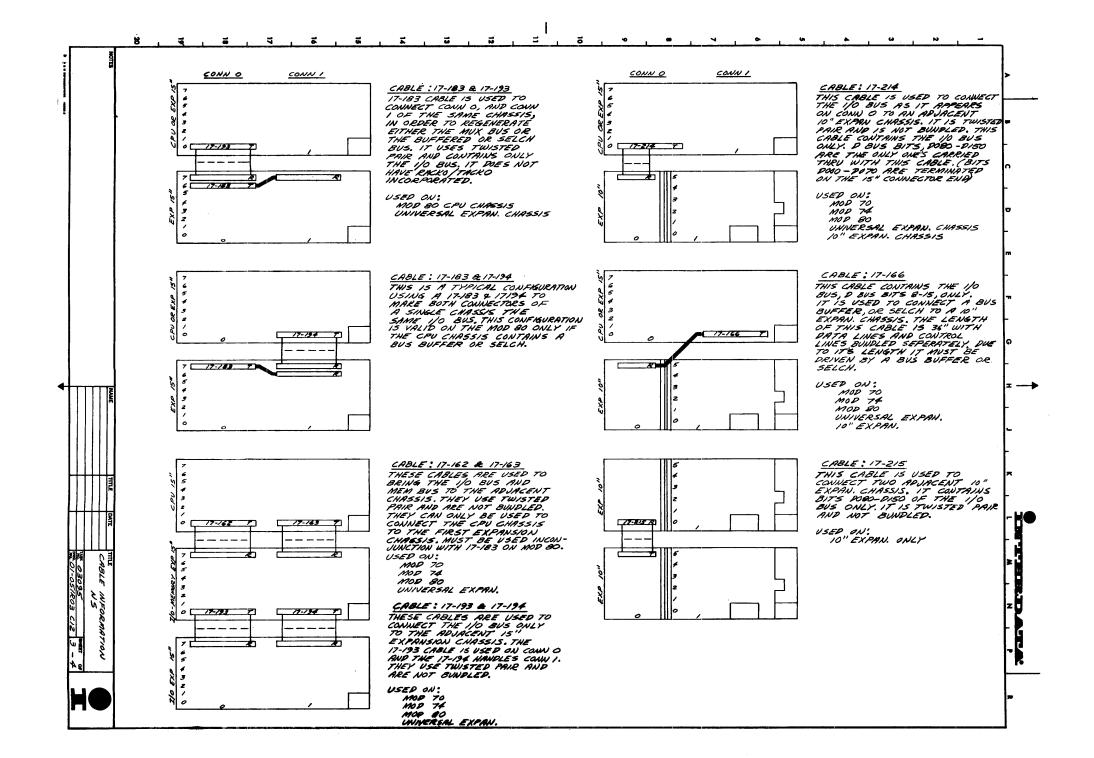

#### 9.2 System Expansion Cable

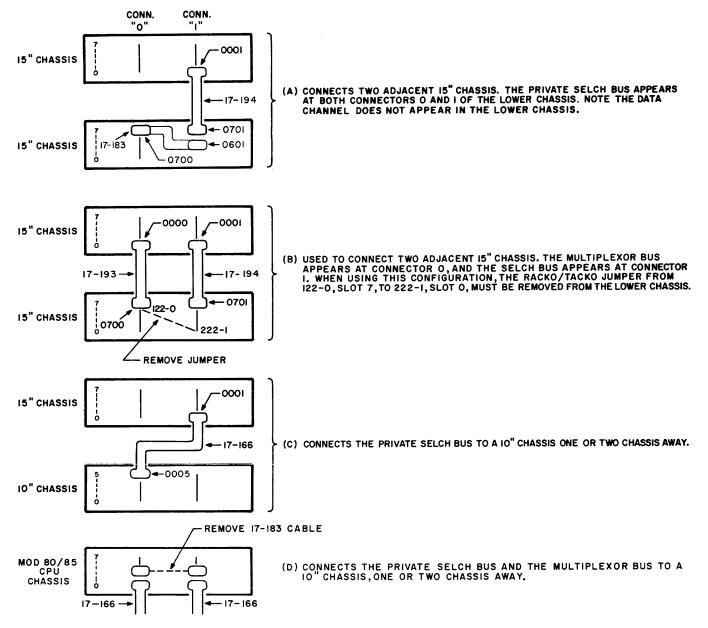

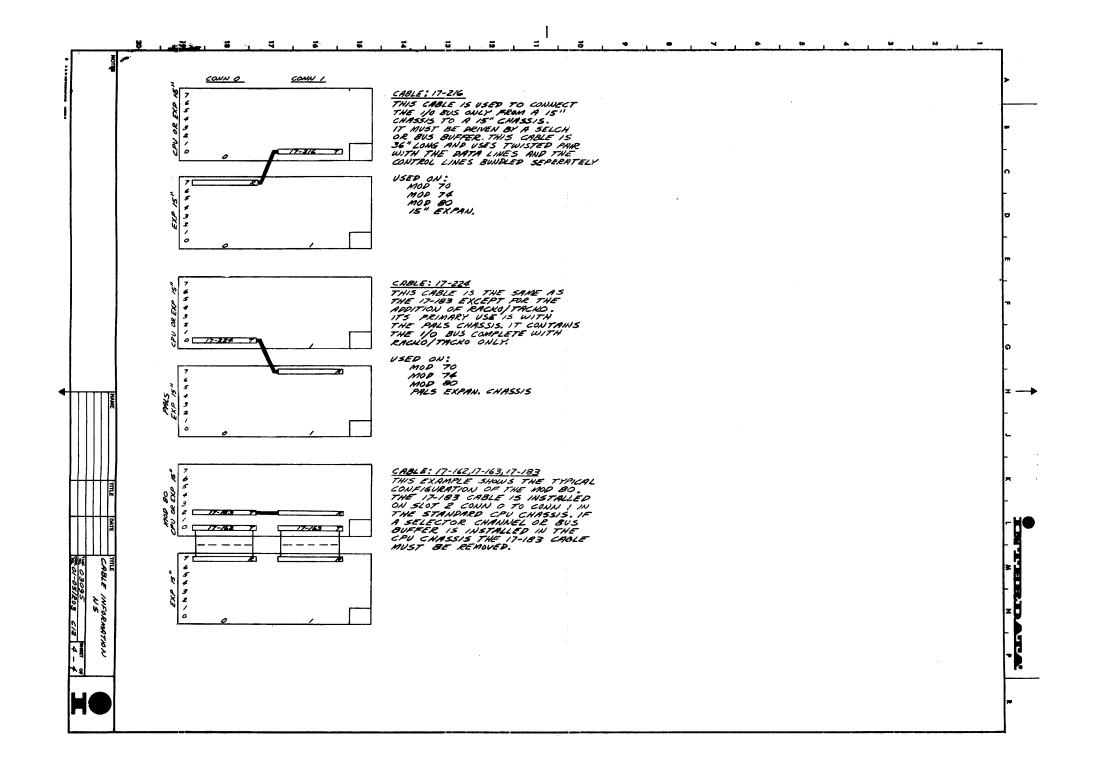

A number of standard cables are available for configuring systems made up of the INTERDATA expansion chassis discussed in Section 4. The choice of cables is dependent upon system configuration. The following cables are available:

1. 17-162 and 17-163: I/O and Memory Expansion Cable

This cable is used to connect the "0" connector field (17-162) and the "1" connector field (17-163) from the Processor to the corresponding connector in the first 15 inch expansion file. The expansion file must be mounted immediately below the basic Processor as these cables contain the DMA bus which is restricted to the first 15 inch expansion.

These cables are always used in pairs.

2. 17-193: I/O Expansion Cable, Connector "0"

This cable is used to connect the "0" connector field between two adjacent 15 inch card files.

3. 17-194: I/O Expansion Cable

This cable is used to connect the "1" connector I/O fields between two adjacent 15 inch card files.

4. 17-216: I/O Expansion Cable, 36 inch Long

This is a 36 inch long cable. It can be used to connect two 15 inch files that are not adjacent.

It must not be used to extend the basic Processor Mux Bus.

It can be used to extend a buffered bus or a SELCH Bus. It plugs into a "1" side connector. The "receiving" end can plug into the "0" or "1" side of the expansion file.

5. 17-214: 15 Inch to 10 Inch Expansion Cable

This cable is used to connect the "0" connector field of a 15 inch card file to a lower adjacent 10 inch card file. It provides an 8 bit I/O bus to the 10 inch card file.

6. 17-166: 15 Inch to 10 Inch I/O Expansion Cable, 36 Inch Long

This cable is used to connect the "1" side of a 15 inch expansion file to a 10 inch expansion file. It provides an 8 bit I/O bus to a 10 inch card file.

It must not be connected to the basic CPU Multiplexor Bus.

It may be driven either by a Selector Channel or a Bus Buffer.

It can be used on the older 10 inch card file, 13 I/O Slots with cards mounted vertically.

7. 17-183: "0" to "1" Connector

This cable can be used to interconnect the "0" field and the "1" field within a 15 inch card file.

It can also be used to connect a "0" side (slot "0") of a file, to the "1" side (slot 7) of the next adjacent file, or vice versa.

8. 17-215: 10 Inch to 10 Inch I/O Expansion Cable

This cable is used to connect 2 adjacent 10 inch card files.

#### 9.3 Typical Configurations

Information Drawing 01-051R03C12 depicts cabling for typical configurations.

#### 10. TESTING

#### 10.1 Standard Test Software

The following software is supplied with the basic Processor to insure that the System is operational:

| 1. | Processor Test Program | 06-106 |

|----|------------------------|--------|

| 2. | Memory Test Program    | 06-003 |

| 3. | Floating Point Test    | 06-108 |

| 4. | TTY Test Program       | 06-004 |

| 5. | Memory Hold Test       | 06-143 |

#### 10.2 Additional Software

In addition to the test software mentioned above, appropriate test software is supplied with each peripheral. When the system is equipped with the memory parity option, software package 06-144 is provided. The purpose of this routine is to initialize the memory to correct parity when power is initially applied or interrupted to the volatile semi-conductor Memory.

#### NOTE

Failure to initialize the complete memory to correct parity may result in erroneous parity errors even where correct parity is contained in the memory locations being referenced because of the "look-ahead" nature of the Model 80 Memory. Use MOS Parity Initialize Program 06-144.

# MODEL 80 MAINTENANCE SPECIFICATION

## TABLE OF CONTENTS

| 1. | INTE       | RODUCTI  | ON                                                                                                               | -  |

|----|------------|----------|------------------------------------------------------------------------------------------------------------------|----|

|    | 1.1<br>1.2 |          | ingsor                                                                                                           |    |

|    | 1.3        |          | emory                                                                                                            |    |

|    | 1.4        |          | Store                                                                                                            |    |

|    | 1.5        |          | Supply                                                                                                           |    |

|    | 1.6        |          | erals                                                                                                            | 2  |

| 2. | INTE       | ERNAL A  | RCHITECTURE                                                                                                      | 2  |

|    | 2.1        | Modules  | s                                                                                                                | 5  |

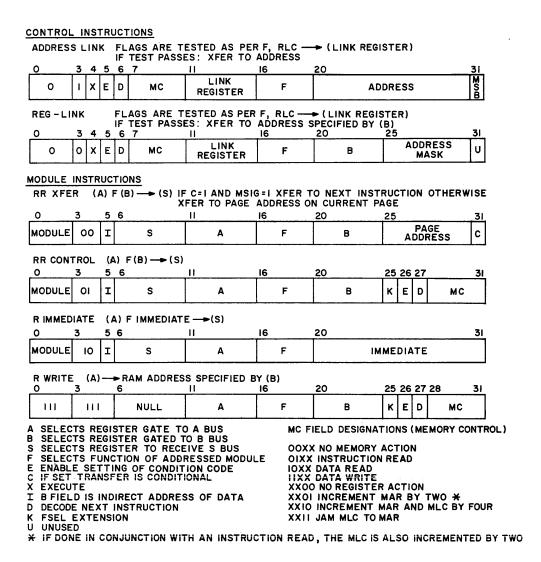

|    | 2.2        |          | Instructions                                                                                                     | 5  |

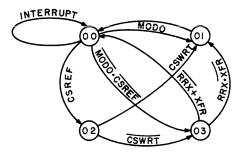

|    | 2.3        |          | pts                                                                                                              | 5  |

|    | 2.4        | _        | rs                                                                                                               | 5  |

|    | 2.5        | 0        | sor Timing                                                                                                       | 2  |

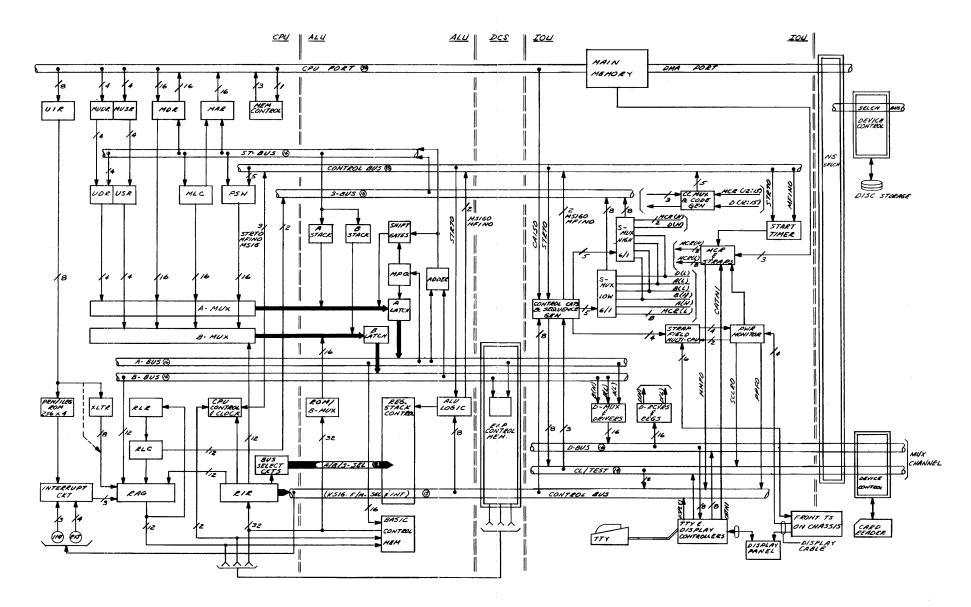

| 3. | FIIN       | CTIONA I | L DESCRIPTION OF THE BASIC PROCESSOR                                                                             | 9  |

| ٠. | ron        | OHONAI   | DEBORN HON OF THE BASIC PROCESSOR                                                                                | ٠  |

|    | 3.1        | Process  | sor Busses                                                                                                       | :  |

|    |            | 3.1.1    | Control Bus                                                                                                      | 3  |

|    |            | 3.1.2    | A, B, and S Busses                                                                                               | 4  |

|    |            | 3.1.3    | Typical Bus Exchange                                                                                             | 4  |

|    | 3.2        | Registe  | rs                                                                                                               | 4  |

|    |            | 3.2.1    | A Stack/B Stack                                                                                                  | 4  |

|    |            | 3.2.2    | Memory Data Register (MDR)                                                                                       | 4  |

|    |            | 3.2.3    | Memory Location Register (MLC)                                                                                   | 4  |

|    |            | 3.2.4    | Memory Address Register (MAR)                                                                                    | 4  |

|    |            | 3.2.5    | Program Status Word (PSW)                                                                                        | 5  |

|    |            | 3.2.6    | User Destination Register, User Source Register (UDR, USR)                                                       | Ę  |

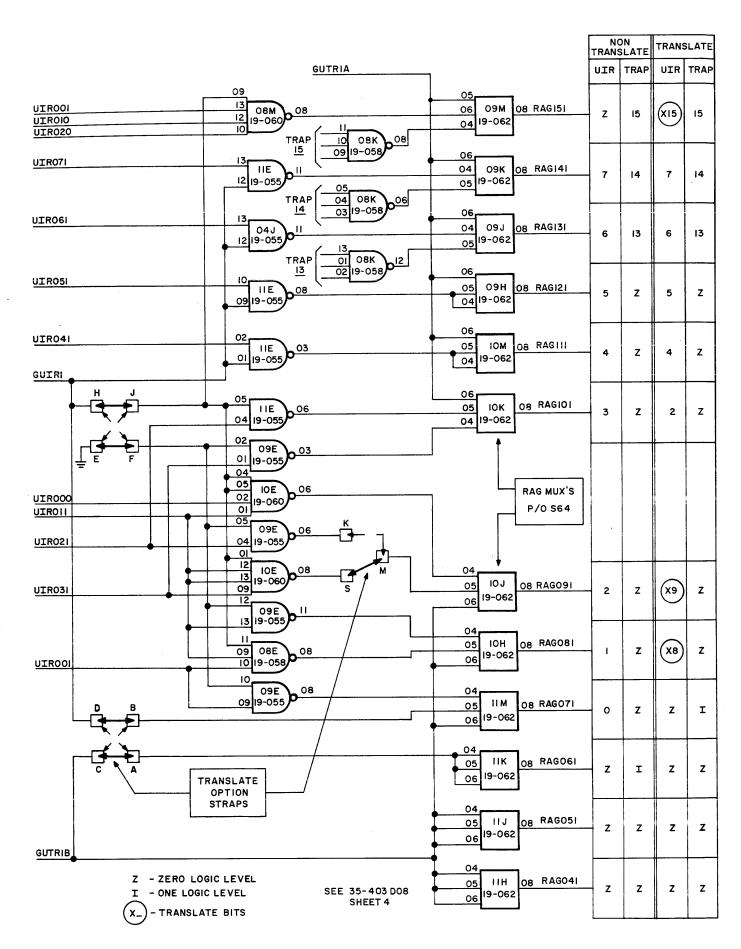

|    |            | 3.2.7    | User Instruction Register (UIR), Memory User Destination Register (MUDR), and Memory User Source Register (MUSR) | c  |

|    |            | 3.2.8    | ROM Location Register (RLR)                                                                                      | ŗ  |

|    |            | 3.2.9    | ROM Instruction Register (RIR)                                                                                   |    |

|    |            | 3.2.10   | A Latch/B Latch                                                                                                  | F  |

|    | 3.3        |          | pts                                                                                                              | Ę  |

|    | 3.4        |          | Store Memory                                                                                                     | Ę  |

|    | 3.5        |          | rogramming                                                                                                       | Ę  |

|    |            | 3.5.1    | Module 0                                                                                                         | 5  |

|    |            | 3.5.2    | Non-CPU Instructions                                                                                             | 7  |

|    |            | 3.5.3    | Micro-Control (MC)                                                                                               | 8  |

|    |            | 3.5.4    | Control Store Data Storage                                                                                       | ę  |

|    |            | 3.5.5    | Interrupts                                                                                                       | ç  |

|    |            | 3.5.6    | Registers                                                                                                        | 10 |

|    |            | 3.5.7    | CPU Flags                                                                                                        | 11 |

|    |            | 3.5.8    | Arithmetic Module (ALU) Programming                                                                              | 11 |

|    |            | 3.5.9    |                                                                                                                  | 12 |

|    | 3.6        |          | sor Block Diagram Analysis                                                                                       | 13 |

|    |            | 3.6.1    | ( 6 )                                                                                                            | 13 |

|    |            | 3.6.2    | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                                                                            | 15 |

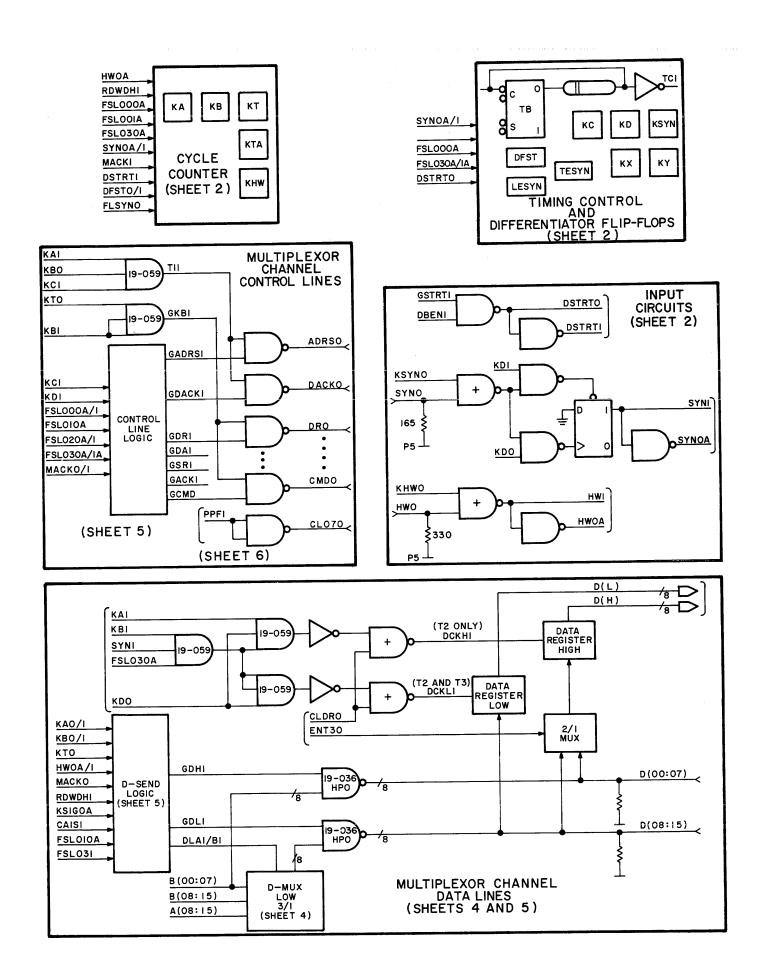

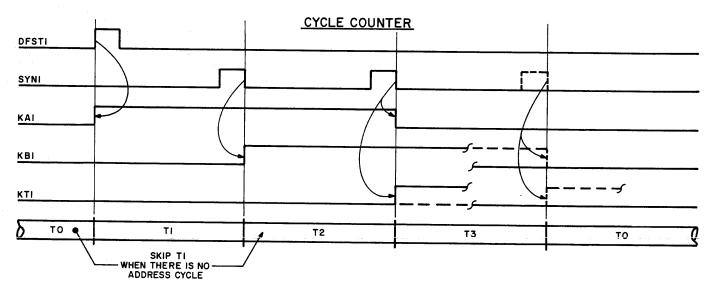

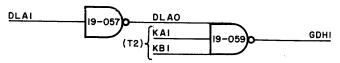

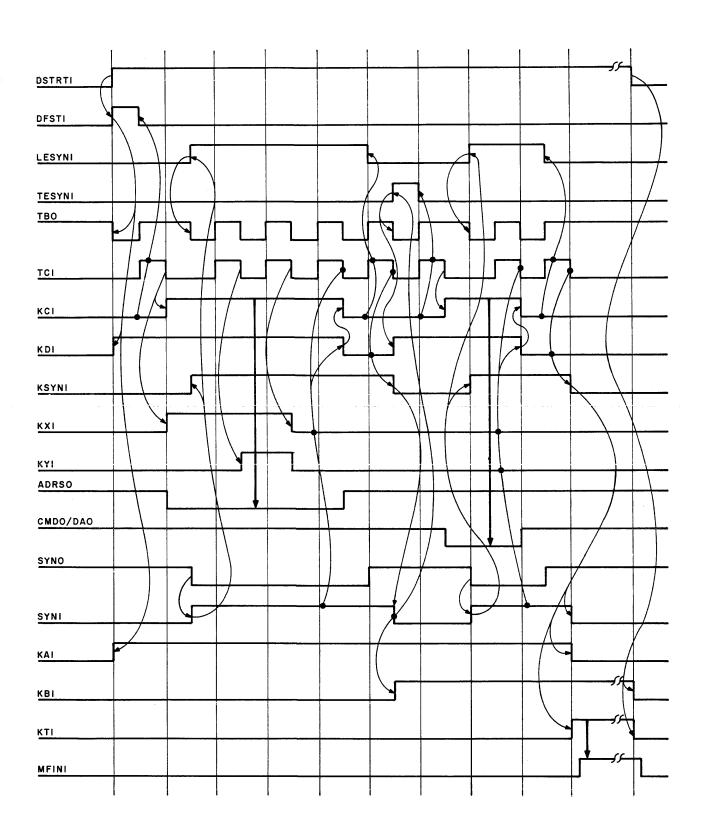

|    |            | 3.6.3    | IOU Board (Figure 3)                                                                                             | 16 |

# TABLE OF CONTENTS (CONTINUED)

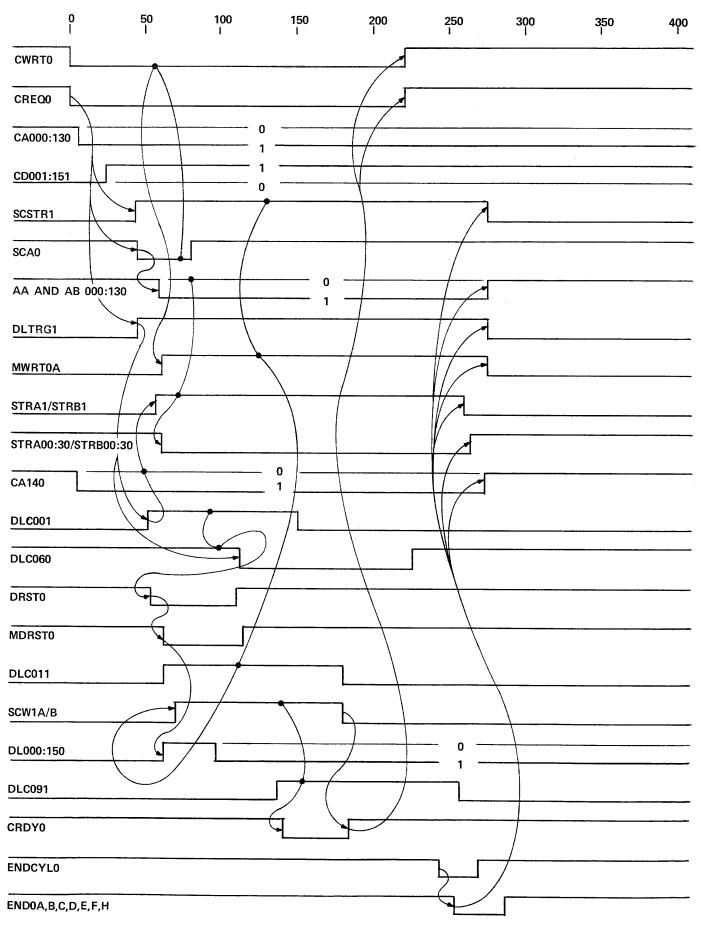

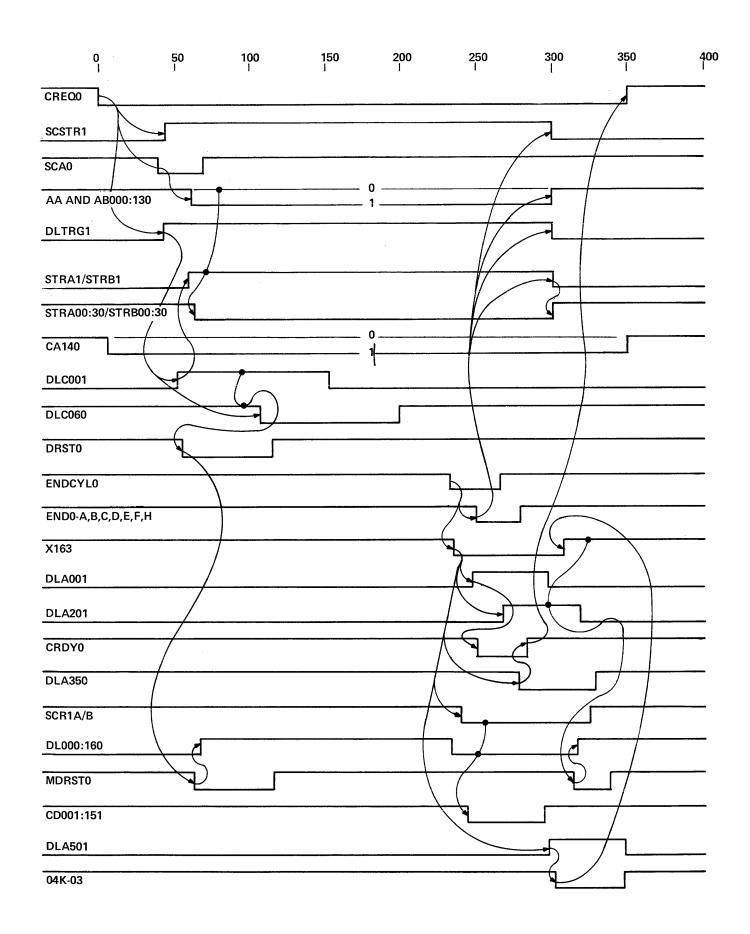

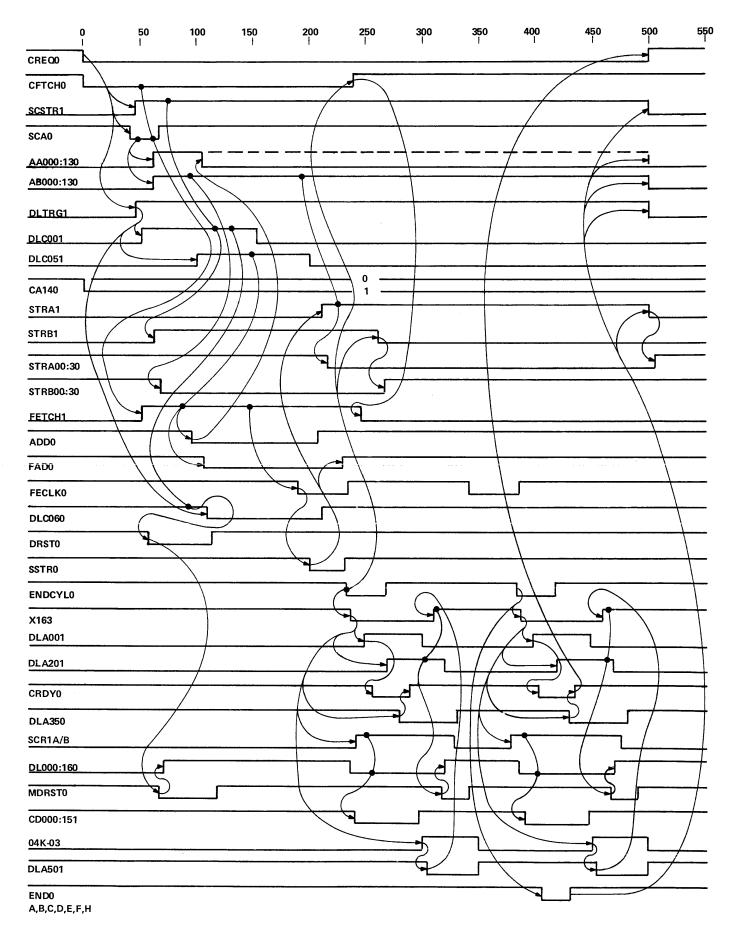

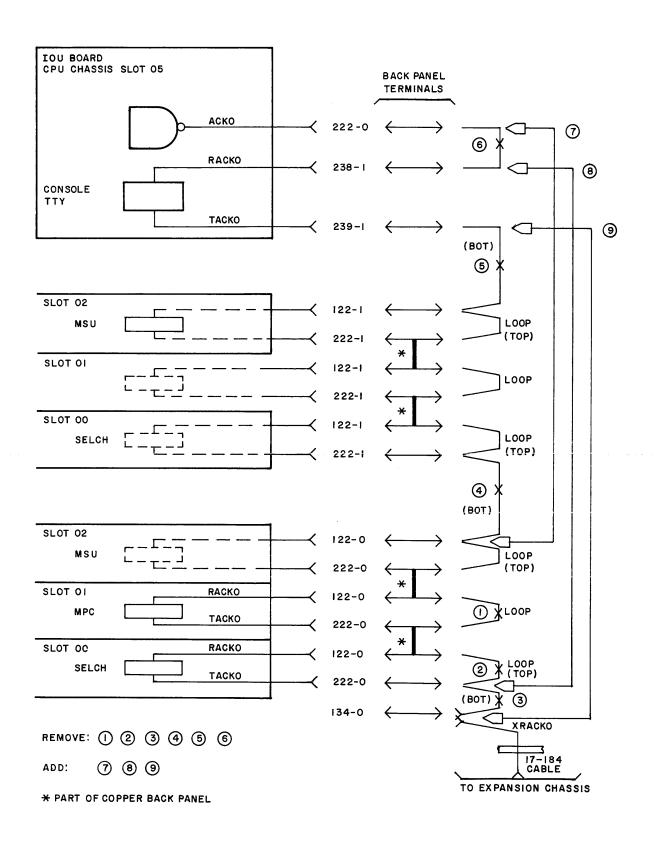

|     | 3.7        | Functional Diagram Analysis                               | 19         |

|-----|------------|-----------------------------------------------------------|------------|