# THEORY OF OPERATION

**OF**

# **INPUT SYSTEM**

**FOR**

AN/FSQ-7

COMBAT DIRECTION CENTRAL

AND

AN/FSQ-8

COMBAT CONTROL CENTRAL

1 December 1958

This document contains information of a proprietary nature. Any use or reproduction of this document for other than government purposes is subject to the prior consent of International Business Machines Corporation.

MILITARY PRODUCTS DIVISION

INTERNATIONAL BUSINESS MACHINES CORPORATION

KINGSTON, NEW YORK

Reproduction for non-military use of the information or illustrations contained in this publication is not permitted without specific approval of the issuing service (BuAer or USAF). The policy for use of classified publications is established for the Air Force in AFR 205-1 and for the Navy in Navy Regulations, Article 1509.

# **—LIST OF REVISED PAGES -**INSERT LATEST REVISED PAGES. DESTROY SUPERSEDED PAGES. NOTE: The portion of the text affected by the current revision is indicated by a vertical rule in the left margin of a left-hand page and in the right margin of a right-hand page. \*The asterisk indicates pages revised, added or deleted by the current revision.

# **CONTENTS**

| Heading |                                       | Page |

|---------|---------------------------------------|------|

| PART    | 1 INTRODUCTION                        | 1    |

| СНАР    | TER 1 GENERAL                         | 1    |

| 1.1     | Scope of Manual                       |      |

| 1.2     | AN/FSQ-7 Combat Direction Central     |      |

| 1.3     | Input Systems in General              |      |

| 1.4     | AN/FSQ-7 Input System                 |      |

| 1.4.1   | General                               |      |

| 1.4.2   | LRI Element                           |      |

| 1.4.3   | GFI Element                           |      |

| 1.4.4   | XTL Element                           |      |

| 1.4.5   | LRI Monitor                           | 3    |

| 1.4.6   | Test Pattern Generator                | 3    |

| CHAP    | TER 2 DATA SOURCES AND TRANSMISSION   | 5    |

| 2.1     | LRI Data                              | 5    |

| 2.1.1   | General                               | 5    |

| 2.1.2   | Long-Range Search Radar Data          | 5    |

| 2.1.3   | MK X IFF Radar Beacon Data            | 5    |

| 2.1.4   | Height-Finder Radar Data              | 6    |

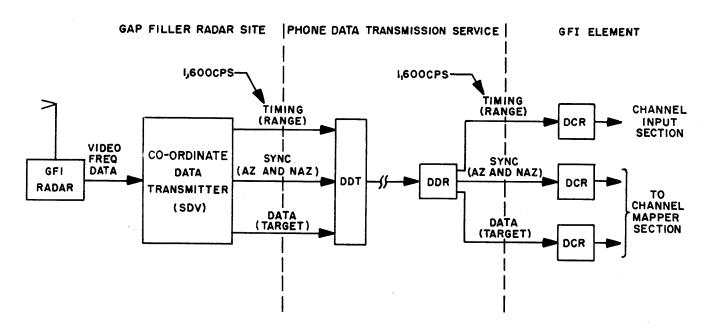

| 2.2     | GFI Data                              | 6    |

| 2.2.1   | General                               | 6    |

| 2.2.2   | Slowed-Down Video                     | 6    |

| 2.3     | XTL Data                              | 6    |

| 2.4     | Telephone Transmission of Data        | 6    |

| 2.4.1   | LRI Data                              | 7    |

| 2.4.2   | GFI Data                              | 7    |

| 2.4.3   | XTL Data                              | 7    |

| СНАРТ   | TER 3 DATA PROCESSING IN INPUT SYSTEM | 9    |

| 3.1     | General                               | 9    |

| 3.2     | LRI Data                              | 10   |

| Heading         |                                           | Page |

|-----------------|-------------------------------------------|------|

| 3.3             | GFI Data                                  | 10   |

| 3.4             | XTL Data                                  | 11   |

| CHAPTE          | R 4 MONITORING AND TEST EQUIPMENT         | . 13 |

| 4.1             | Long-Range Radar Input Monitor C-2021/FSQ | 13   |

| 4.2             | Test Pattern Generator TS-923/FSQ         | . 13 |

| 4.2.1           | General                                   | 13   |

| 4.2.2           | Test Signals                              | . 13 |

| 4.2.2.1         | LRI TPG Signals                           | . 13 |

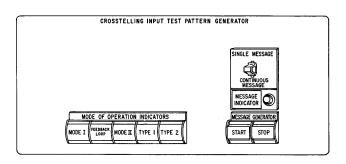

| 4.2.2.2         | XTL TPG Signals                           | . 13 |

| 4.2.2.3         | GFI TPG Signals                           | . 13 |

| 4.2.3           | Physical Description                      | . 14 |

| 4.2.4           | Modes of Operation                        | . 14 |

| 4.2.4.1         | General                                   | . 14 |

| 4.2.4.2         | LRI and XTL TPG's                         | . 14 |

| 4.2.4.3         | GFI TPG                                   | . 14 |

| CHAPTE          | R 5 SIMPLEX MAINTENANCE CONSOLE           | 15   |

| 5.1             | Method of Presentation                    | 15   |

| 5.2             | Purpose of Equipment                      | 15   |

| 5.3             | Physical Description                      | 16   |

| 5.3.1           | Differences between Systems               | 16   |

| 5.3.2           | Present Systems                           | 16   |

| 5.3.3           | Future Systems                            | 16   |

| 5.4             | Functional Description                    |      |

| 5.4.1           | General                                   |      |

| 5.4.2           | TPG Control Panels                        |      |

| 5.4.3           | Channel Control Panels                    | _    |

| 5.4.4           | CEP Control Panel                         |      |

| 5.4.5           | Power Control Panels                      |      |

|                 | Marginal Check Panel                      |      |

| 5.4.6<br>\$ 4.7 | Miscellaneous Panels                      | 17   |

| S /1 /          | WOSCHIADROUS PAURIS                       | 1./  |

| Heading |                                                       | Page |

|---------|-------------------------------------------------------|------|

| PART 2  | LONG-RANGE RADAR INPUT ELEMENT                        | 19   |

| CHAPTER | ? 1 INTRODUCTION                                      | 19   |

| 1.1     | General                                               |      |

| 1.2     | Function of Long-Range Radar Input Element            | . 19 |

| 1.3     | Relationship of LRI Element to Sources of Information | . 19 |

| 1.4     | Physical Description                                  | . 20 |

| 1.5     | Message and Drum Word Layout                          | . 20 |

| 1.5.1   | Fine Grain Data Message                               | . 21 |

| 1.5.2   | MK X IFF Message                                      | . 21 |

| 1.5.3   | Height-Finder Message                                 | . 21 |

| 1.6     | General Functional Description                        | . 21 |

| 1.6.1   | Input Switching                                       | . 22 |

| 1.6.2   | Channel Input Section                                 | . 22 |

| 1.6.3   | Duplex Switching Section                              | . 22 |

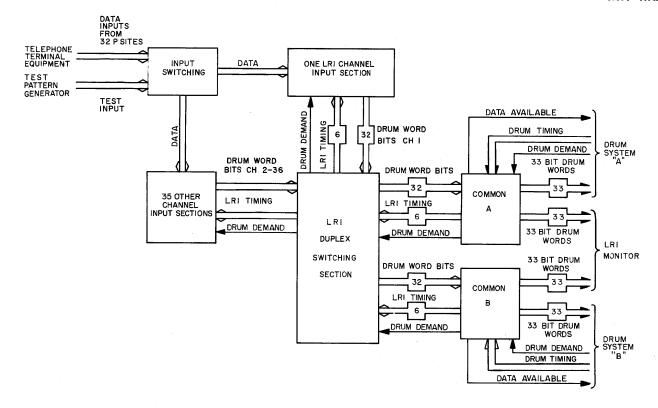

| 1.6.4   | Common Equipment                                      | . 23 |

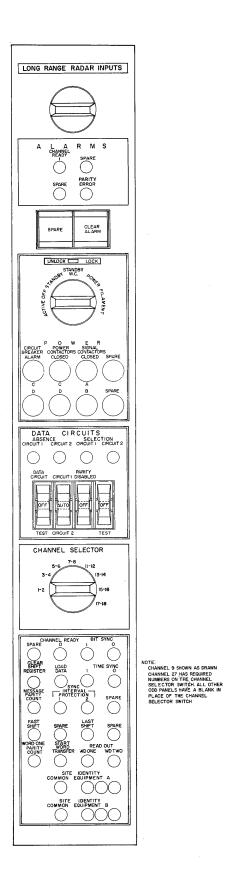

| 1.7     | Simplex Maintenance Console LRI Control Panels        | . 23 |

| 1.7.1   | General                                               | . 23 |

| 1.7.2   | Function of LRI Control Panel Switches                | . 23 |

| CHAPTER | 2 INPUT SWITCHING                                     | . 27 |

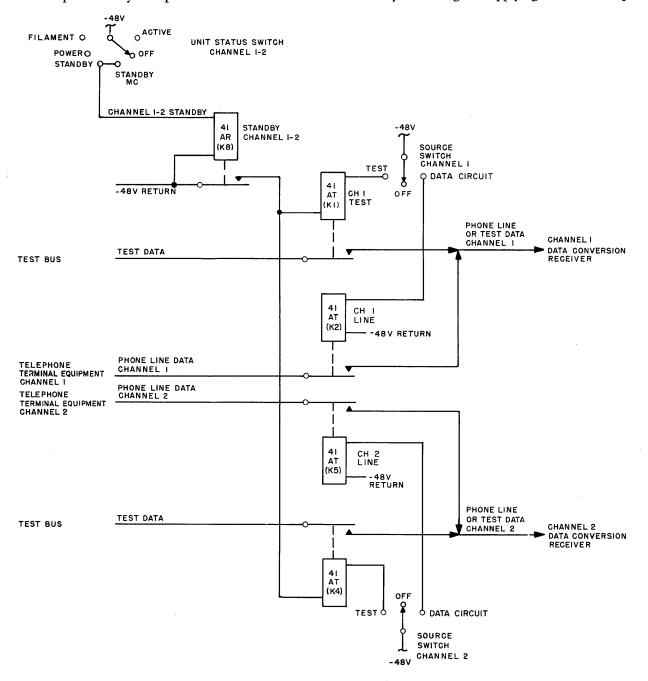

| 2.1     | General                                               | . 27 |

| 2.2     | Input Data Switching                                  | 27   |

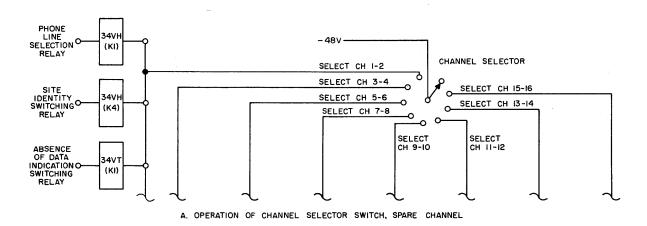

| 2.3     | Spare-Channel Switching                               | . 27 |

| 2.3.1   | General                                               | . 27 |

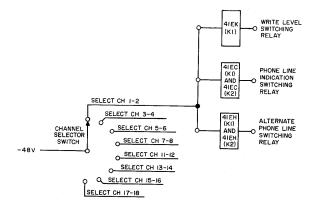

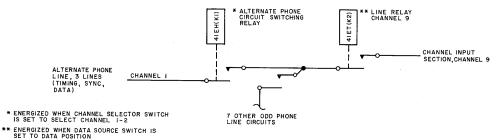

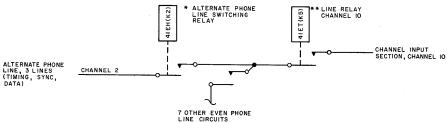

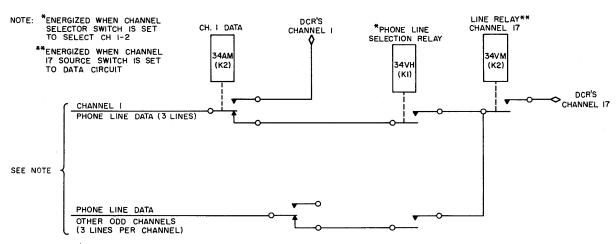

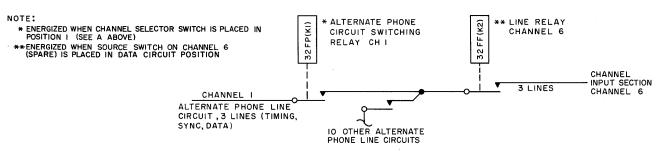

| 2.3.2   | Alternate Telephone-Line Switching                    | 28   |

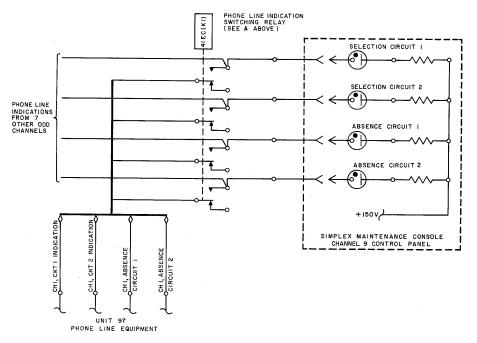

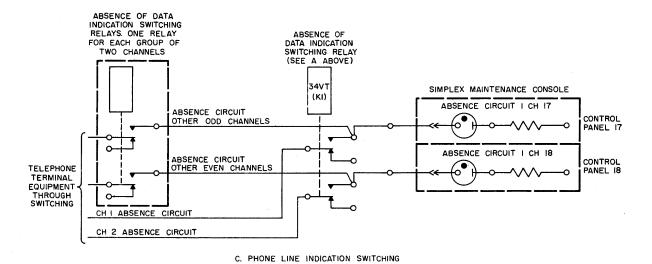

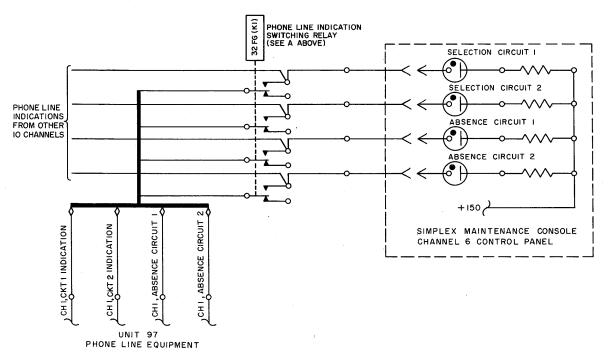

| 2.3.3   | Switching of Basic Telephone Terminal Indications     | 30   |

| CHAPTER | 3 CHANNEL INPUT SECTION                               | 31   |

| 3.1     | Introduction                                          | 31   |

| 3.2     | Data Converter and Synchronizer                       | 32   |

| 3.3     | Primary Core Shift Register and Controls              | 34   |

| 3.4     | Parity Alarm and Busy Bit Detector                    | 37   |

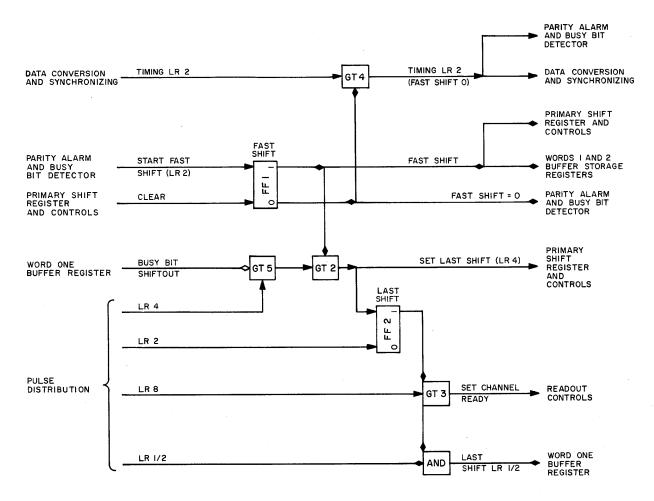

| 3.5     | Fast-Shift Controls                                   | 38   |

| Heading     |                                                                          | Page |

|-------------|--------------------------------------------------------------------------|------|

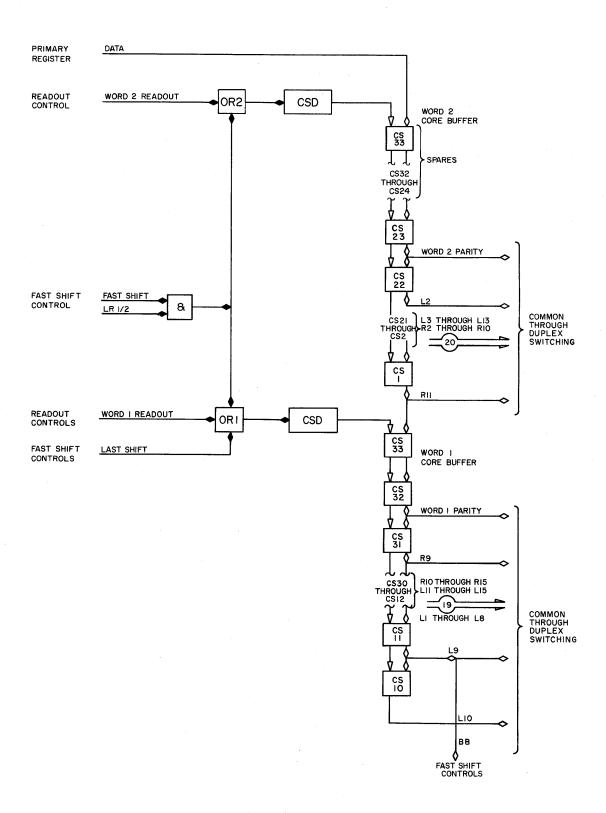

| 3.6         | Word 1 and Word 2 Core Buffer Registers                                  | . 39 |

| 3.7         | Readout Control Circuit                                                  | . 41 |

| СНАРТЕ      | R 4 DUPLEX SWITCHING                                                     | . 43 |

| 4.1         | General                                                                  |      |

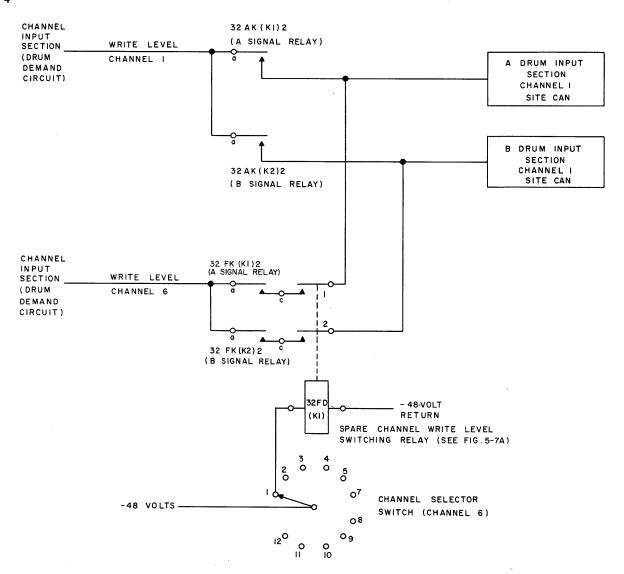

| 4.2         | Driving of A and B Signal Relays                                         | . 43 |

| 4.3         | Core-Data Switching                                                      |      |

| 4.4         | Write Level Switching                                                    |      |

| 4.5         | Readout Alarm Switching                                                  |      |

| 4.6         | Timing Pulse and Level Switching                                         |      |

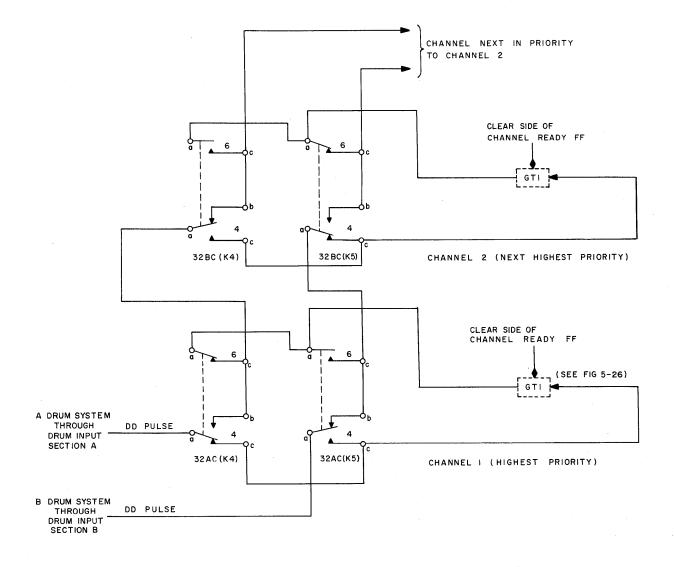

| <b>4.</b> 7 | Drum-Demand Switching                                                    |      |

| 4.7.1       | Drum-Demand Switching for Channels 1 and 2                               |      |

| 4.7.2       | Drum-Demand Switching for Channels 3 and 4                               |      |

| 4.8         | Site Neon Indication Switching                                           |      |

| 4.9         | Status Indication Switching                                              |      |

| CHAPTE      | R 5 COMMON EQUIPMENT                                                     | 51   |

| 5.1         | Introduction                                                             | 51   |

| 5.2         | Pulse Generator                                                          | 53   |

| 5.3         | Drum-Demand Control                                                      | 54   |

| 5.3.1       | Generation of Drum-Demand Pulses                                         | 55   |

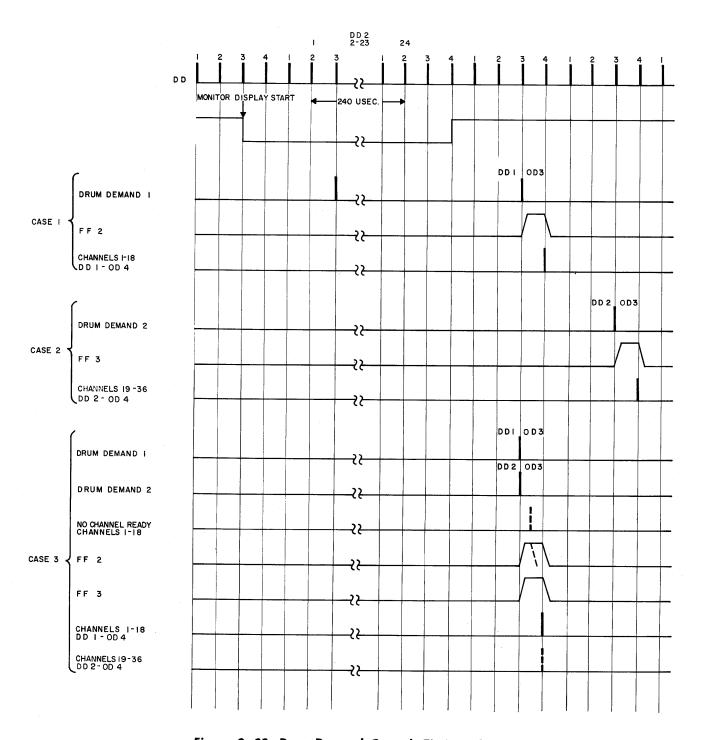

| 5.3.1.1     | Case 1: Drum-Demand 1 Pulse Received                                     | 57   |

| 5.3.1.2     | Case 2: Drum-Demand 2 Pulse Received                                     | 58   |

| 5.3.1.3     | Case 3: Drum-Demand 1 and Drum-Demand 2 . Pulses Received Simultaneously | 58   |

| 5.3.2       | Inhibiting of Drum-Demand Pulses during LRI Monitor Display              | 58   |

| 5.4         | Site Identity Generator                                                  | 59   |

| 5.5         | Clock                                                                    | 60   |

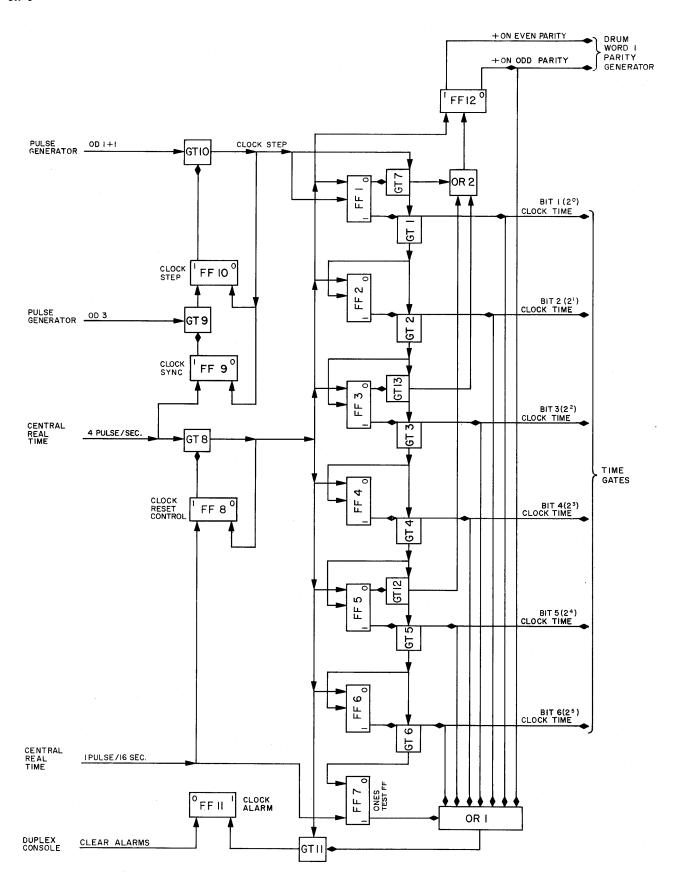

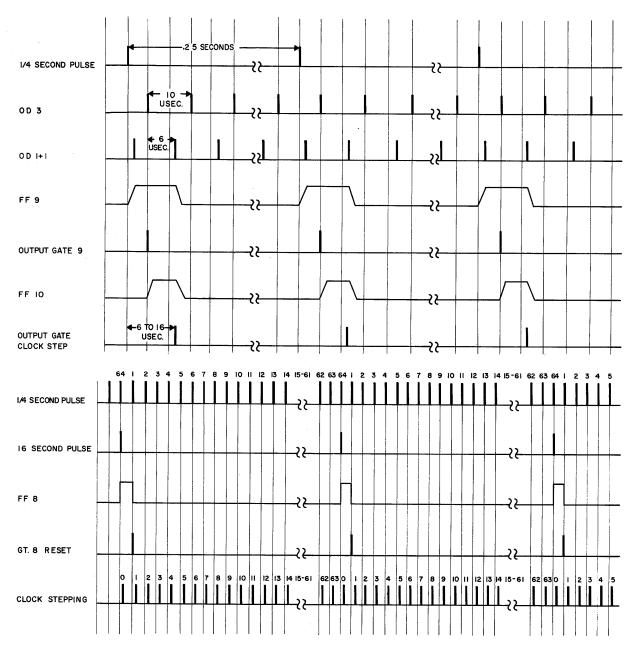

| 5.5.1       | Clock Stepping and Synchronizing                                         | 61   |

| 5.5.2       | Clock Indication (6-Stage Binary Counter)                                | 62   |

| 5.5.3       | Clock Parity Generator                                                   | 63   |

| 5.5.4       | Clock Test                                                               | 64   |

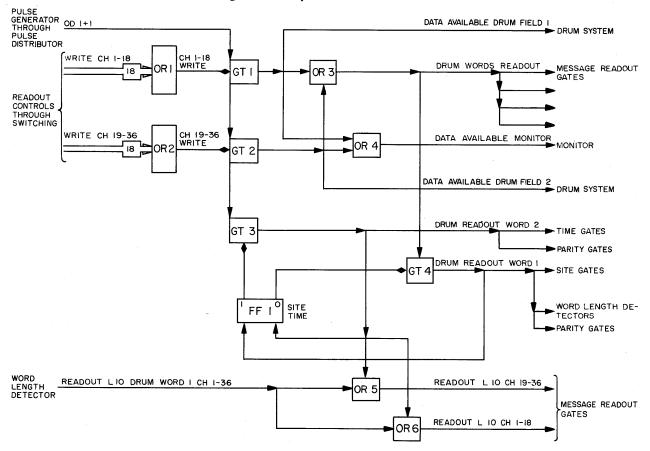

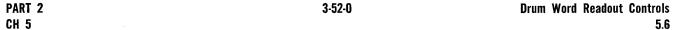

| 5.6         | Drum Word Readout Controls                                               | 64   |

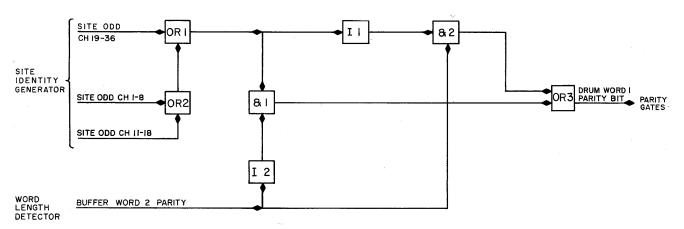

| 5.7         | Drum Word 1 Parity Generator                                             | 68   |

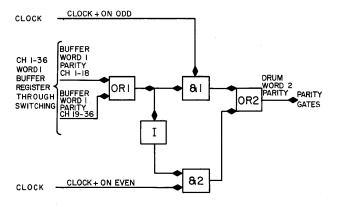

| 5.8         | Drum Word 2 Parity Generator                                             | 69   |

| Heading |                                                                 | Page |

|---------|-----------------------------------------------------------------|------|

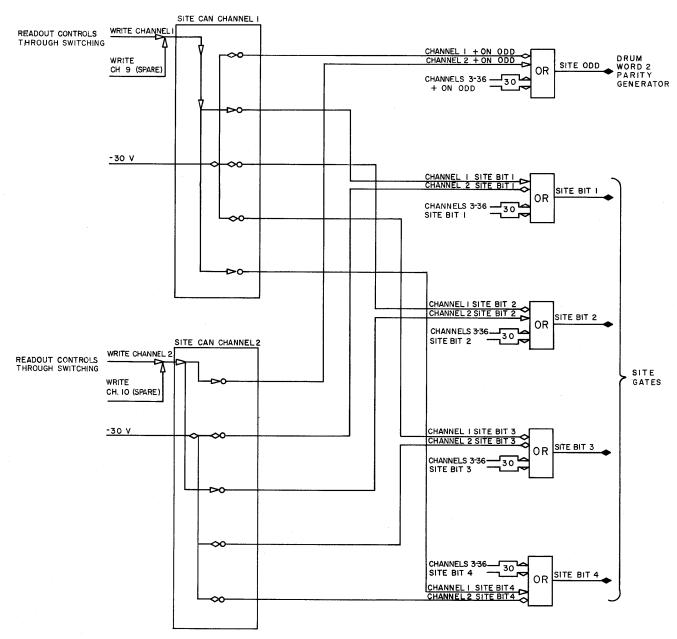

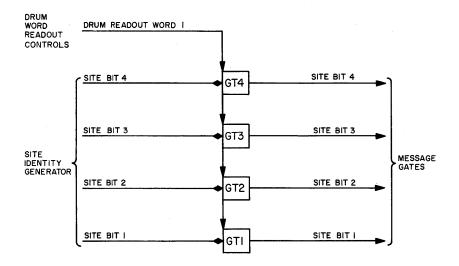

| 5.9     | Site Gates                                                      | . 70 |

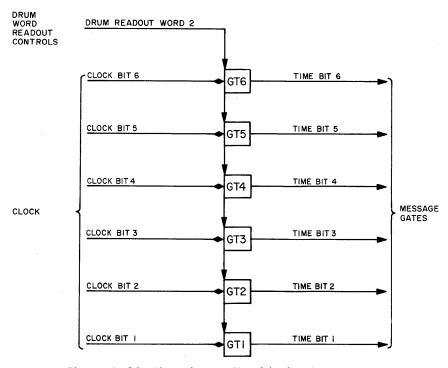

| 5.10    | Time Gates                                                      | . 71 |

| 5.11    | Parity Gates                                                    | . 71 |

| 5.12    | Message Readout Gates                                           | . 72 |

| 5.13    | Readout Alarm                                                   | 74   |

| 5.14    | Word-Length Detector Circuit                                    | . 75 |

| PART 3  | LONG-RANGE RADAR INPUT MONITOR C-2021/FSQ                       | . 77 |

| CHAPTER | 1 INTRODUCTION                                                  | 77   |

| 1.1     | Scope of Part                                                   | 77   |

| 1.2     | Purpose of Equipment                                            | 77   |

| 1.3     | Physical Description                                            | 77   |

| 1.3.1   | Display Consoles                                                | 77   |

| 1.3.1.1 | General Features                                                | 77   |

| 1.3.1.2 | Units 622 and 623                                               | 77   |

| 1.3.1.3 | Unit 620                                                        | 77   |

| 1.3.1.4 | Unit 621                                                        | 77   |

| 1.3.2   | Unit 93                                                         | 79   |

| 1.4     | System Theory of Operation                                      | 79   |

| 1.4.1   | Position of LRI Monitor in AN/FSQ-7 Combat<br>Direction Central | 79   |

| 1.4.2   | Composition of LRI Message                                      | 79   |

| 1.4.3   | Synchronization with LRI Element                                | 80   |

| 1.4.4   | Duplexing                                                       | 80   |

| 1.5     | Mathematical Basis of Theory of Operation                       | 80   |

| 1.5.1   | General                                                         | 80   |

| 1.5.2   | Generation of PPI Display                                       | 83   |

| 1.5.3   | Determination of Deflection Values                              | 83   |

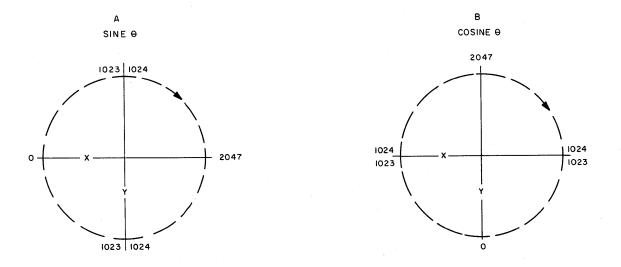

| 1.5.4   | Sine and Cosine Approximation                                   | 83   |

| 1.5.5   | Target Presentation                                             | 83   |

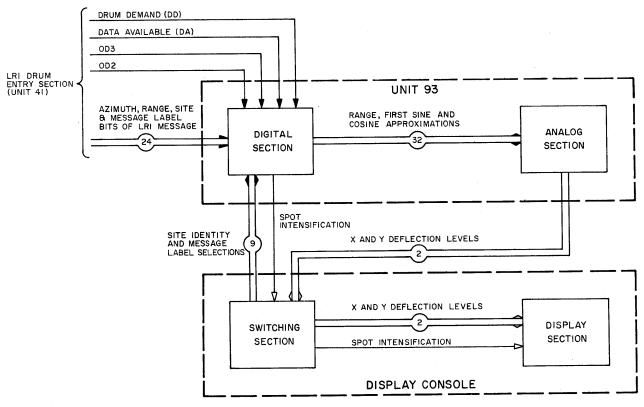

| 1.6     | General Functional Description                                  | 84   |

| 1.6.1   | LRI Monitor Sections                                            | 84   |

| 1.6.2   | Digital Section                                                 | 84   |

| 1.6.3       Analog Section       8         1.6.4       Display Section       8         1.6.5       Switching Section       8         CHAPTER 2 DIGITAL SECTION         2.1       Overall Theory of Operation       8         2.1.1       General       8         2.1.2       Message Selection       8         2.1.3       Target Data Conversion       8         2.1.4       Synchronization and Timing       8 | zе |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.6.5       Switching Section       8         CHAPTER 2 DIGITAL SECTION       8         2.1       Overall Theory of Operation       8         2.1.1       General       8         2.1.2       Message Selection       8         2.1.3       Target Data Conversion       8                                                                                                                                       | 5  |

| CHAPTER 2 DIGITAL SECTION       8         2.1 Overall Theory of Operation       8         2.1.1 General       8         2.1.2 Message Selection       8         2.1.3 Target Data Conversion       8                                                                                                                                                                                                             | 5  |

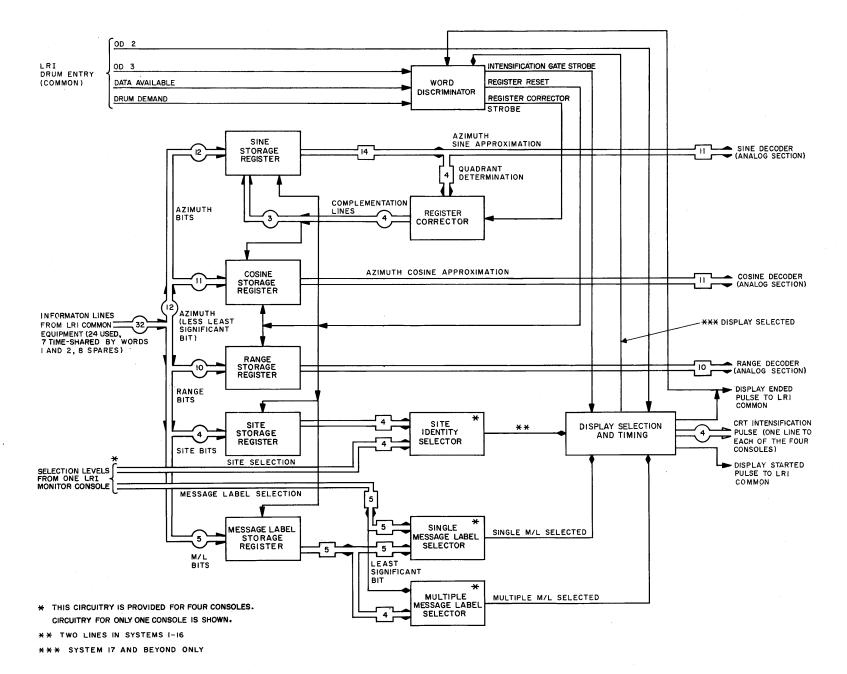

| 2.1       Overall Theory of Operation       8         2.1.1       General       8         2.1.2       Message Selection       8         2.1.3       Target Data Conversion       8                                                                                                                                                                                                                               | 5  |

| 2.1.1 General       8         2.1.2 Message Selection       8         2.1.3 Target Data Conversion       8                                                                                                                                                                                                                                                                                                       | 7  |

| 2.1.2Message Selection82.1.3Target Data Conversion8                                                                                                                                                                                                                                                                                                                                                              | 7  |

| 2.1.3 Target Data Conversion 8                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                         | 7  |

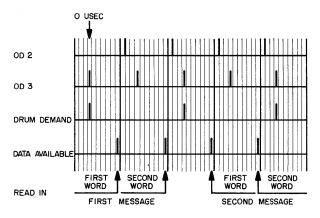

| 2.1.4 Synchronization and Timing 8                                                                                                                                                                                                                                                                                                                                                                               | 7  |

| ,                                                                                                                                                                                                                                                                                                                                                                                                                | 7  |

| 2.1.4.1 General 8                                                                                                                                                                                                                                                                                                                                                                                                | 7  |

| 2.1.4.2 Systems 17 and Beyond 8                                                                                                                                                                                                                                                                                                                                                                                  | 7  |

| 2.1.4.3 Systems 1 through 16 9                                                                                                                                                                                                                                                                                                                                                                                   | 0  |

| 2.2 Message Selection Circuits 9                                                                                                                                                                                                                                                                                                                                                                                 | 0  |

| 2.2.1 Site Identity and Message Label Storage Registers 9                                                                                                                                                                                                                                                                                                                                                        | 0  |

| 2.2.2 Site Identity Selector 9                                                                                                                                                                                                                                                                                                                                                                                   | 1  |

| 2.2.2.1 General 9                                                                                                                                                                                                                                                                                                                                                                                                | 1  |

| 2.2.2.2 Systems 17 and Beyond 9                                                                                                                                                                                                                                                                                                                                                                                  | 1  |

| 2.2.2.3 Systems 1 through 16                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

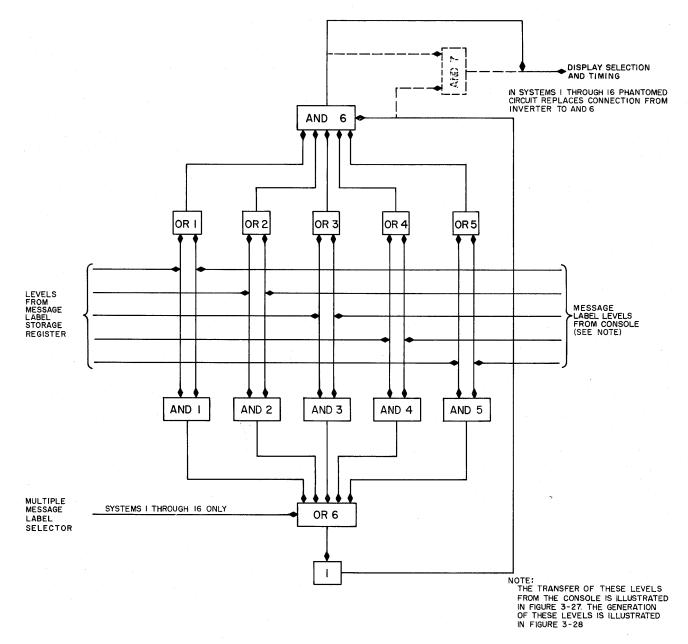

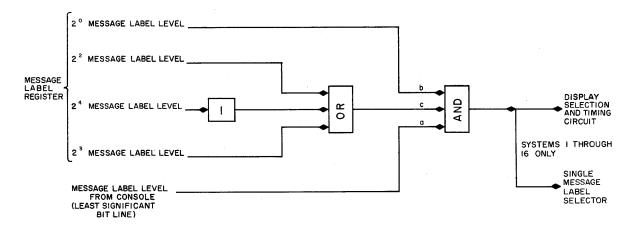

| 2.2.3 Single-Message Label Selector                                                                                                                                                                                                                                                                                                                                                                              | )2 |

| 2.2.3.1 General 9                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

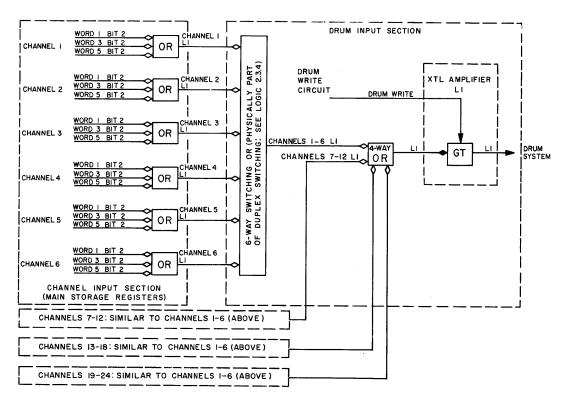

| 2.2.3.2 Differences in Systems 1 through 16                                                                                                                                                                                                                                                                                                                                                                      | )3 |

| 2.2.4 Multiple-Message Label Selector 9                                                                                                                                                                                                                                                                                                                                                                          | )3 |

| 2.3 Target Data Conversion 9                                                                                                                                                                                                                                                                                                                                                                                     | )4 |

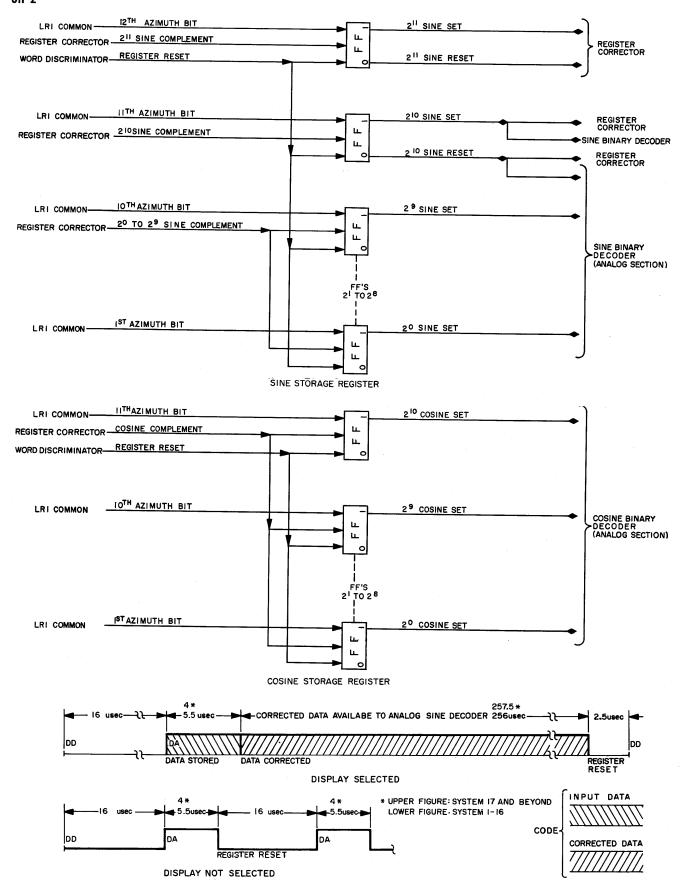

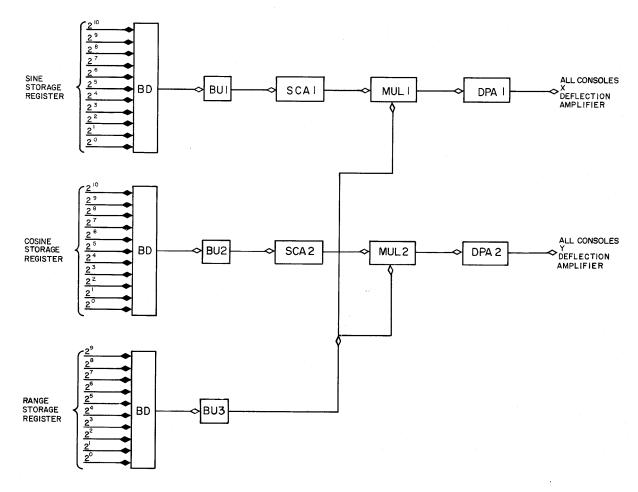

| 2.3.1 Sine Storage and Cosine Storage Registers                                                                                                                                                                                                                                                                                                                                                                  | 4  |

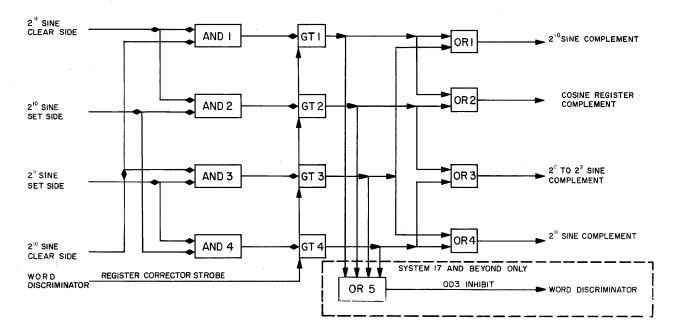

| 2.3.2 Register Corrector                                                                                                                                                                                                                                                                                                                                                                                         | 96 |

| 2.3.3 Range Storage Register                                                                                                                                                                                                                                                                                                                                                                                     | 7  |

| 2.4 Synchronization and Timing 9                                                                                                                                                                                                                                                                                                                                                                                 | 9  |

| 2.4.1 Word Discriminator                                                                                                                                                                                                                                                                                                                                                                                         | 9  |

| 2.4.1.1 Systems 17 and Beyond                                                                                                                                                                                                                                                                                                                                                                                    | 9  |

| 2.4.1.2 Systems 1 through 16                                                                                                                                                                                                                                                                                                                                                                                     | 9  |

| 2.4.2 Display Selection and Timing Circuit                                                                                                                                                                                                                                                                                                                                                                       | 99 |

| 2.4.2.1 General                                                                                                                                                                                                                                                                                                                                                                                                  | 99 |

| 2.4.2.2 Systems 1 through 16                                                                                                                                                                                                                                                                                                                                                                                     | )0 |

| Heading |                                                 | Page  |

|---------|-------------------------------------------------|-------|

| CHAPTE  | R 3 ANALOG SECTION                              | 101   |

| 3.1     | General                                         | 101   |

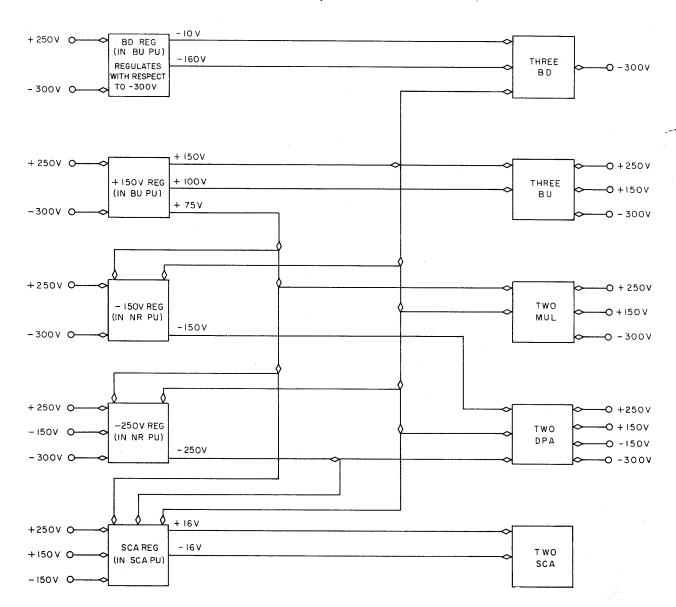

| 3.2     | Binary Decoders                                 | . 101 |

| 3.3     | Buffer Amplifiers                               | 102   |

| 3.4     | Sine and Cosine Approximators                   | 102   |

| 3.5     | Multipliers                                     | 102   |

| 3.6     | Distribution Power Amplifiers                   | 102   |

| 3.7     | Power Supplies                                  | 102   |

| 3.8     | Analog Calibration                              | 102   |

| 3.8.1   | Alignment Panel                                 | 102   |

| 3.8.2   | Multiplier Alignment                            | 102   |

| 3.8.3   | Other Alignment Circuits                        | 103   |

| СНАРТЕ  | R 4 DISPLAY SECTION                             | 105   |

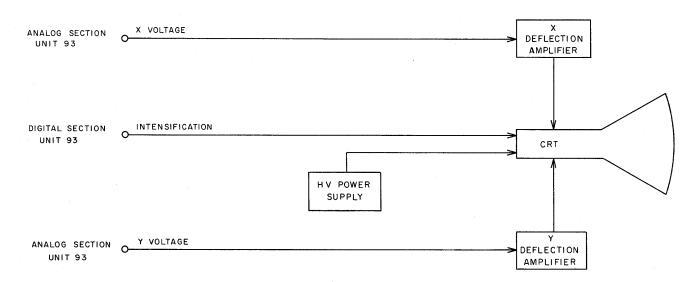

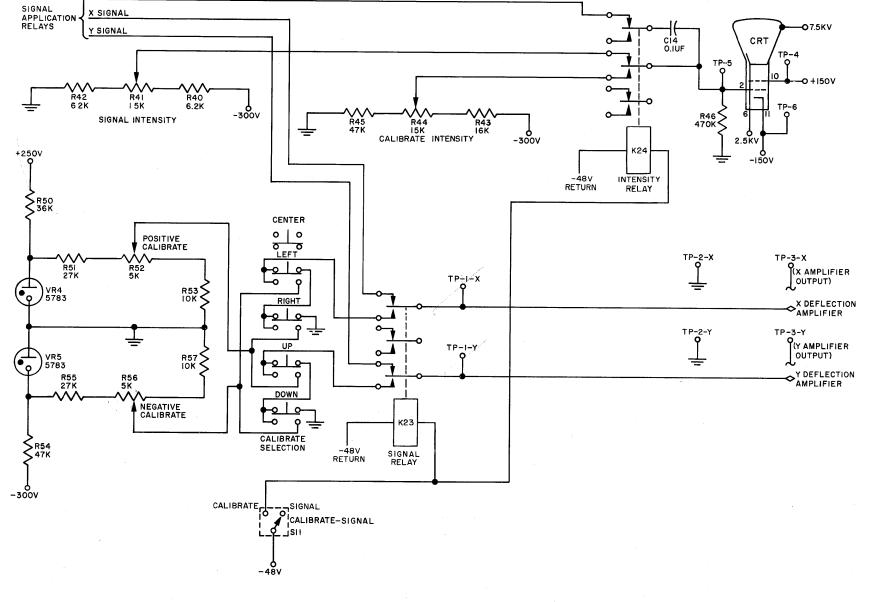

| 4.1     | Operation of CRT Section                        | 105   |

| 4.1.1   | General                                         | 105   |

| 4.1.2   | Cathode-Ray Tube                                | 105   |

| 4.1.3   | Deflection Amplifiers                           | 105   |

| 4.1.4   | High-Voltage Power Supply                       | 105   |

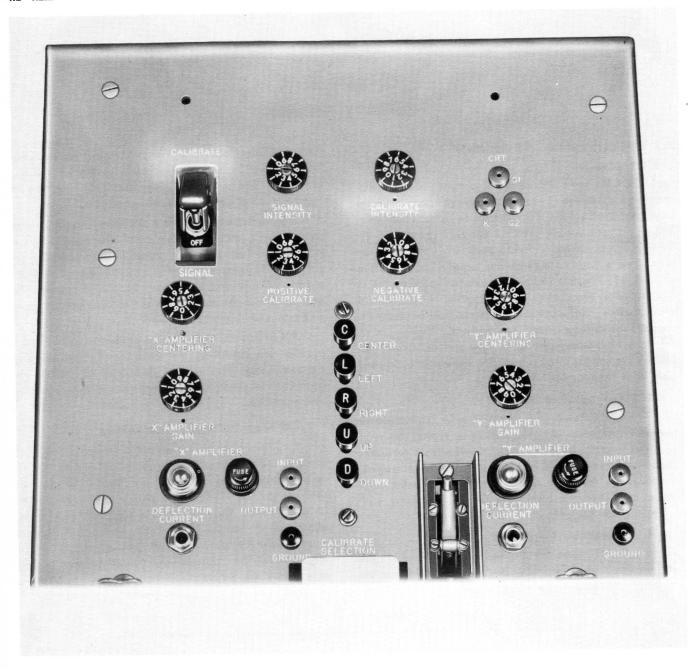

| 4.2     | Calibration                                     | 106   |

| 4.2.1   | General                                         | 106   |

| 4.2.2   | Circuit Switching                               | 106   |

| 4.2.3   | Calibration Voltages                            | 108   |

| 4.2.4   | Calibration Test Points                         | 108   |

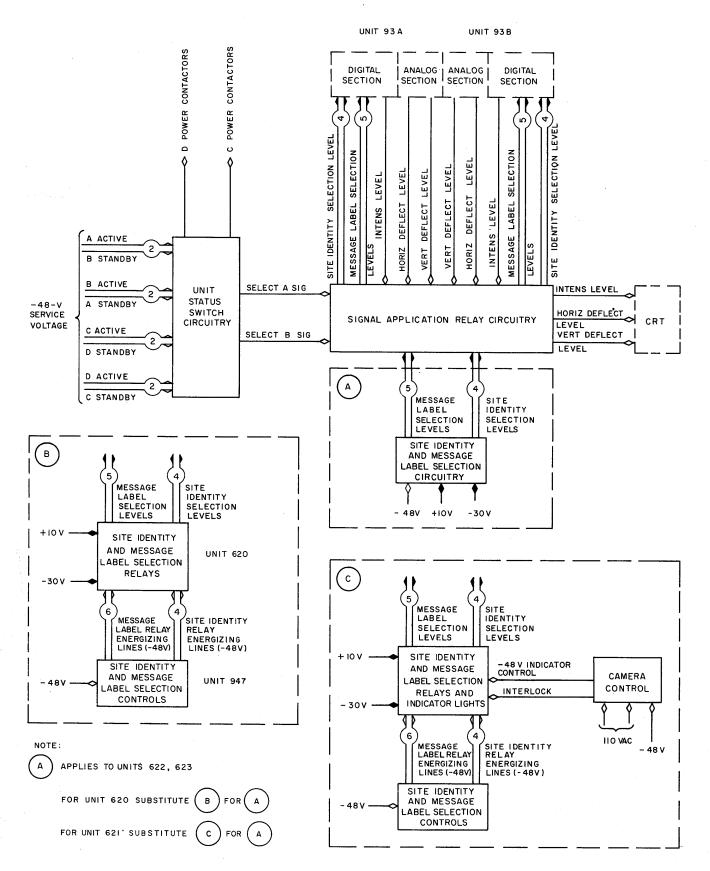

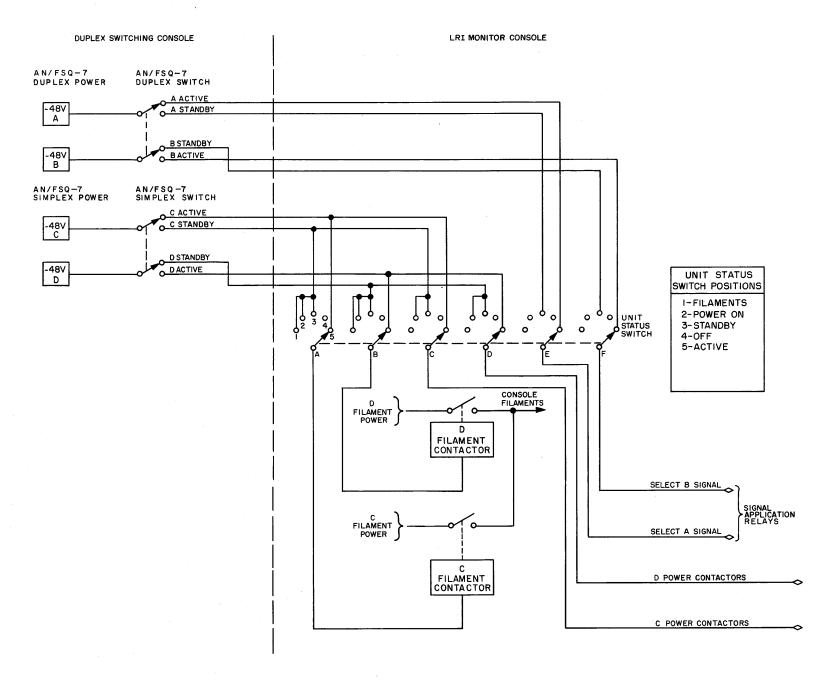

| СНАРТЕ  | R 5 SWITCHING SECTION                           | 109   |

| 5.1     | General                                         | 109   |

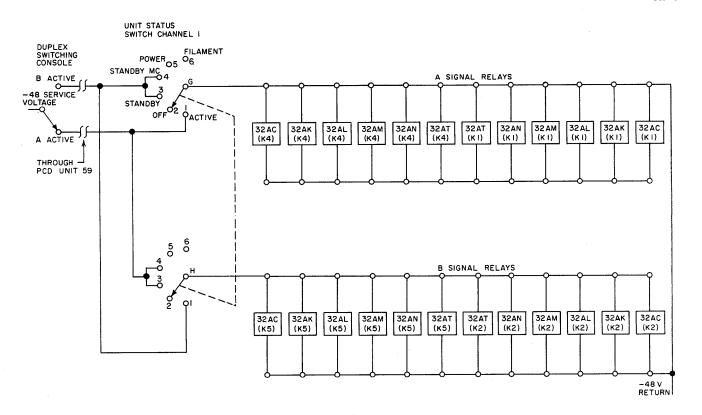

| 5.2     | UNIT STATUS Switch                              | 109   |

| 5.3     | Signal Application Control Relays               | 111   |

| 5.4     | Site Identity and Message Label Selector Switch |       |

|         | and Relay Circuitry                             | 111   |

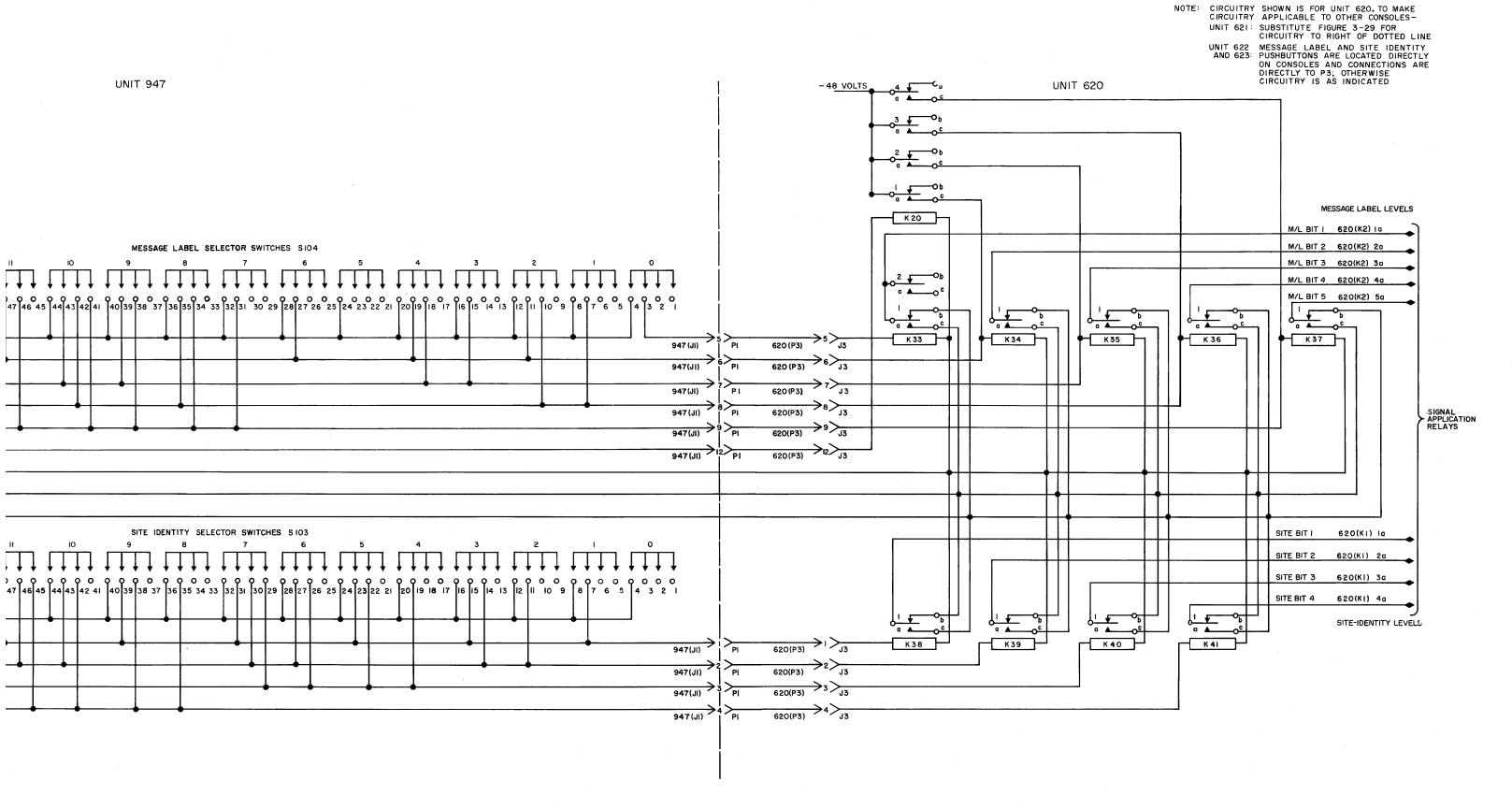

| 5.4.1   | General                                         | 111   |

| 5.4.2   | Message Label Switches and Relays               | 111   |

| 5.4.3   | Site Identity Switches and Relays               | 113   |

| Heading |                                                        | Page |

|---------|--------------------------------------------------------|------|

| 5.4.4   | Site Selection and Message Label Indicators, Unit 621  | 113  |

| 5.4.5   | Film Exposure Interlock, Unit 621                      | 113  |

| 5.5     | Camera Control Circuit                                 | 114  |

| 5.5.1   | General                                                | 114  |

| 5.5.2   | Film Exposure Control                                  | 114  |

| 5.5.2   | .1 Controls and Indicators                             | 114  |

| 5.5.2   | .2 General Description of Circuit Operation            | 114  |

| 5.5.2   | .3 Detailed Description of Circuit Operation           | 114  |

| 5.5.3   | Stop Mechanisms                                        | 115  |

| 5.5.4   | Selection Indicators and Indicator Disconnect Circuit  | 115  |

| 5.5.5   | Film-Advance Circuit                                   | 116  |

| 5.5.6   | Film Alarm Circuit                                     | 116  |

| 5.5.7   | Miscellaneous Circuits                                 | 116  |

| 5.5.7   | .1 Film Interlock                                      | 116  |

| 5.5.7   | .2 EXPOSURE ON Indicator                               | 116  |

|         | 4 GAP-FILLER INPUT ELEMENT                             |      |

| 1.1     | General                                                |      |

| 1.2     | Function of the Gap-Filler Input Element               | 117  |

| 1.3     | Relationship of the GFI Element to Information Sources |      |

| 1.4     | Physical Description                                   | 118  |

| 1.5     | Drum Word Layout and Drum Entry                        | 118  |

| 1.6     | General Functional Description                         | 119  |

| 1.6.1   | Input Switching Section                                | 119  |

| 1.6.2   | Channel Equipment                                      | 119  |

| 1.6.3   | Duplex Switching Section                               | 119  |

| 1.6.4   | Common Equipment                                       | 119  |

| 1.6.5   | GFI Mapper                                             | 121  |

| 1.7     | Simplex Maintenance Console GFI Control Panels         | 121  |

| 1.7.1   | General                                                | 121  |

| 1.7.2   | Function of GFI Control Panel Switches                 | 121  |

| Heading |                                           | Page |

|---------|-------------------------------------------|------|

| СНАРТЕ  | R 2 INPUT SWITCHING                       | 123  |

| 2.1     | General                                   | 123  |

| 2.1.1   | Input Data Switching                      | 123  |

| 2.1.2   | Spare Channel Switching                   | 125  |

| СНАРТЕ  | R 3 GFI CHANNEL INPUT                     | 127  |

| 3.1     | Introduction                              | 127  |

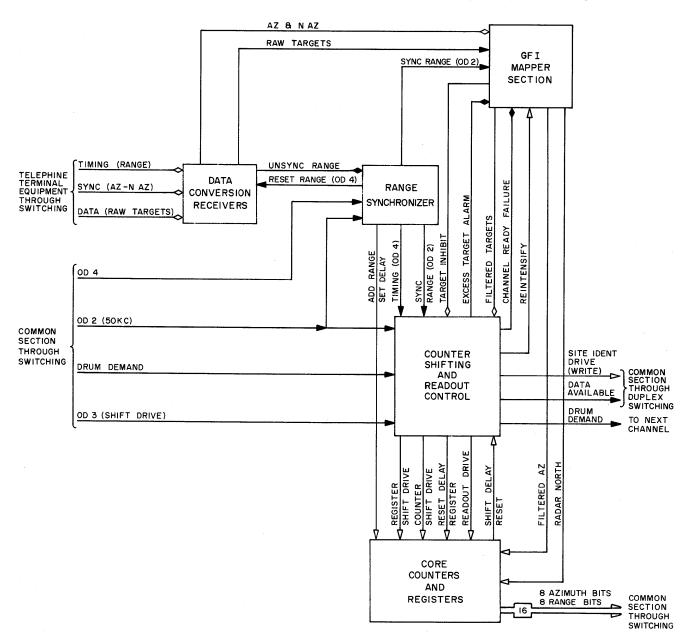

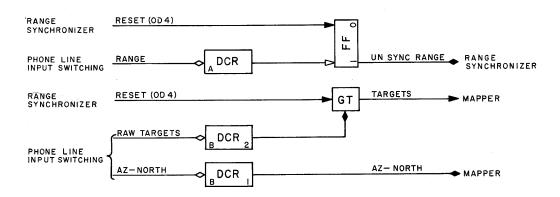

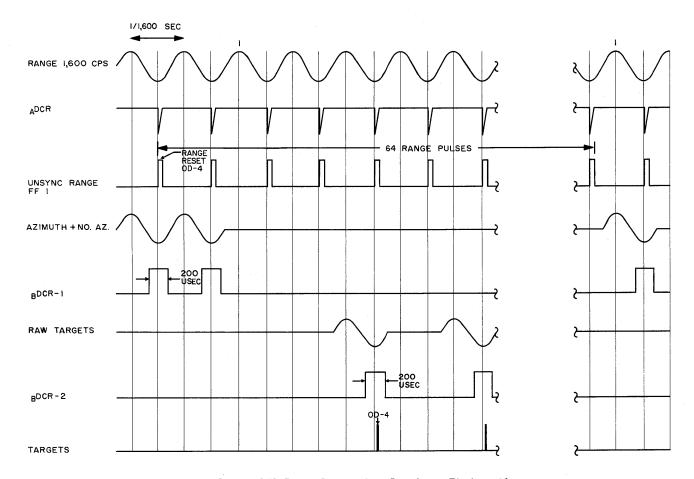

| 3.2     | Data Conversion Receiver Circuit          | 128  |

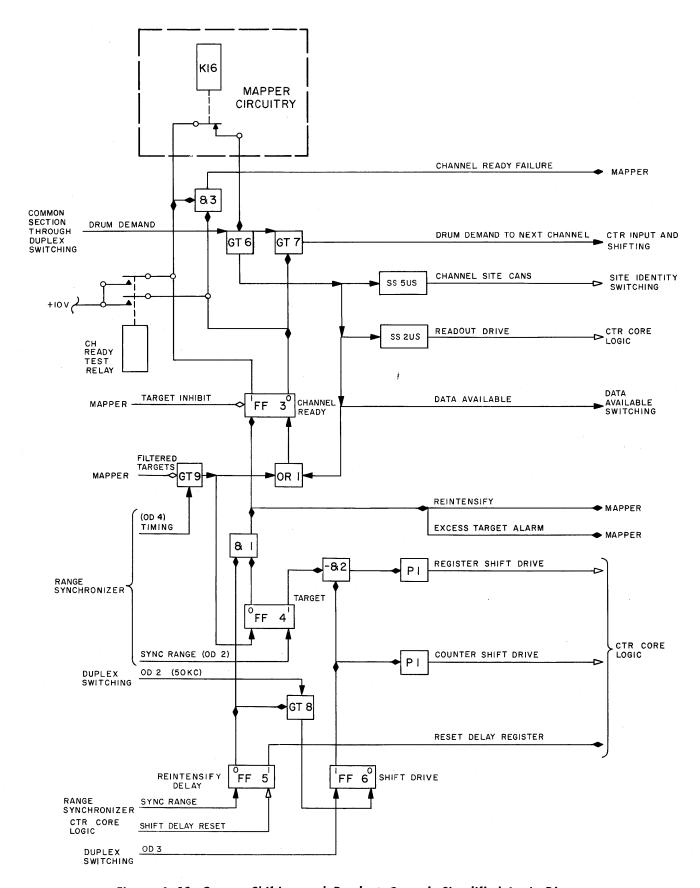

| 3.3     | GFI Mapper Section                        | 128  |

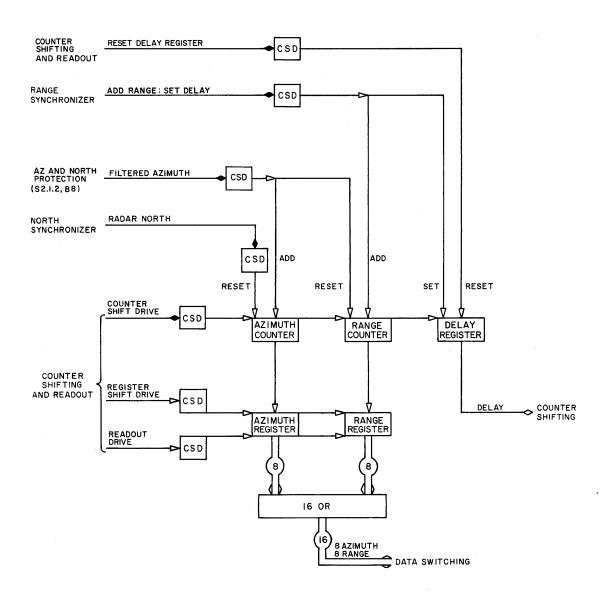

| 3.4     | GFI Counter Section                       | 129  |

| 3.4.1   | General                                   | 129  |

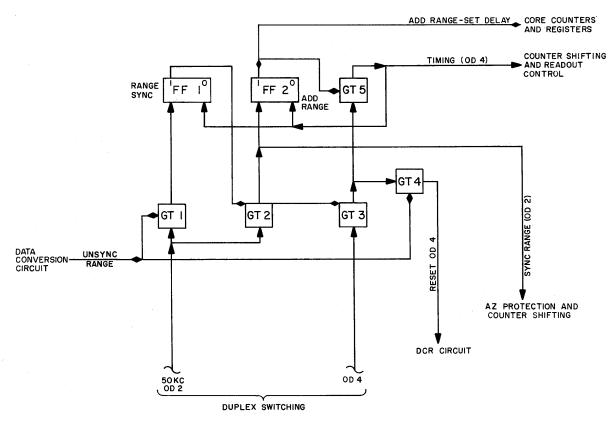

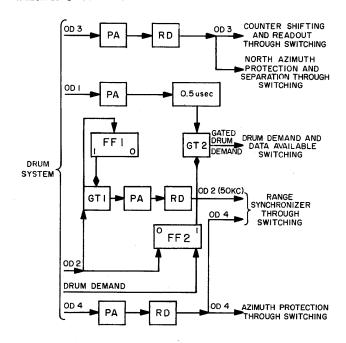

| 3.4.2   | Range Synchronizer                        | 129  |

| 3.4.3   | Counter Shifting and Readout Control      | 130  |

| 3.4.3.1 | Generation of Counter-Shift-Drive Pulses  | 130  |

| 3.4.3.2 | Generation of Register-Shift-Drive Pulses | 132  |

| 3.4.3.3 | Generation of Readout Pulse               | 132  |

| 3.4.4   | Core Counters and Registers               | 133  |

| СНАРТЕ  | R 4 DUPLEX SWITCHING                      | 135  |

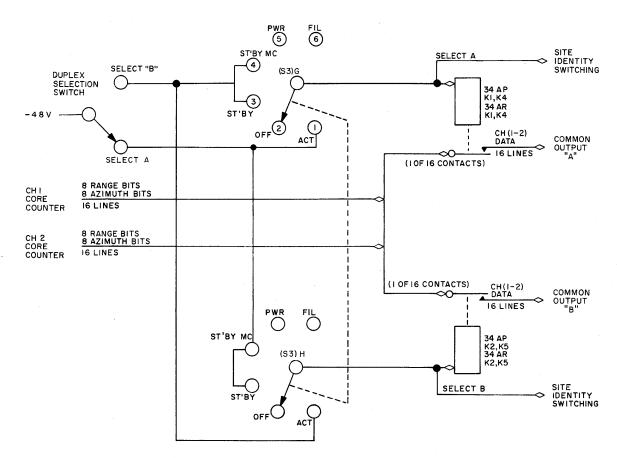

| 4.1     | General                                   | 135  |

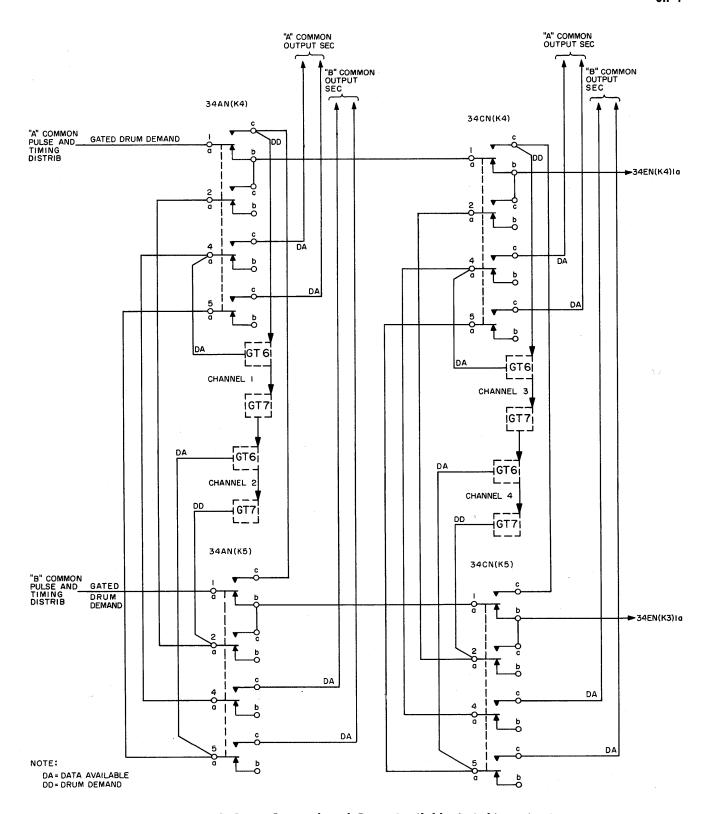

| 4.2     | Drum Demand and Data Available Switching  | 135  |

| 4.3     | Site Identity Switching                   | 137  |

| 4.4     | Site Identity Switching for Spares        | 137  |

| 4.5     | Data Switching to Common A or Common B    | 138  |

| 4.6     | Timing Pulse Switching                    | 139  |

| 4.7     | Site Neon Switching                       | 139  |

| 4.8     | Status Indication Switching               | 140  |

| CHAPTE  | R 5 GFI COMMON SECTION                    | 141  |

| 5.1     | Introduction                              | 141  |

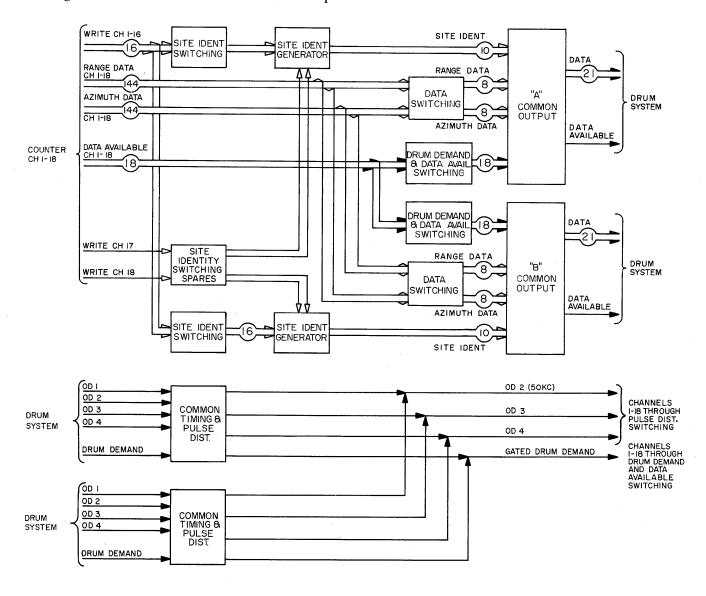

| 5.2     | Common Timing and Pulse Distribution      | 142  |

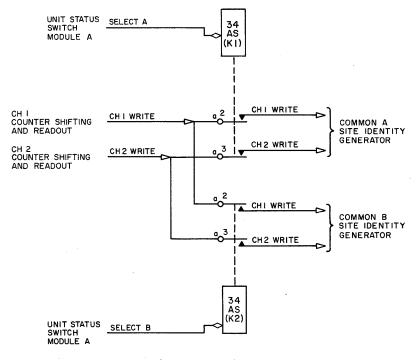

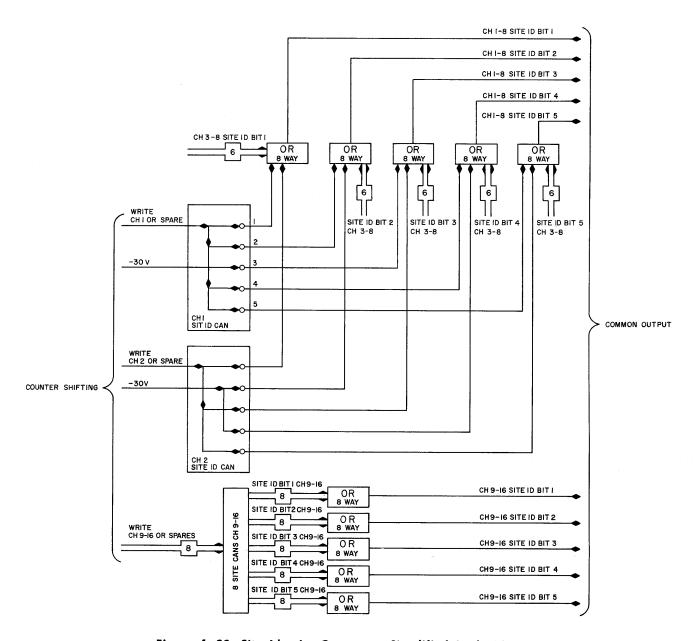

| 5.3     | Site Identity Generator                   | 142  |

| 5.3.1   | Site Identity for Channels 1 through 16   | 143  |

| 5.3.2   | Site Identity for Spare Channels          | 145  |

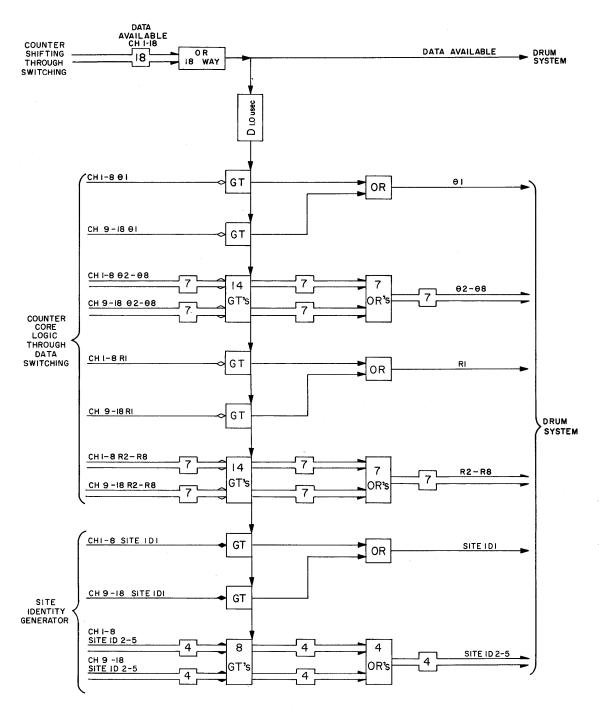

| 5.4     | GFI Common Output                         | 145  |

| Heading |                                              | Page |

|---------|----------------------------------------------|------|

| CHAP    | TER 6 GFI MAPPER SECTION                     | 147  |

| 6.1     | Introduction                                 | 147  |

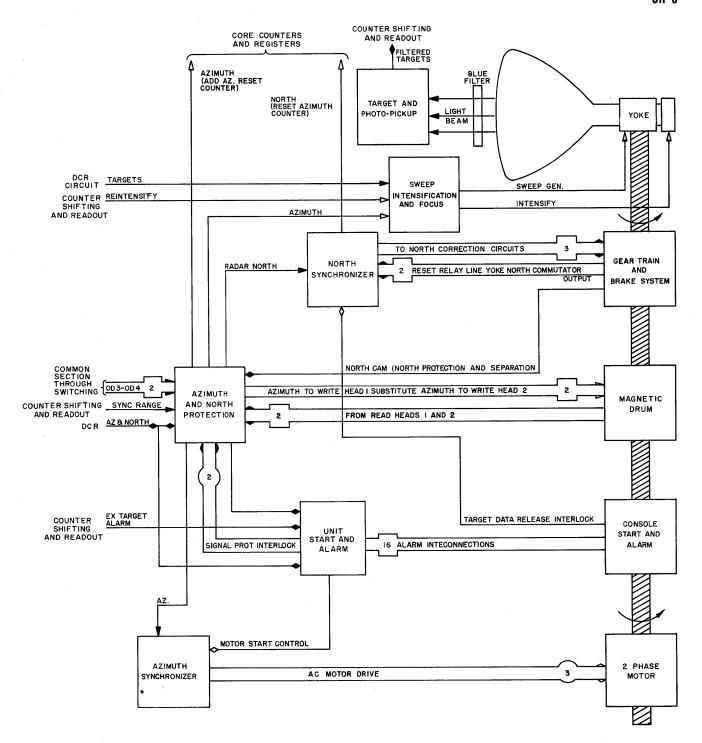

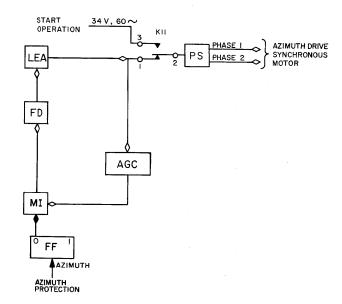

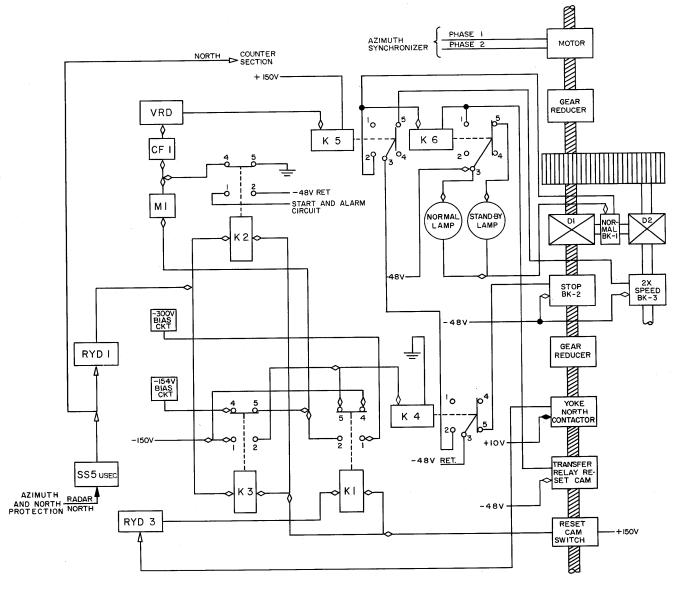

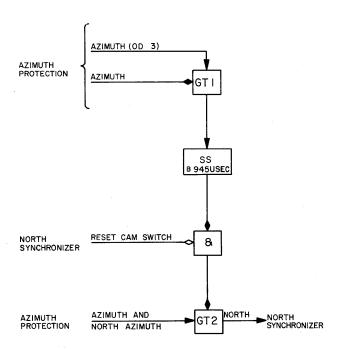

| 6.2     | Azimuth Synchronizer                         | 147  |

| 6.2.1   | General                                      | 147  |

| 6.2.2   | Azimuth Synchronizer, Block Level Discussion | 149  |

| 6.3     | North Synchronizer                           | 149  |

| 6.3.1   | General                                      | 149  |

| 6.3.2   | Yoke Lags Radar Antenna                      | 150  |

| 6.3.3   | Yoke Leads Radar Antenna                     | 151  |

| 6.3.4   | Yoke and Radar Antenna Synchronized          | 151  |

| 6.3.5   | Operation of Relay K6                        | 151  |

| 6.3.6   | Generation of Yoke-North Pulse               | 151  |

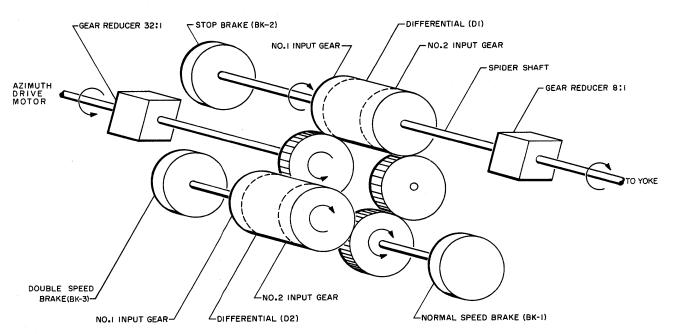

| 6.3.7   | Mechanical Operation of Gear Train           | 152  |

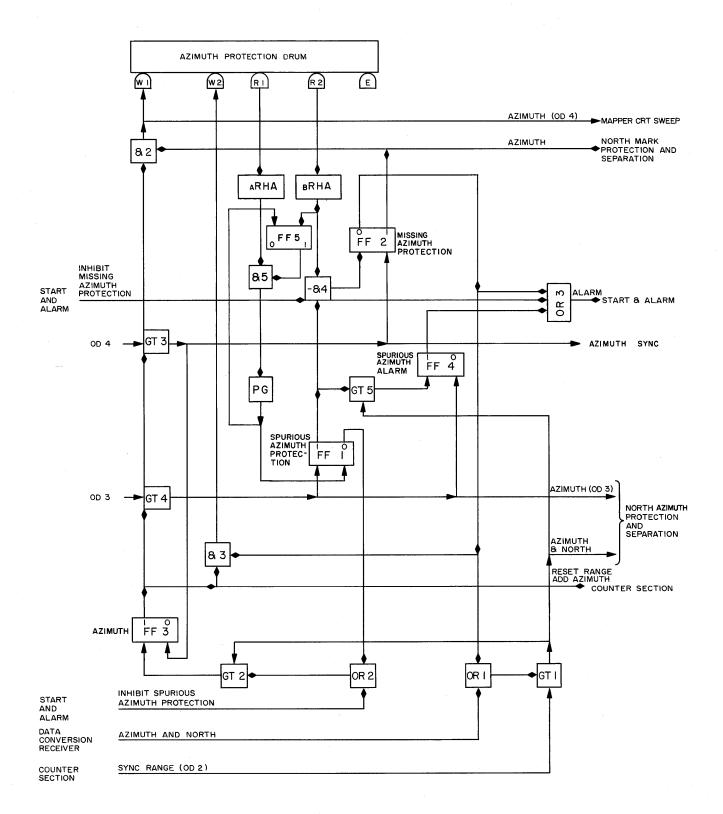

| 6.4     | Azimuth Signal Protection                    | 152  |

| 6.4.1   | General                                      | 152  |

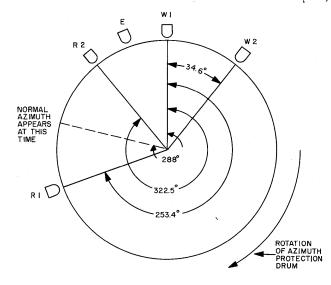

| 6.4.2   | Magnetic Drum                                | 153  |

| 6.4.3   | Protection Against Spurious Azimuth Pulses   | 153  |

| 6.4.4   | Protection Against Missed Azimuth Pulses     | 155  |

| 6.4.5   | North Azimuth Protection and Separation      | 155  |

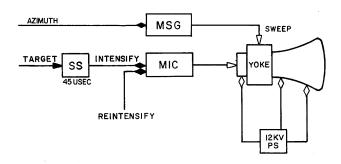

| 6.5     | CRT Operation                                | 156  |

| 6.5.1   | General                                      | 156  |

| 6.5.2   | Radial Sweep                                 | 156  |

| 6.5.3   | Intensification                              | 156  |

| 6.5.4   | Focus                                        | 156  |

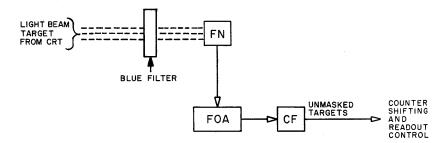

| 6.6     | Photo Pickup                                 | 156  |

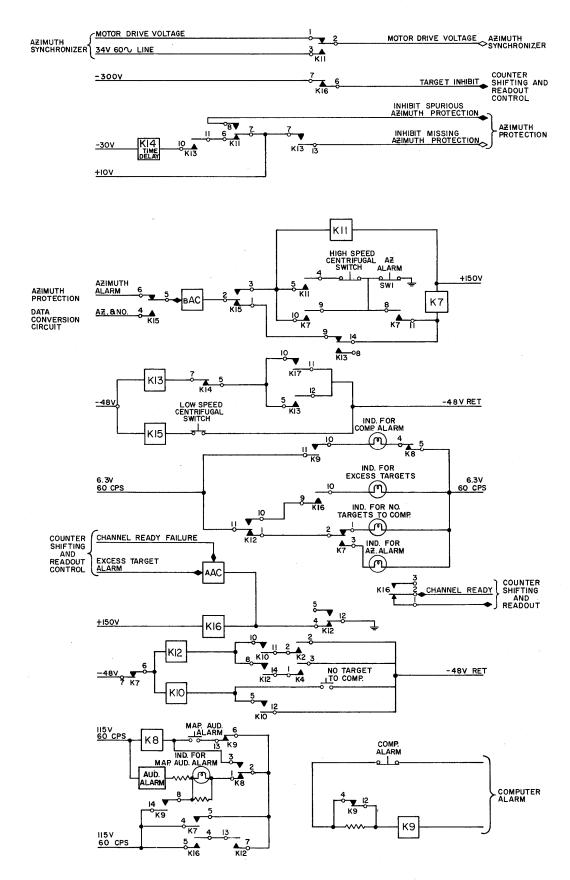

| 6.7     | Start and Alarm Logic                        | 157  |

| 6.7.1   | Start Circuit                                | 157  |

| 6.7.2   | Alarm Circuit                                | 159  |

| PART    | 5 CROSSTELL INPUT ELEMENT                    | 161  |

| CHAP    | TER 1 INTRODUCTION                           | 161  |

| 1.1     | General                                      |      |

| 1.2     | Function of XTI Input Flement                | 161  |

| Head | ding    |                                                     | Page |

|------|---------|-----------------------------------------------------|------|

|      | 1.3     | Relationship of XTL Element to Information Sources  | 161  |

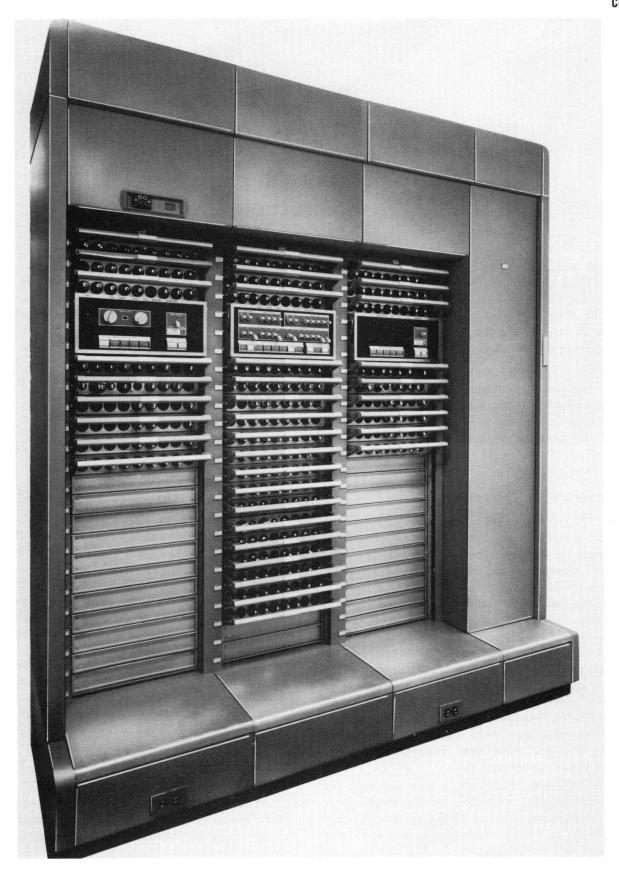

|      | 1.4     | Physical Description                                | 162  |

|      | 1.4.1   | Twenty-Four-Channel Installation                    | 162  |

|      | 1.4.2   | Twelve-Channel Installation                         | 162  |

|      | 1.5     | Message Layout                                      | 162  |

|      | 1.6     | General Functional Description                      | 162  |

|      | 1.6.1   | Twenty-Four-Channel Installation                    | 162  |

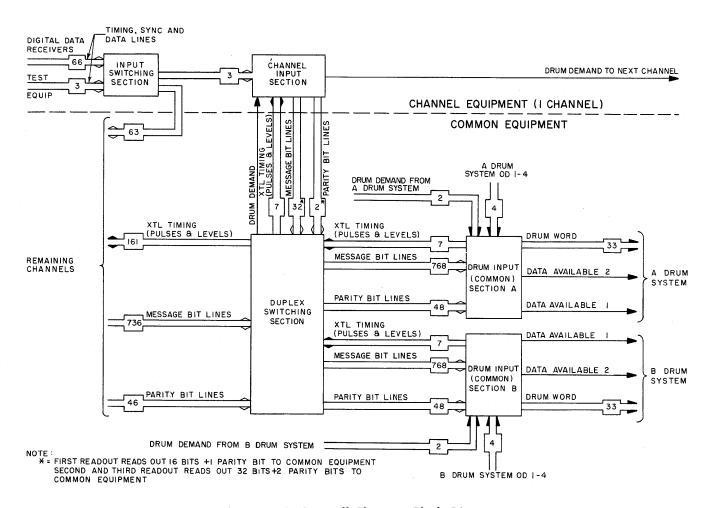

|      | 1.6.1.1 | Input Switching                                     | 163  |

|      | 1.6.1.2 | Channel Input Section                               | 163  |

|      | 1.6.1.3 | Duplex Switching Section                            | 163  |

|      | 1.6.1.4 | Drum Input (Common) Section                         | 164  |

|      | 1.6.2   | Twelve-Channel Installation                         | 164  |

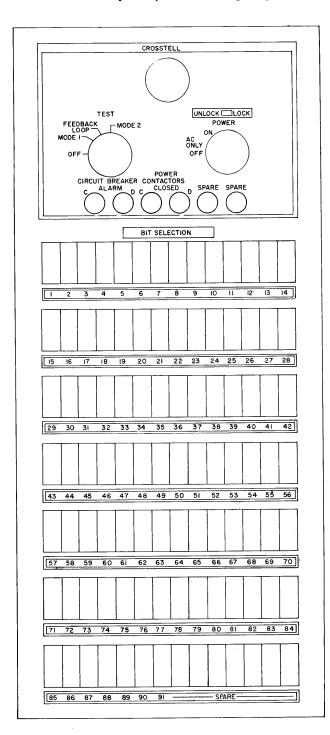

|      | 1.7     | Simplex Maintenance Console XTL Control Panels      | 164  |

|      | 1.7.1   | General                                             | 164  |

|      | 1.7.2   | Function of XTL Control Panel Switches              | 164  |

| C    | HAPTER  | 2 INPUT SWITCHING                                   | 167  |

|      | 2.1     | General                                             | 167  |

|      | 2.2     | Input Data Switching                                | 167  |

|      | 2.3     | Spare Channel Switching                             | 167  |

|      | 2.3.1   | General                                             | 167  |

|      | 2.3.2   | Alternate Telephone Line Switching                  | 168  |

|      | 2.3.3   | Switching of Basic Telephone-Terminal Indications   | 168  |

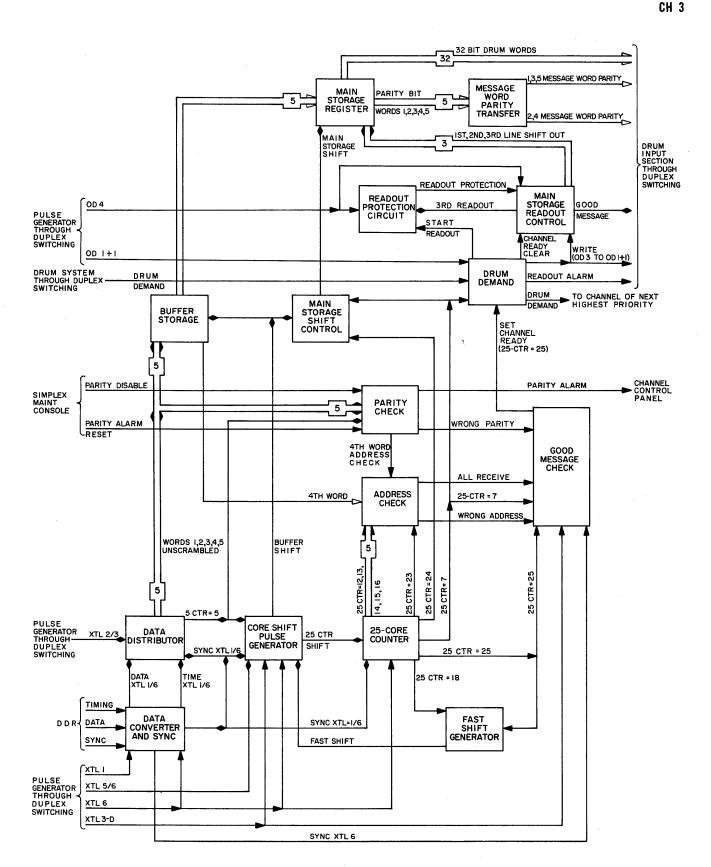

| C    | HAPTER  | 3 CROSSTELL CHANNEL INPUT SECTION                   | 171  |

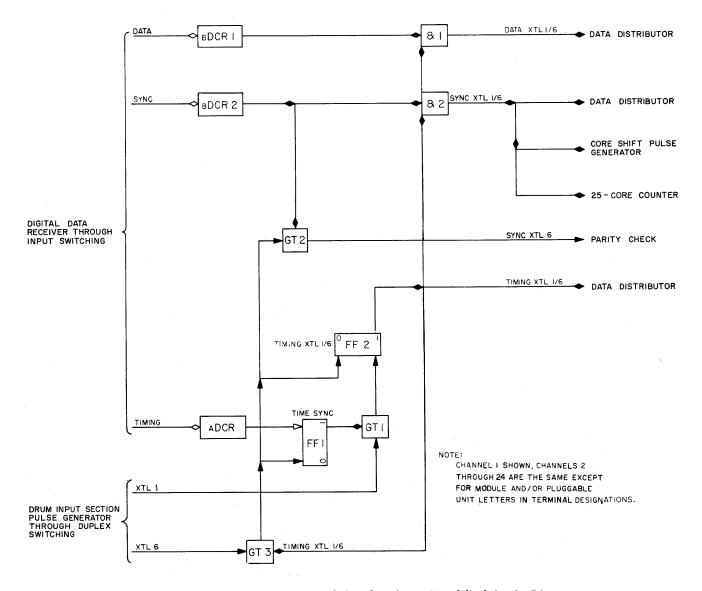

|      | 3.1     | Introduction                                        | 171  |

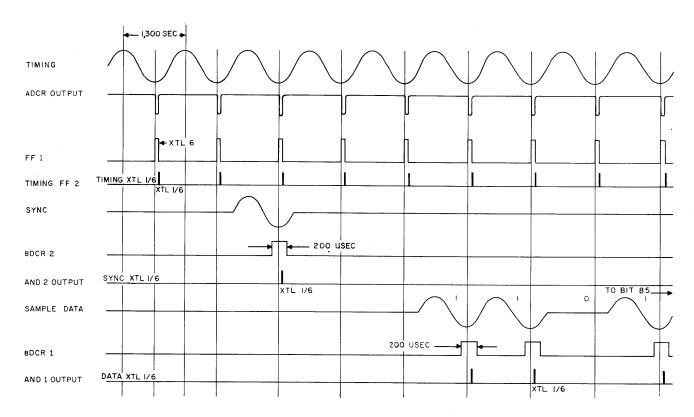

|      | 3.2     | Data Converter and Synchronizer                     | 173  |

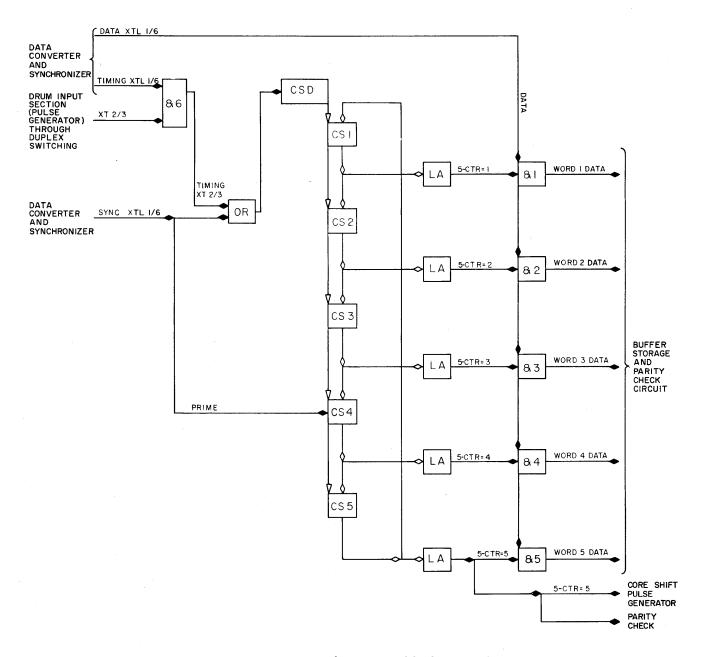

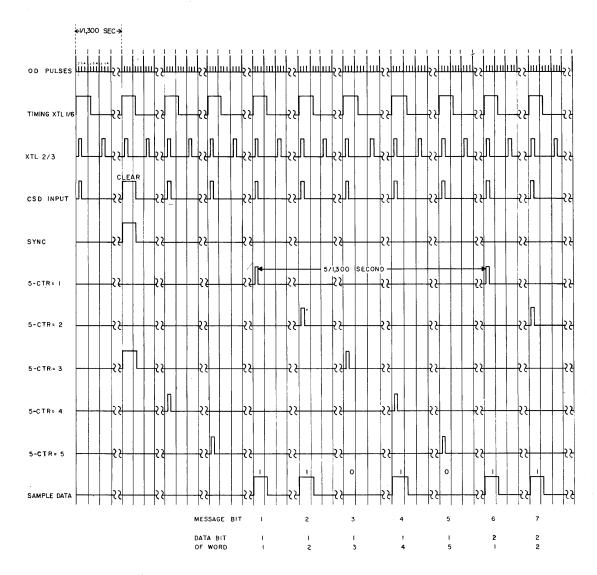

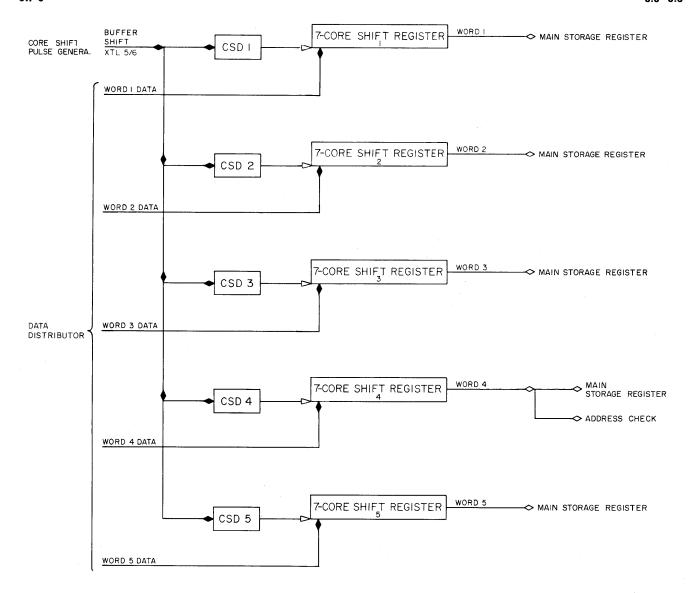

|      | 3.3     | Data Distributor                                    | 175  |

|      | 3.4     | Buffer Storage Registers                            | 177  |

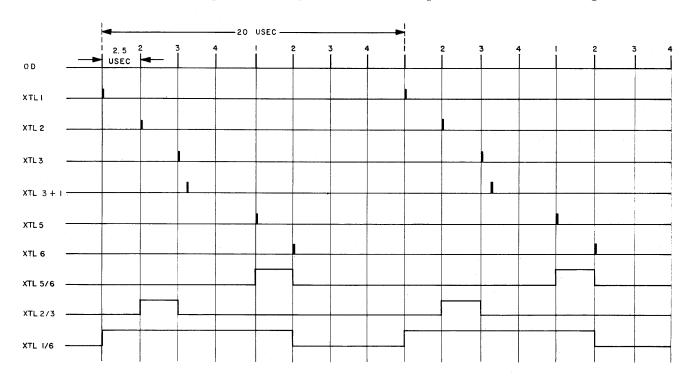

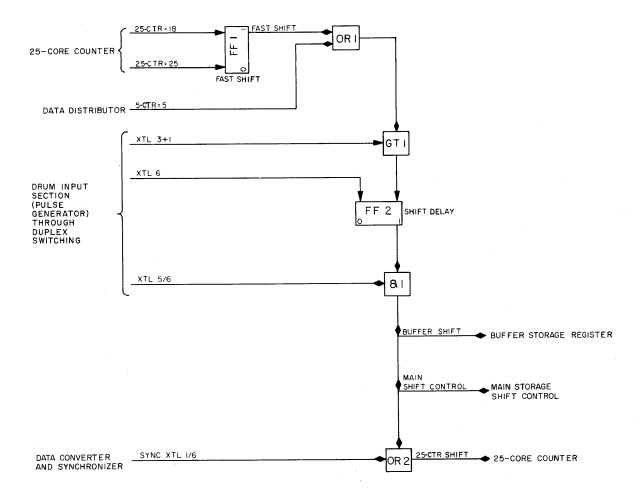

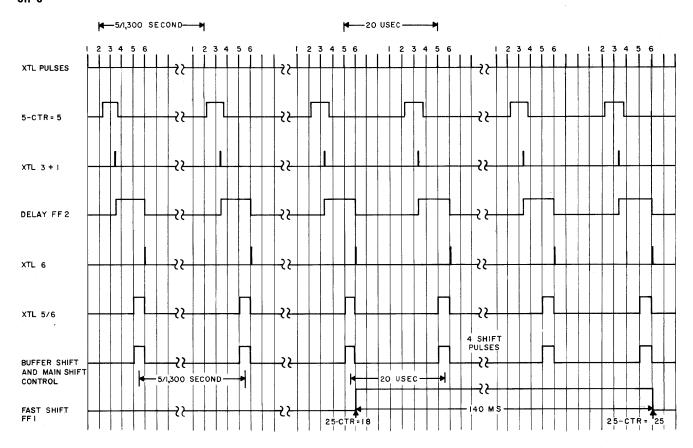

|      | 3.5     | Core Shift Pulse Generator and Fast-Shift Generator | 177  |

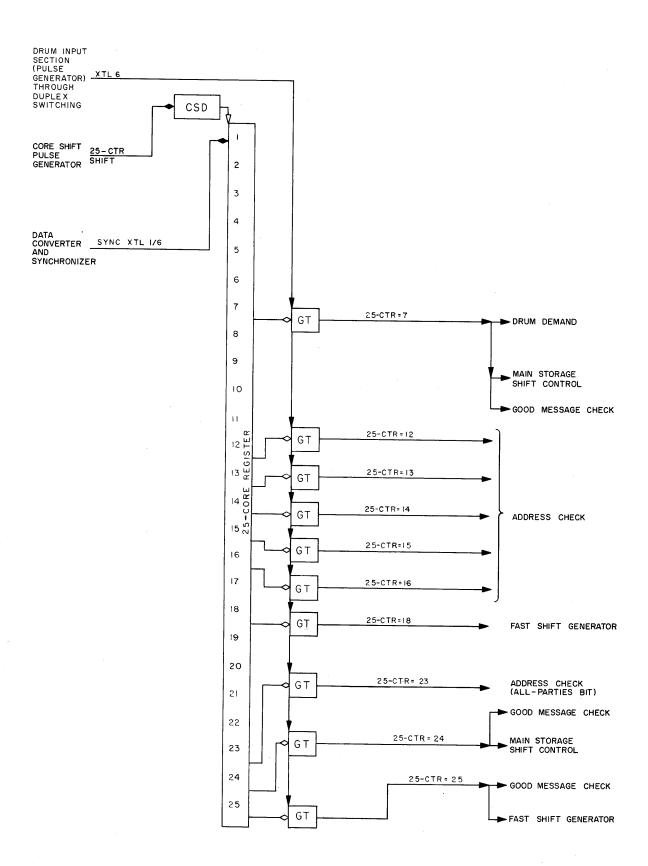

|      | 3.6     | The 25-Core Counter                                 | 179  |

|      | 3.7     | Main Storage                                        | 181  |

|      | 3.7.1   | General                                             | 181  |

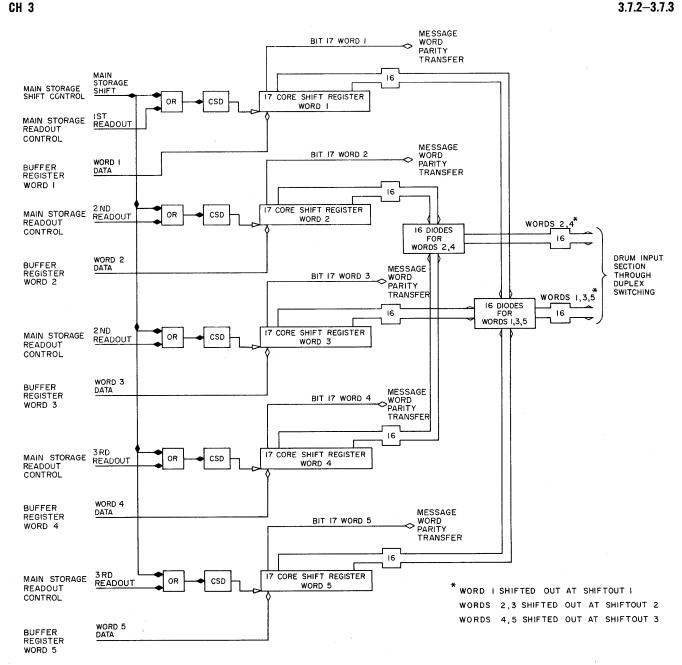

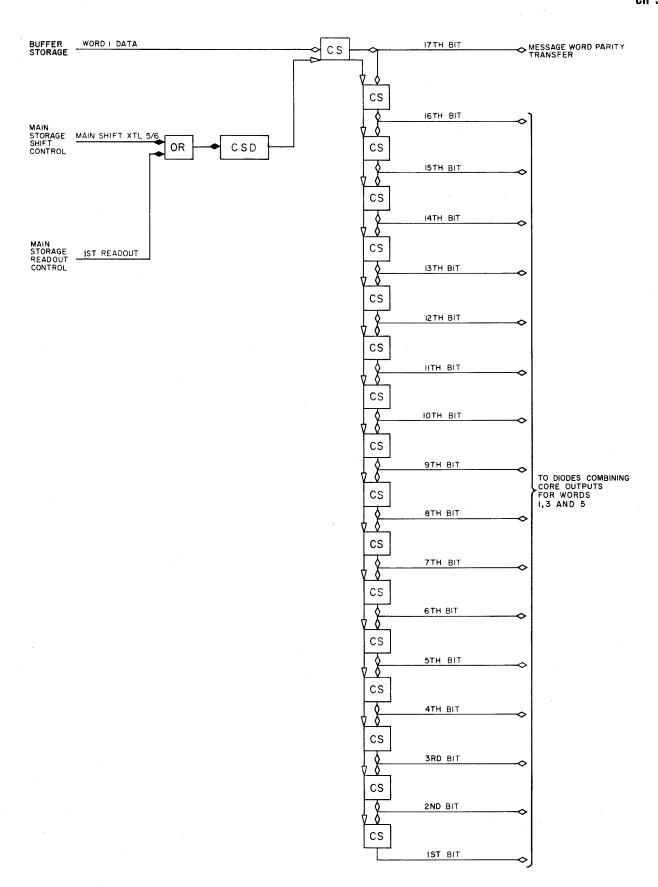

|      | 3.7.2   | Word Storage                                        | 181  |

|      | 3.7.3   | Word Readout                                        | 183  |

| Heading     |                                                                       | Page |

|-------------|-----------------------------------------------------------------------|------|

| 3.7.4       | Diode Isolating Circuits                                              | 185  |

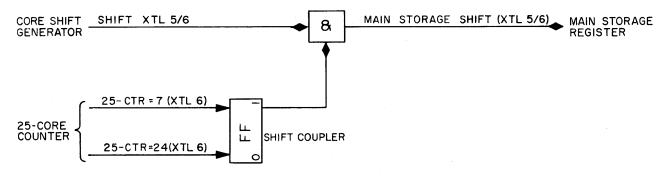

| 3.8         | Main Storage Shift Control                                            | 185  |

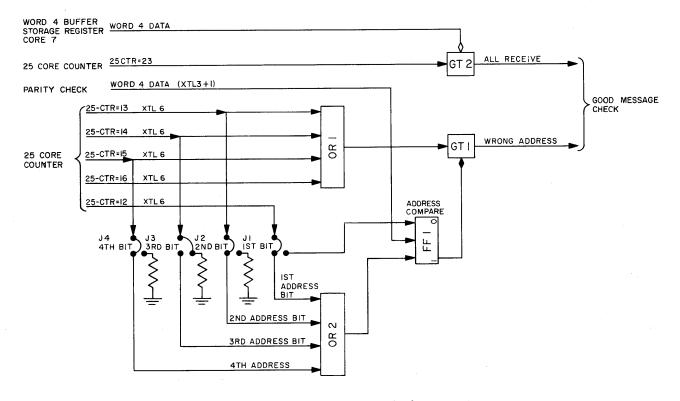

| 3.9         | Address Check                                                         | 185  |

| 3.9.1       | Address Checking                                                      | 185  |

| 3.9.2       | All-Receive                                                           | 186  |

| 3.10        | Parity Check                                                          | 186  |

| 3.11        | Good Message Check                                                    | 189  |

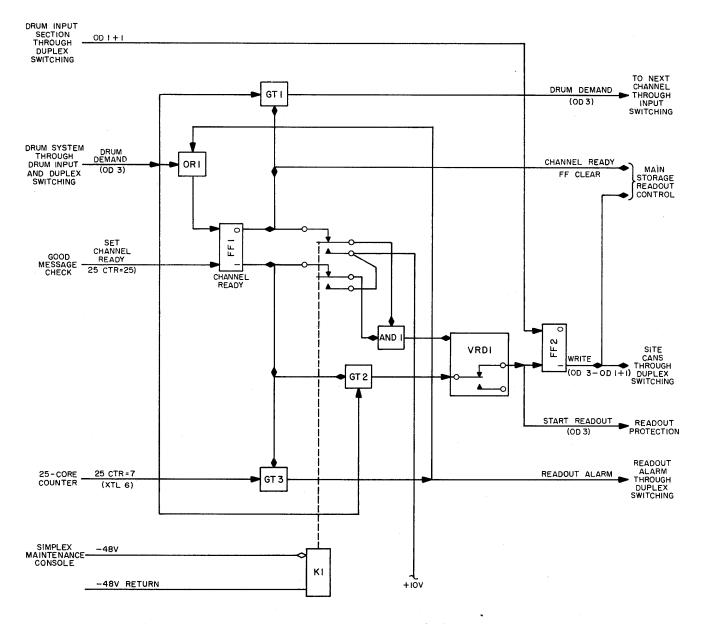

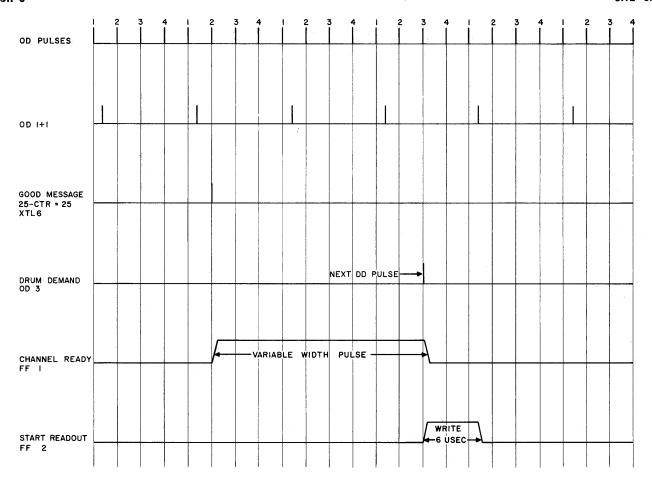

| 3.12        | Drum Demand                                                           | 190  |

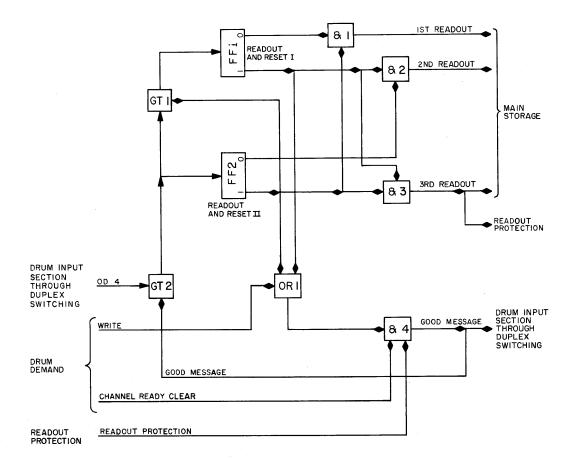

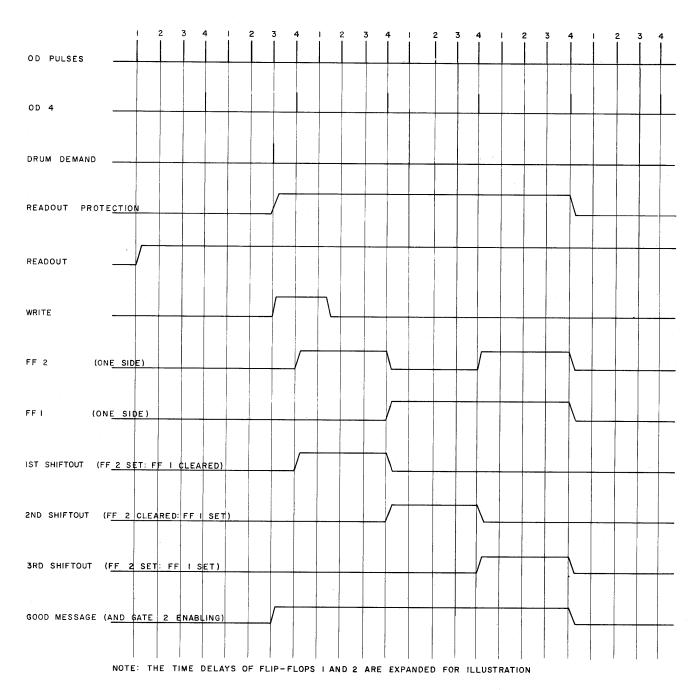

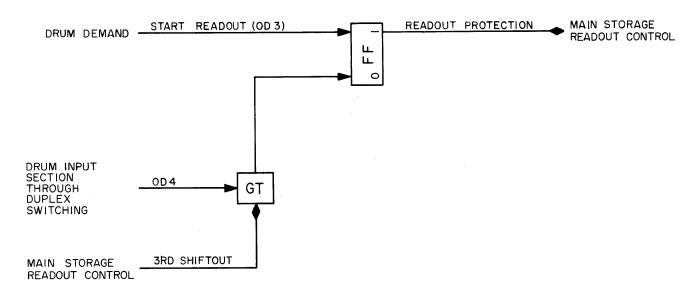

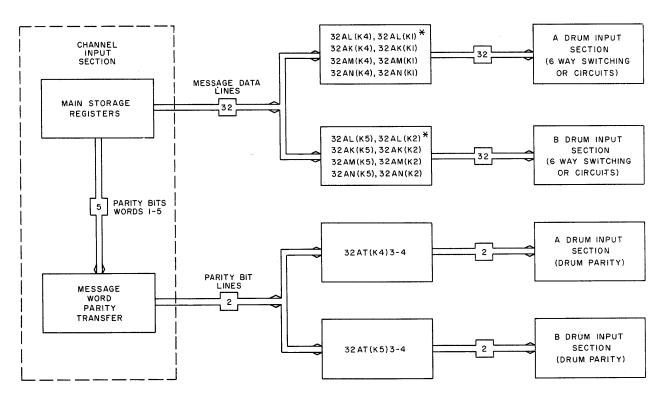

| 3.13        | Main Storage Readout Control                                          | 191  |

| 3.14        | Readout Protection                                                    | 193  |

| 3.15        | Message Word Parity Transfer                                          | 194  |

| CHAPTER     | 4 DUPLEX SWITCHING                                                    | 195  |

| 4.1         | General                                                               | 195  |

| 4.2         | Driving of A and B Signal Relays                                      | 195  |

| 4.3         | Core Data Switching Circuit                                           | 195  |

| 4.4         | Write Level Switching                                                 | 197  |

| 4.5         | Site Neon Indication Switching                                        | 198  |

| 4.6         | Good-Message Level and Readout Alarm Switching                        | 198  |

| <b>4.</b> 7 | Drum Demand Switching                                                 | 199  |

| 4.8         | OD Pulse and XTL Pulse and Level Switching                            | 201  |

| 4.9         | Status Indication Switching                                           | 201  |

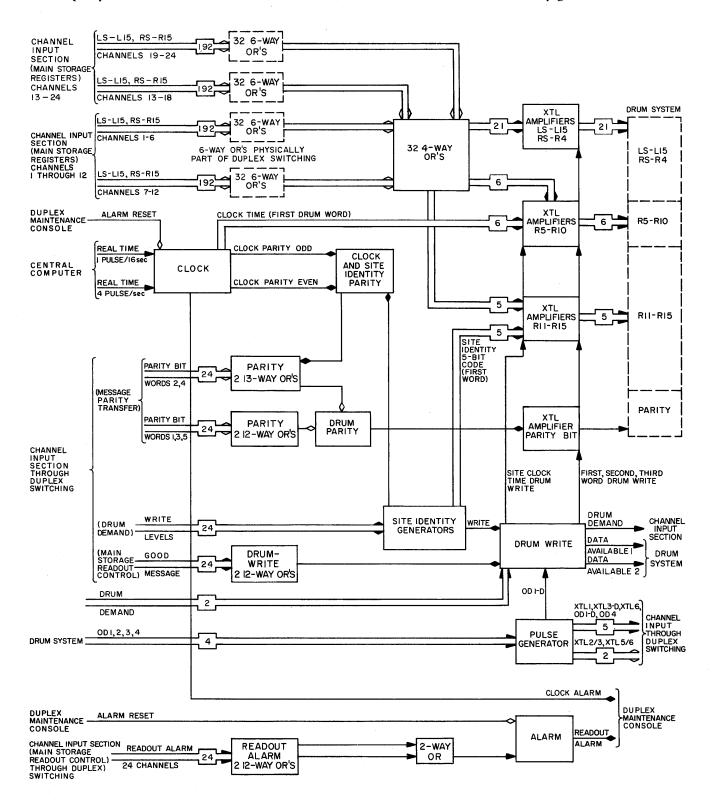

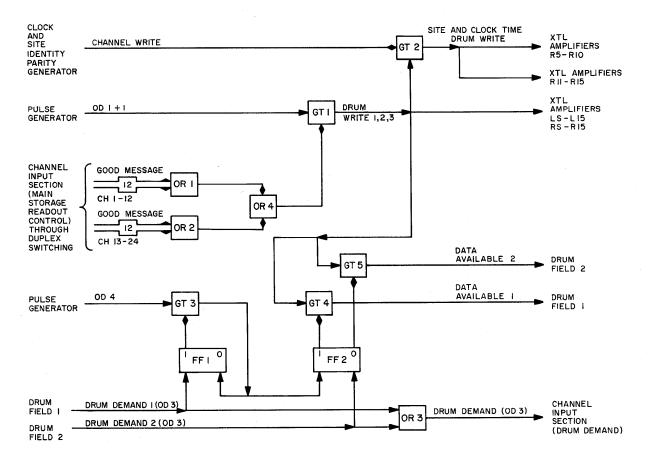

| CHAPTER     | 5 CROSSTELL DRUM INPUT (COMMON) SECTION                               | 203  |

| 5.1         | Introduction                                                          | 203  |

| 5.2         | Block Diagram Analysis of Drum Input Section                          | 203  |

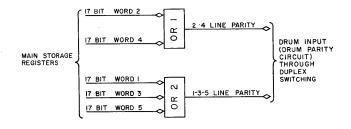

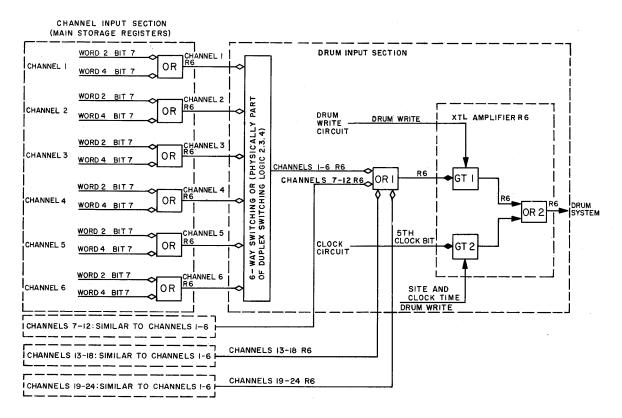

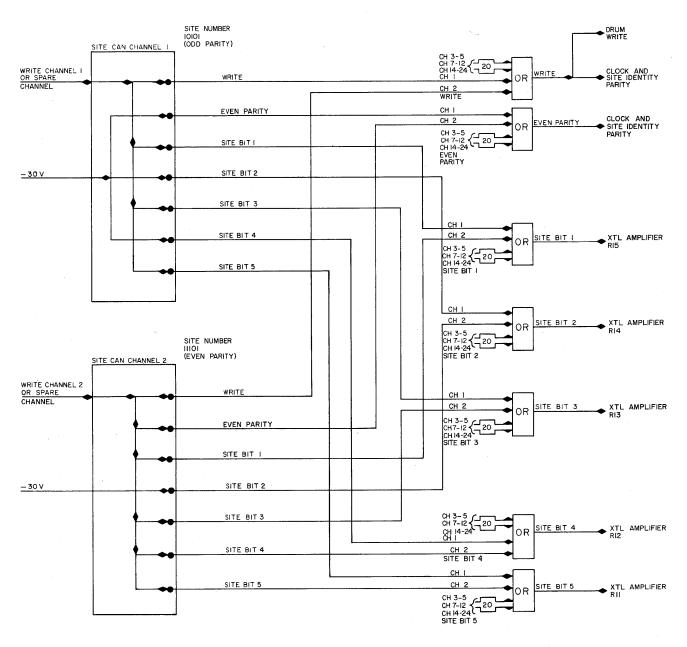

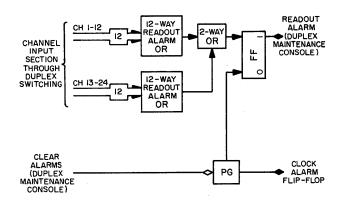

| 5.2.1       | Consolidation of Output Lines of 24 Channels                          | 203  |

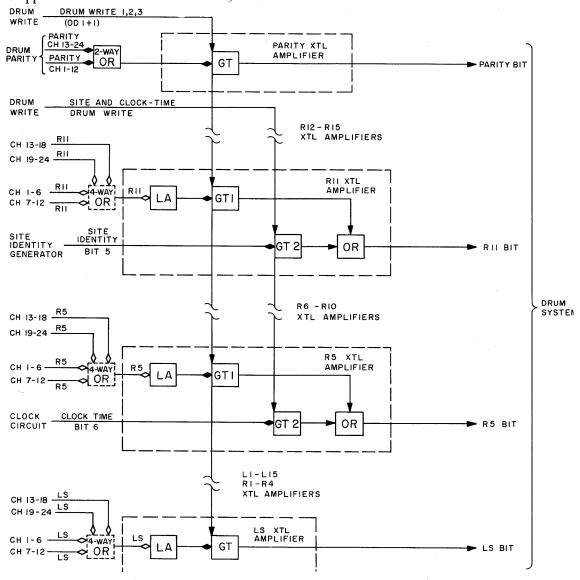

| 5.2.2       | Addition of Clock Time, Site Identity, and Drum Parity to the Message | 205  |

| 5.2.3       | Transfer of Message to Drum System                                    | 205  |

| 5.2.4       | Generation of XTL Timing Pulses and Levels                            | 205  |

| 5.2.5       | Alarm Indications                                                     | 205  |

| 5.2.6       | Generation of Data-Available Pulse                                    | 207  |

| 5.3         | Message Bit OR Circuits                                               | 207  |

| Heading |                                           | Page |

|---------|-------------------------------------------|------|

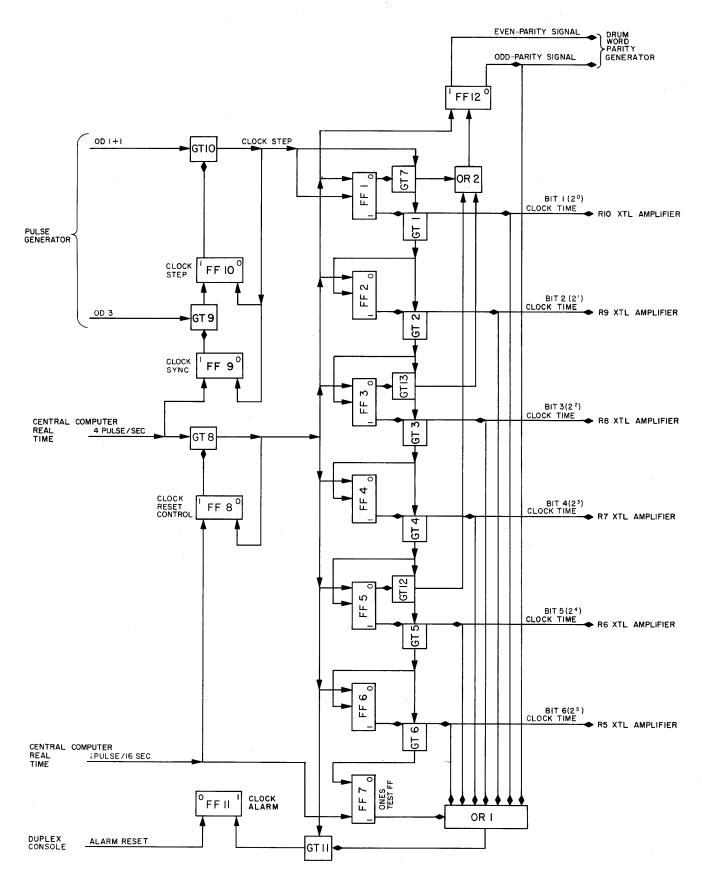

| 5.4     | Clock Circuit                             | 207  |

| 5.4.1   | General                                   | 207  |

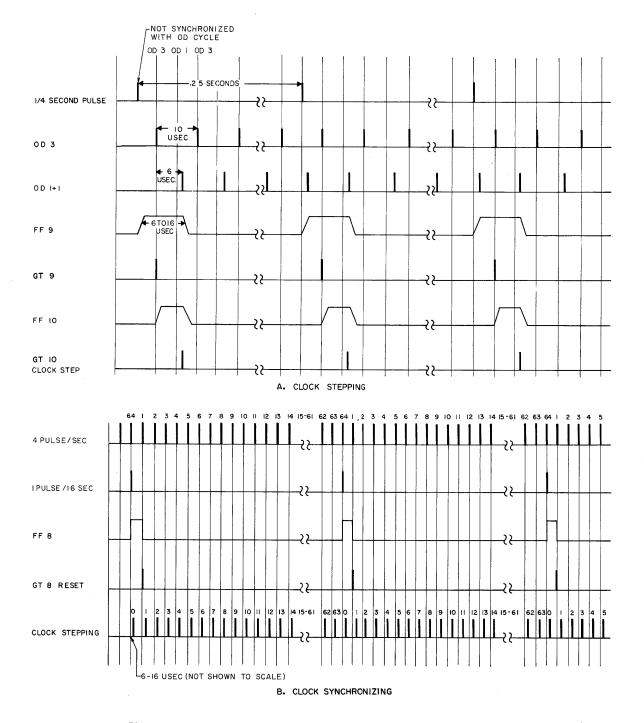

| 5.4.2   | Clock Stepping and Synchronizing          | 207  |

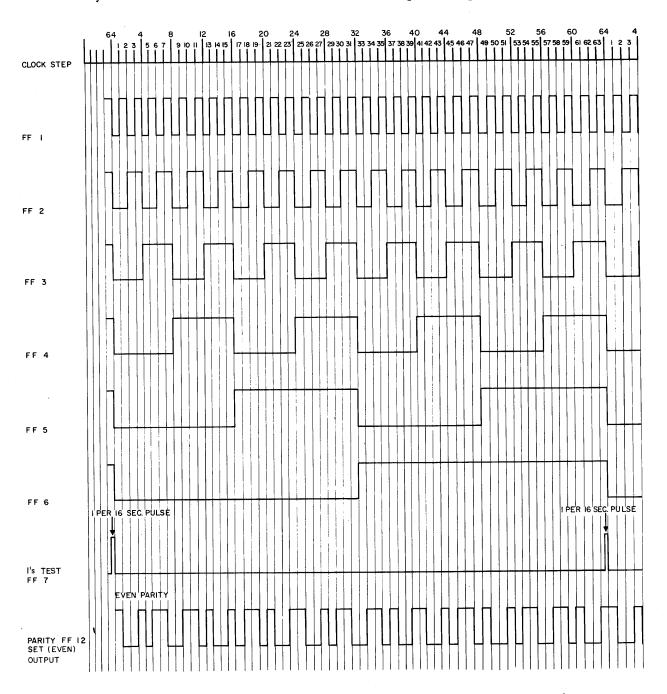

| 5.4.3   | Clock Indication (6-Stage Binary Counter) | 209  |

| 5.4.4   | Clock Parity Generator                    | 210  |

| 5.4.5   | Clock Test                                | 211  |

| 5.5     | Site Identity Generator                   | 211  |

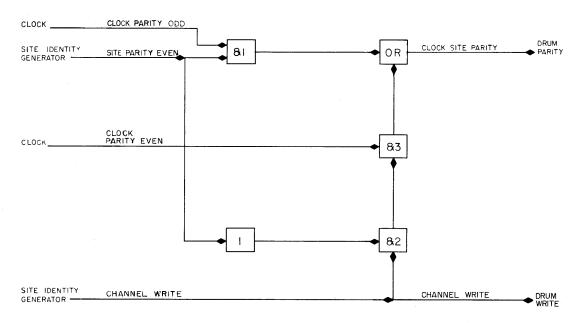

| 5.6     | Clock and Site Identity Parity            | 212  |

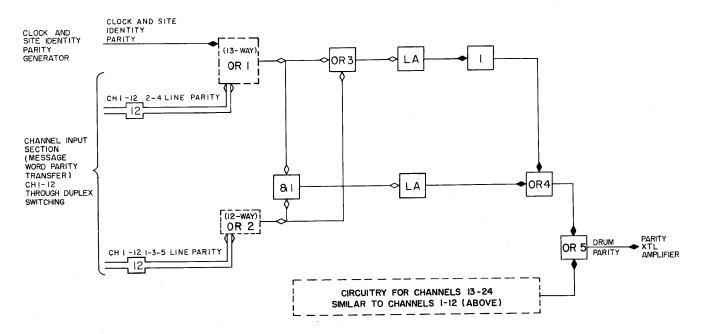

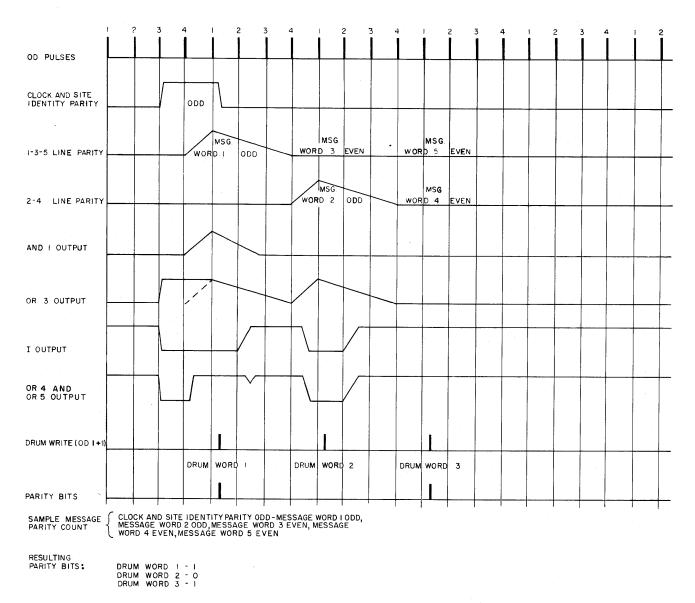

| 5.7     | Drum Parity                               | 213  |

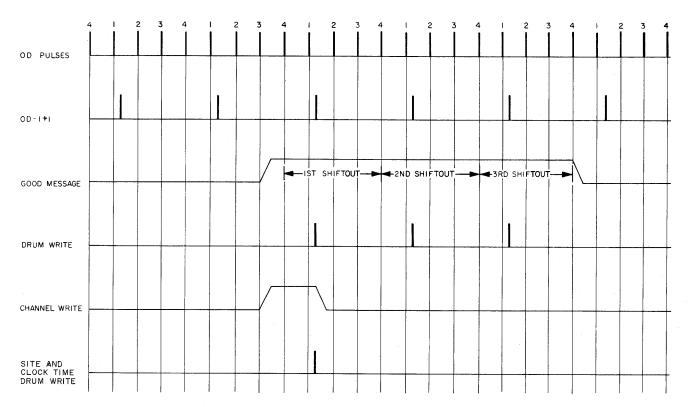

| 5.8     | Drum Write                                | 216  |

| 5.9     | XTL Amplifiers                            | 217  |

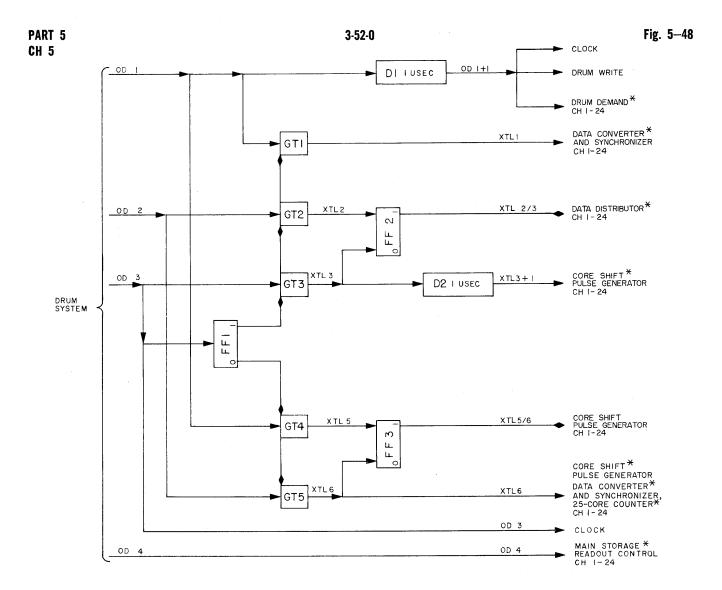

| 5.10    | Pulse Generator                           | 218  |

| 5.11    | Readout Alarm                             | 221  |

| PART A  | A TEST DATTEDNI CENEDATOD TS 000 /FS0     | 222  |

| PARI    | 5 TEST PATTERN GENERATOR TS-923/FSQ       | 223  |

| CHAPTI  | ER 1 INTRODUCTION                         | 223  |

| 1.1     | Scope                                     | 223  |

| 1.2     | Purpose of Equipment                      | 223  |

| 1.2.1   | General                                   | 223  |

| 1.2.2   | LRI TPG                                   | 223  |

| 1.2.3   | XTL TPG                                   | 223  |

| 1.2.4   | GFI TPG                                   | 223  |

| 1.3     | Physical Description                      | 223  |

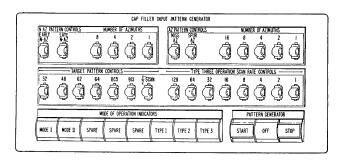

| 1.3.1   | General                                   | 223  |

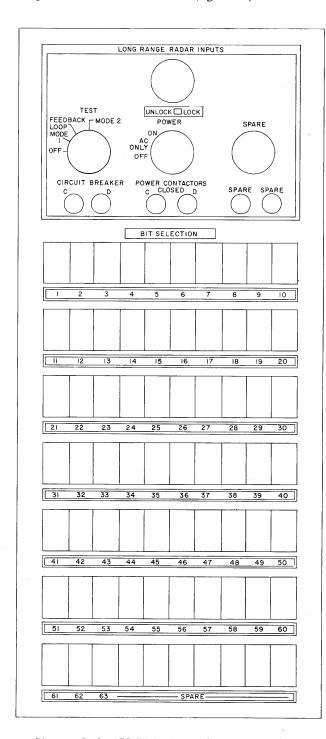

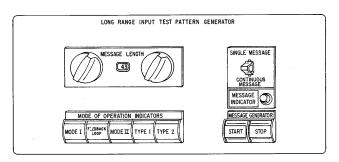

| 1.3.2   | LRI TPG Controls                          | 225  |

| 1.3.3   | XTL TPG Controls                          | 225  |

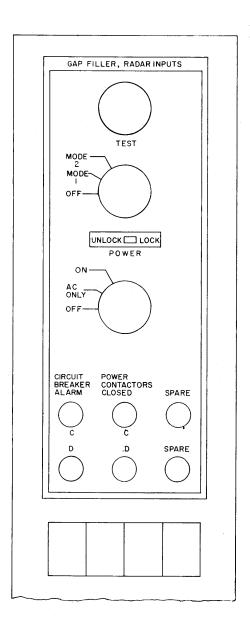

| 1.3.4   | GFI TPG Controls                          | 225  |

| 1.4     | General Functional Description            | 225  |

| 1.5     | Modes of Operation                        | 226  |

| 1.5.1   | General                                   | 226  |

| 1.5.2   | Mode I                                    | 227  |

| 1.5.3   | Mode II                                   | 228  |

| 1.5.4   | Feedback Loop                             | 228  |

| Heading |                                                  | Page |

|---------|--------------------------------------------------|------|

| 1.5.5   | Mode Controls and Indicators                     | 228  |

| 1.6     | Power                                            | 228  |

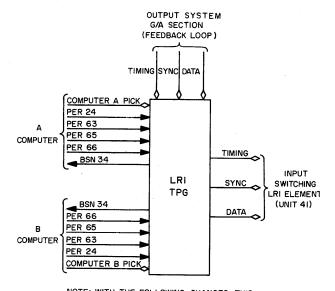

| CHAPTER | 2 LRI TEST PATTERN GENERATOR                     | 229  |

| 2.1     | General                                          | 229  |

| 2.2     | Signal Composition                               | 229  |

| 2.3     | Modes of Operation                               | 229  |

| 2.3.1   | Mode I Operation                                 | 229  |

| 2.3.2   | Mode II Operation                                | 229  |

| 2.3.3   | Feedback Loop Operation                          | 229  |

| 2.4     | Theory of Operation on the Section Diagram Level | 229  |

| 2.4.1   | General                                          | 229  |

| 2.4.2   | Signal Generation Function                       | 230  |

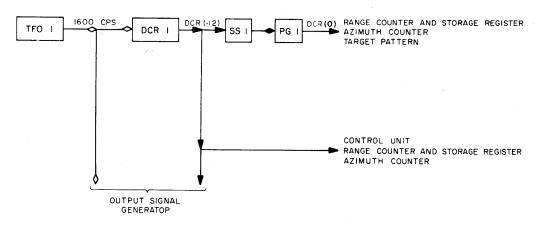

| 2.4.2.1 | TFO and Pulse Generator                          | 230  |

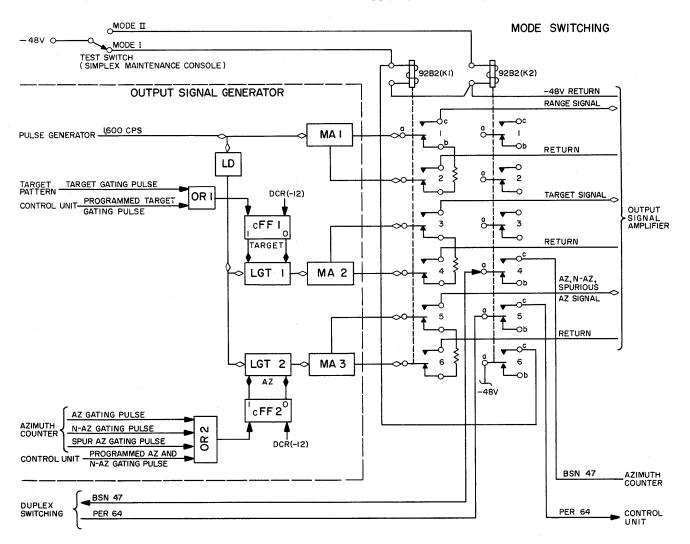

| 2.4.2.2 | Output Signal Generator                          | 231  |

| 2.4.2.3 | Mode Switching                                   | 231  |

| 2.4.2.4 | Output Signal Amplifiers                         | 231  |

| 2.4.3   | Signal Control Function                          | 231  |

| 2.4.3.1 | Mode I Single Message Signal Control             | 231  |

| 2.4.3.2 | Mode I Continuous Message Signal Control         | 231  |

| 2.4.3.3 | Mode II Type 1 Signal Control                    | 231  |

| 2.4.3.4 | Mode II Type 2 Signal Control                    | 232  |

| 2.5     | TFO and Pulse Generator                          | 233  |

| 2.6     | Output Signal Generator                          | 233  |

| 2.7     | Mode Switching                                   | 233  |

| 2.8     | Output Signal Amplifiers                         | 235  |

| 2.9     | Message Control Section                          | 235  |

| 2.9.1   | General                                          | 235  |

| 2.9.2   | Mode I Single Message Operation                  | 236  |

| 2.9.3   | Mode I Continuous Message Operation              | 236  |

| 2.9.4   | Mode II Type 2 Operation                         | 237  |

| 2.10    | Message Data Register                            | 237  |

| 2.11    | Message Length Register                          | 238  |

| 2.11.1  | Operation                                        | 238  |

| $H_{i}$ | eading  |                                                  | Page  |

|---------|---------|--------------------------------------------------|-------|

|         | 2.11.2  | Timing Relationship with Other Sections          | 240   |

|         | 2.12    | Sync and Data Gating Circuit                     | 240   |

|         | 2.13    | Duplex Switching                                 | 240   |

|         | 2.14    | Mode-Type Switching                              | 241   |

|         | 2.15    | PER 63 Synchronization                           | 242   |

|         | CHAPTER | 3 XTL TEST PATTERN GENERATOR                     | 243   |

|         | 3.1     | Overall Operation                                | 243   |

|         | 3.2     | Detailed Operation                               | 243   |

|         | 3.2.1   | Mode Switching                                   | 243   |

|         | 3.2.2   | Message Data Register                            | 243   |

|         | 3.2.3   | Mode-Type Switching                              | 243   |

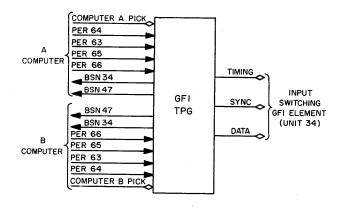

|         | CHAPTER | R 4 GFI TEST PATTERN GENERATOR                   | . 245 |

|         | 4.1     | General                                          | . 245 |

|         | 4.2     | Signal Composition                               | 245   |

|         | 4.2.1   | Types of Signals                                 | . 245 |

|         | 4.2.2   | Azimuth and North-Azimuth Cycle                  | . 245 |

|         | 4.2.3   | Missing and Spurious Azimuth Signals             | 245   |

|         | 4.2.4   | Early North and Late North                       | . 245 |

|         | 4.2.5   | Target Patterns                                  | . 245 |

|         | 4.3     | Modes and Mode-Types of Operation                | . 246 |

|         | 4.3.1   | General                                          | . 246 |

|         | 4.3.2   | Mode I                                           | . 246 |

|         | 4.3.3   | Mode II Type 1                                   | . 246 |

|         | 4.3.4   | Mode II Type 2                                   | . 246 |

|         | 4.3.5   | Mode II Type 3                                   | . 246 |

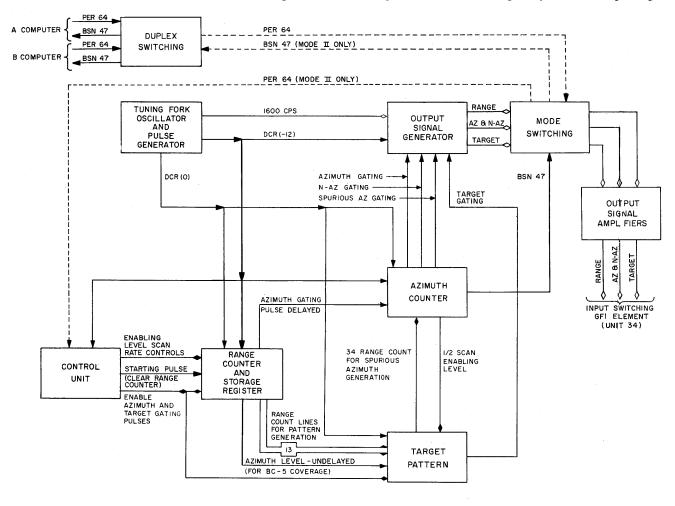

|         | 4.4     | Theory of Operation on the Section Diagram Level | . 246 |

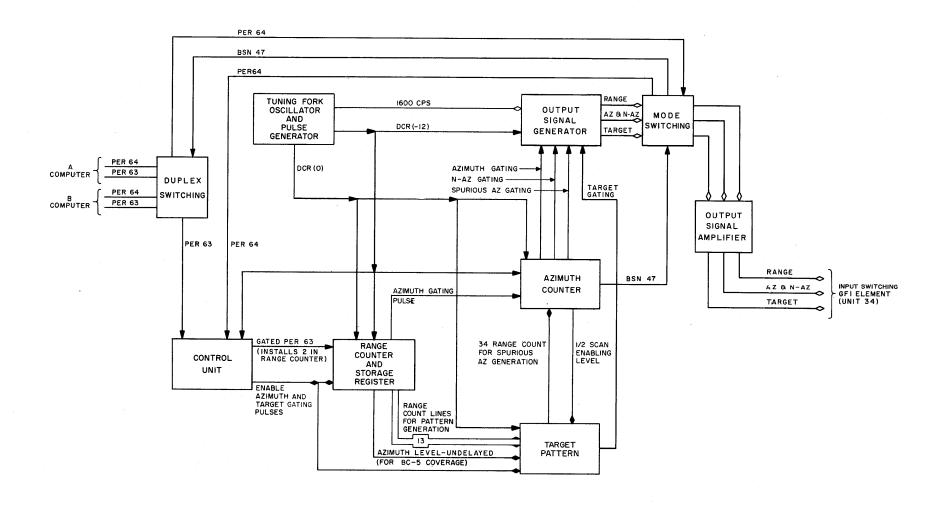

|         | 4.4.1   | General                                          | . 246 |

|         | 4.4.2   | Signal Generation Function                       | . 247 |

|         | 4.4.2.1 | TFO and Pulse Generator                          | . 247 |

|         | 4.4.2.2 | Output Signal Generator                          | . 247 |

|         | 4.4.2.3 | Mode Switching                                   | . 247 |

|         | 4.4.2.4 | Output Signal Amplifiers                         | . 248 |

|         | 4.4.3   | Signal Control Function                          | 248   |

| Hea | ding        |                                                     | Page |

|-----|-------------|-----------------------------------------------------|------|

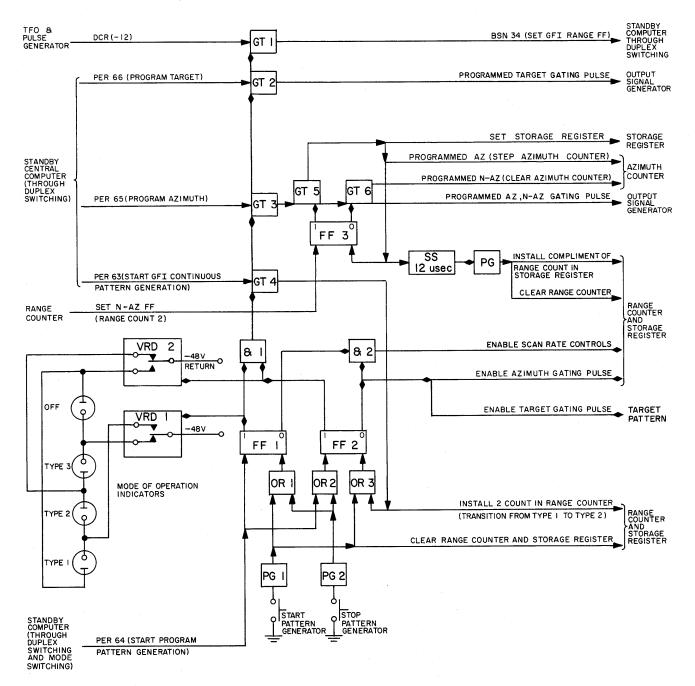

|     | 4.4.3.1     | Control Unit                                        | 248  |

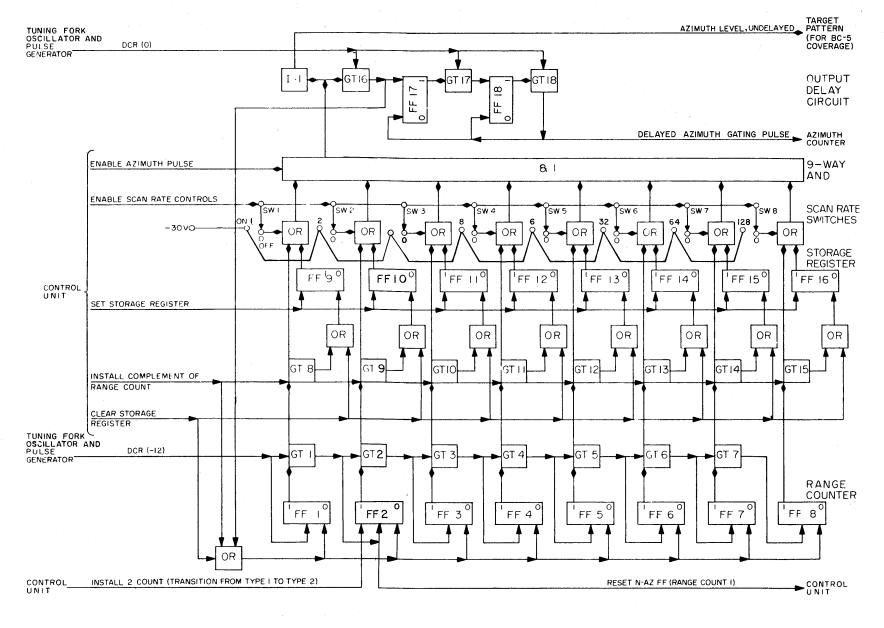

|     | 4.4.3.2     | Range Counter and Storage Register                  | 248  |

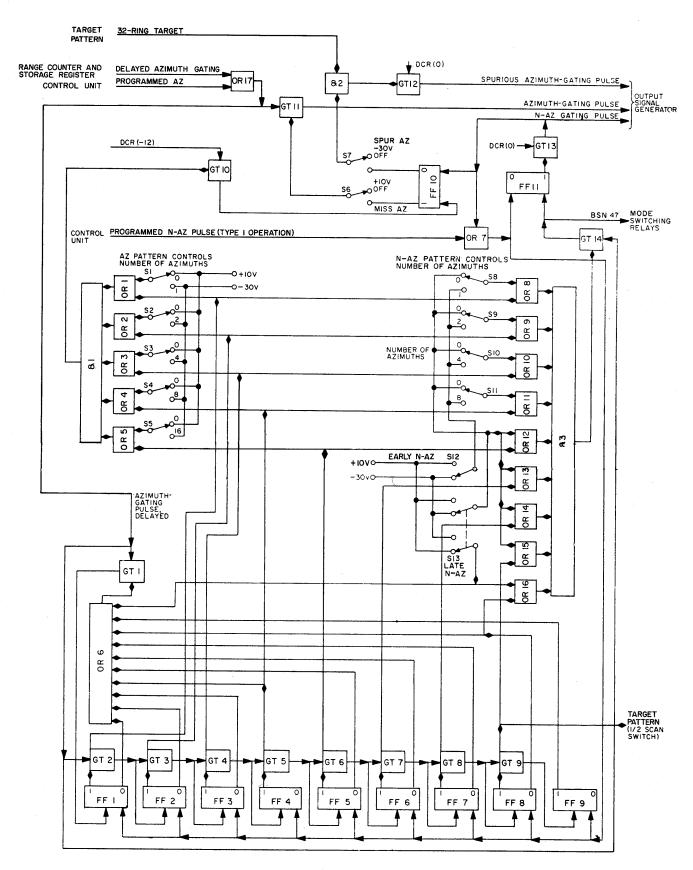

|     | 4.4.3.3     | Azimuth Counter                                     | 248  |

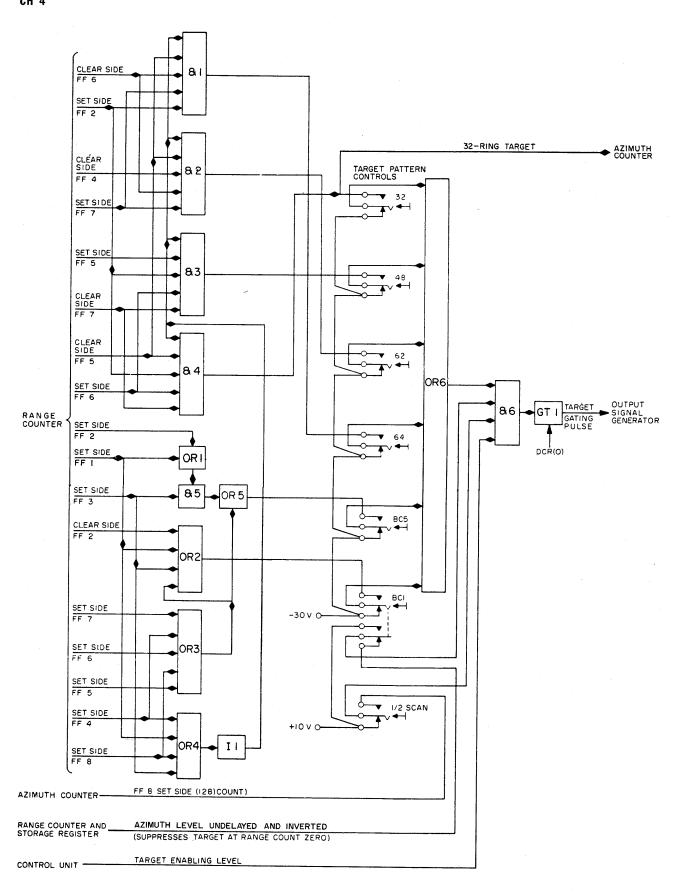

|     | 4.4.3.4     | Target Pattern                                      | 248  |

|     | 4.4.3.5     | Duplex Switching                                    | 250  |

|     | 4.5         | Sectional Operation in Various Modes and Mode Types | 250  |

|     | 4.5.1       | General                                             | 250  |

|     | 4.5.2       | Mode I                                              | 250  |

|     | 4.5.3       | Mode II Type 1                                      | 250  |

|     | 4.5.4       | Mode II Type 2                                      | 250  |

|     | 4.5.5       | Mode II Type 3                                      | 251  |

|     | 4.6         | TFO and Pulse Generator                             | 251  |

|     | <b>4.</b> 7 | Output Signal Generator                             | 251  |

|     | 4.8         | Mode Switching                                      | 252  |

|     | 4.9         | Output Signal Amplifiers                            | 252  |

|     | 4.10        | Control Unit                                        | 252  |

|     | 4.10.1      | Mode I Operation                                    | 252  |

|     | 4.10.2      | Mode II Type 1 Operation                            | 253  |

|     | 4.10.3      | Mode II Type 2 Operation                            | 254  |

|     | 4.10.4      | Mode II Type 3 Operation                            | 254  |

|     | 4.10.5      | Mode-Type Indications                               | 254  |

|     | 4.11        | Range Counter and Storage Register                  | 254  |

|     | 4.11.1      | General                                             | 254  |

|     | 4.11.2      | Range Counter                                       | 254  |

|     | 4.11.3      | Storage Register                                    | 256  |

|     | 4.11.4      | AND Circuit                                         | 256  |

|     | 4.11.5      | Scan Rate Switches                                  | 256  |

|     | 4.11.6      | Output Delay Circuit                                | 256  |

|     | 4.12        | Azimuth Counter Section                             | 257  |

|     | 4.12.1      | General                                             | 257  |

|     | 4.12.2      | Normal North-Azimuth Operation                      | 257  |

|     | 4.12.3      | Early-North Condition                               | 259  |

|     | 4.12.4      | Late-North Condition                                | 259  |

|     | 4.12.5      | Missing Azimuth Operation                           | 259  |

| Heading |                                                                                                                                     | Page |

|---------|-------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.12.6  | Spurious Azimuth Operation                                                                                                          | 260  |

| 4.13    | Target Pattern Generation                                                                                                           | 260  |

| 4.13.1  | General                                                                                                                             | 260  |

| 4.13.2  | Ring Target Patterns                                                                                                                | 260  |

| 4.13.3  | BC 1 Coverage                                                                                                                       | 262  |

| 4.13.4  | BC 5 Coverage                                                                                                                       | 262  |

| 4.13.5  | 1/2 SCAN Target Pattern                                                                                                             | 262  |

| 4.14    | Duplex Switching                                                                                                                    | 262  |

|         |                                                                                                                                     |      |

|         | INPUT SYSTEM OF THE AN/FSQ-8 COMBAT CONTROL CENTRAL                                                                                 |      |

| CHAPTE  | R 1 GENERAL                                                                                                                         | 263  |

| 1.1     | Comparison of AN/FSQ-7 Combat Direction Central and AN/FSQ-8 Combat Control Central                                                 | 263  |

| 1.2     | Purpose of AN/FSQ-8 Combat Control Central                                                                                          | 263  |

| 1.3     | Input System of AN/FSQ-8 Combat Control Central                                                                                     | 263  |

| СНАРТЕ  | R 2 DIFFERENCES BETWEEN INPUT SYSTEM EQUIP-<br>MENTS OF AN/FSQ-8 COMBAT CONTROL<br>CENTRAL AND AN/FSQ-7 COMBAT<br>DIRECTION CENTRAL | 265  |

| 2.1     | XTL Element                                                                                                                         |      |

| 2.2     | Test Pattern Generator                                                                                                              |      |

| 2.3     | Simplex Maintenance Console                                                                                                         |      |

| 4.3     | Simplex Plantenance Console                                                                                                         | 20)  |

| INDEX   |                                                                                                                                     | 277  |

# LIST OF ILLUSTRATIONS

| Figure | Title                                                               | Page |

|--------|---------------------------------------------------------------------|------|

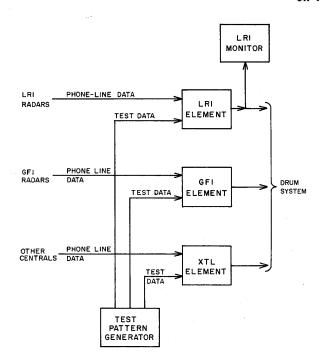

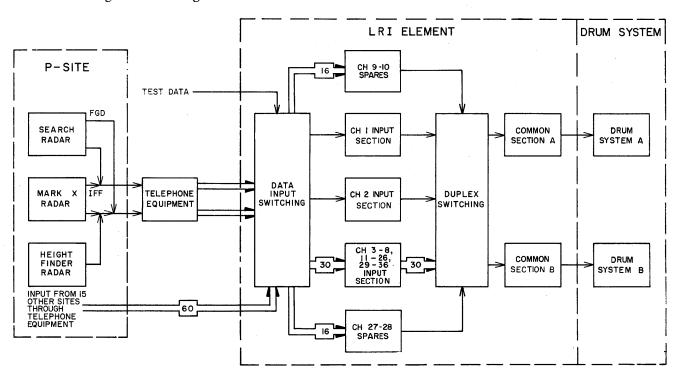

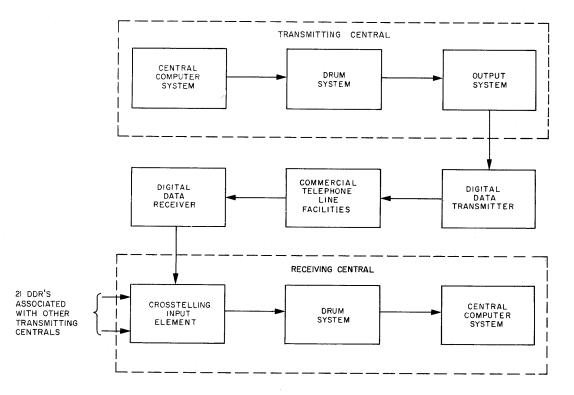

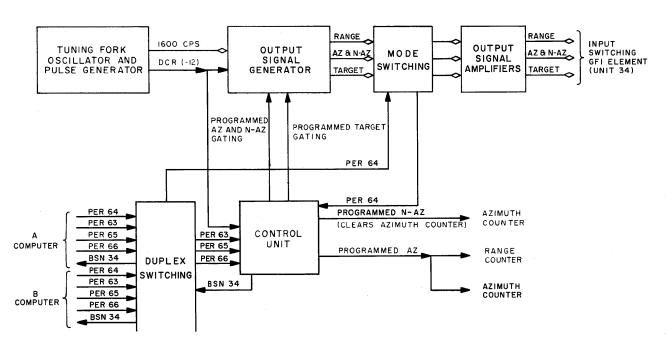

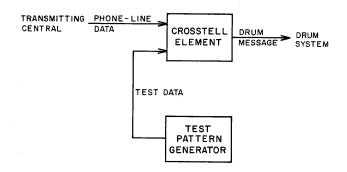

| 1-1    | Input System Block Diagram and Signal Flow                          | . 2  |

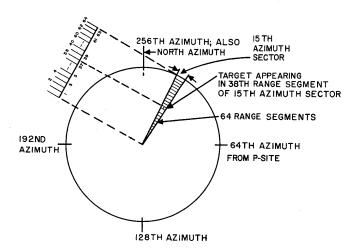

| 1-2    | Quantizing of GFI Information                                       | . 7  |

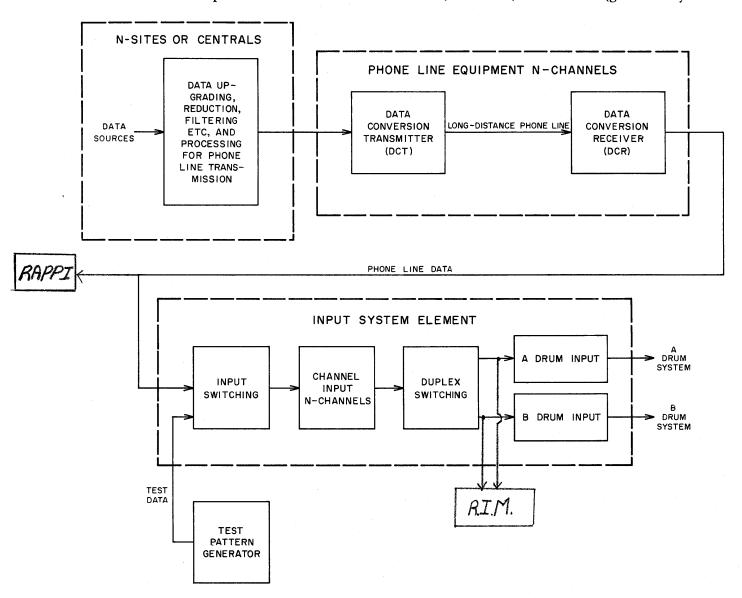

| 1-3    | Typical Input System Element and Data Flow                          | . 9  |

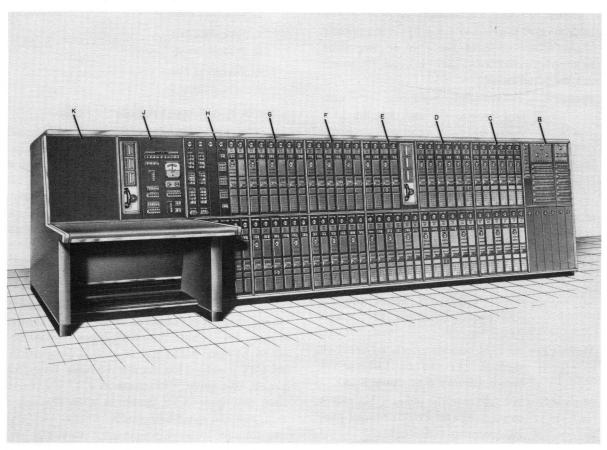

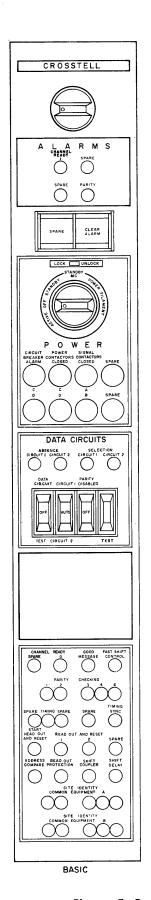

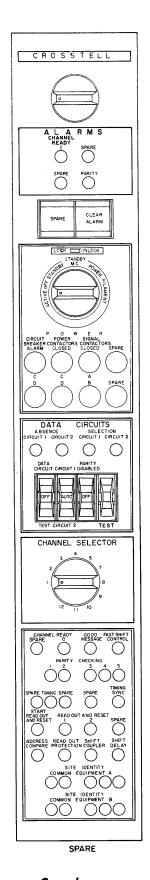

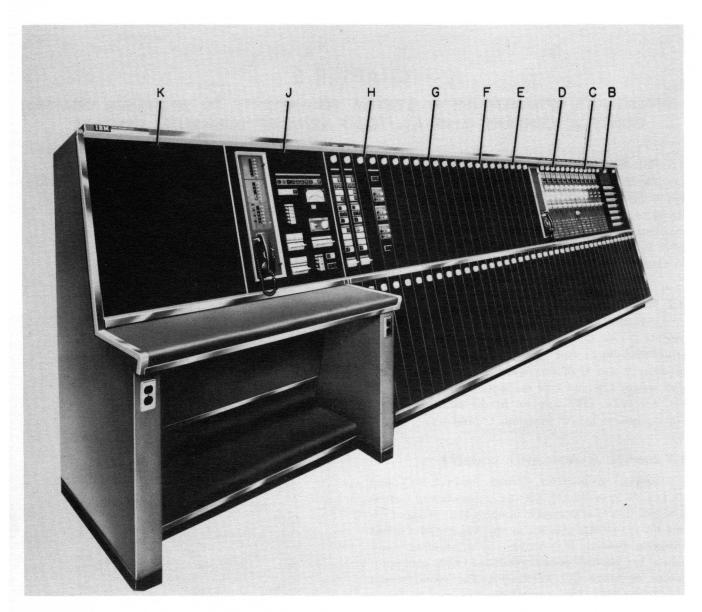

| 1-4    | Simplex Maintenance Console (12 XTL-Channel Installation)           | . 15 |

| 2-1    | LRI Information Flow, Simplified Diagram                            | . 19 |

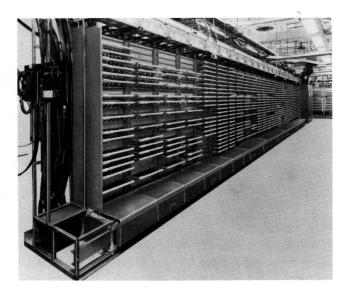

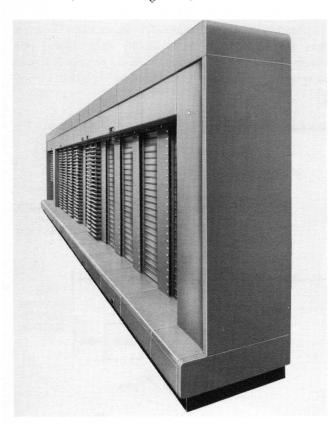

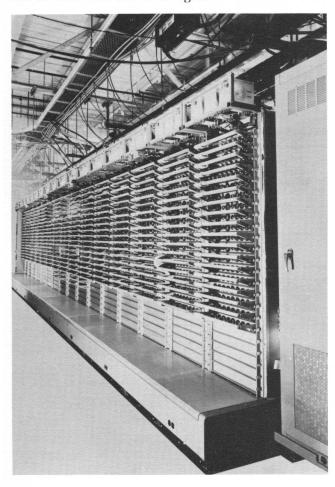

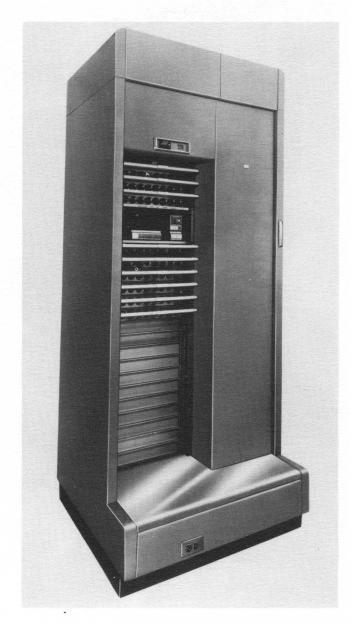

| 2-2    | LRI Unit 41                                                         | . 20 |

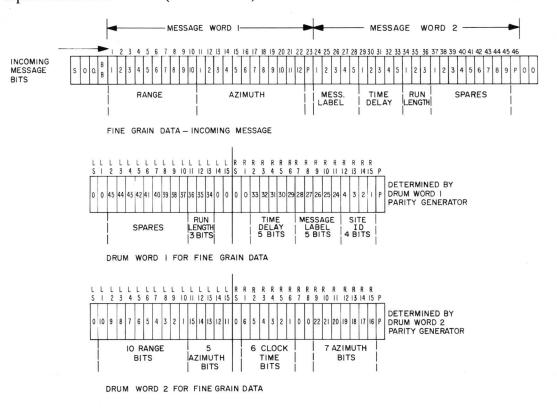

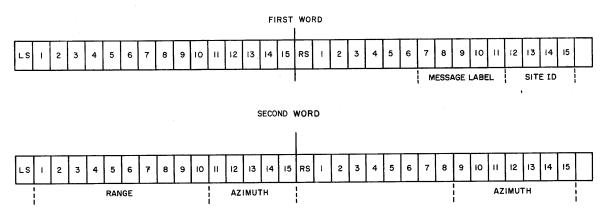

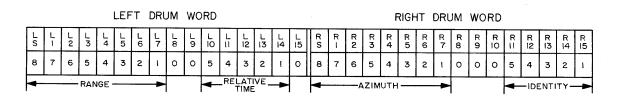

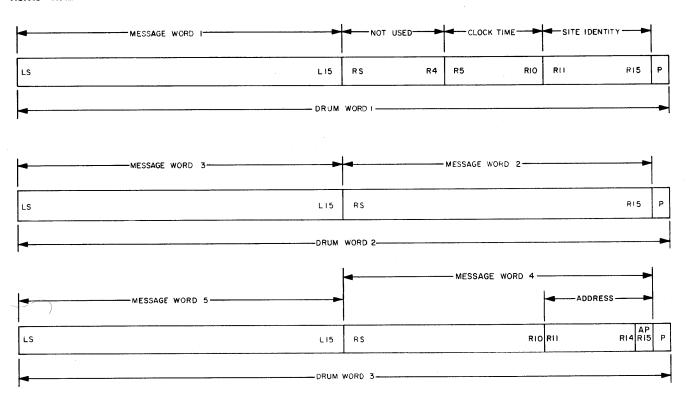

| 2-3    | Message and Drum Word Layout, Fine Grain Data Message               | . 20 |

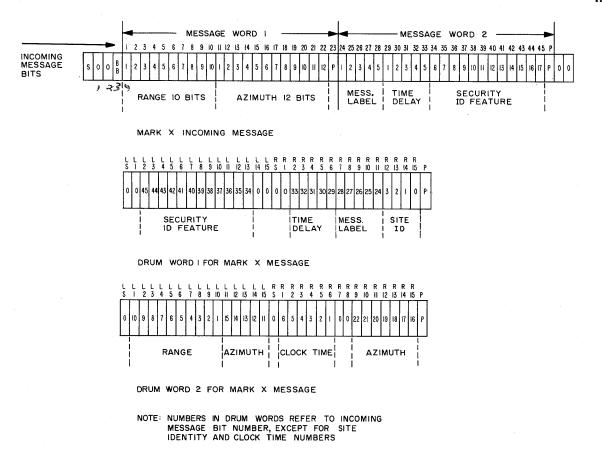

| 2-4    | Message and Drum Word Layout, MK X Message                          | . 21 |

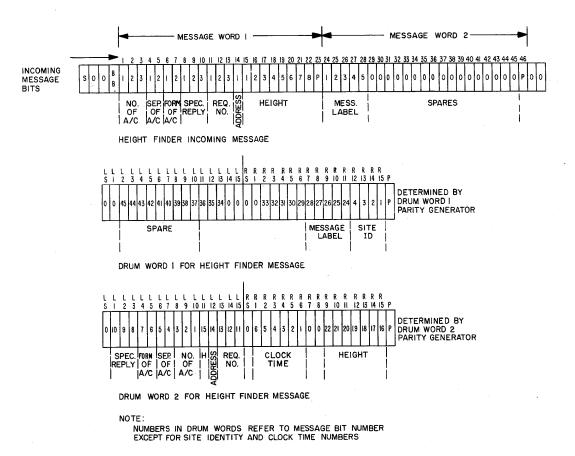

| 2-5    | Message and Drum Word Layout, Height-Finder Message                 | . 22 |

| 2–6    | LRI Input Element, Block Diagram                                    | 23   |

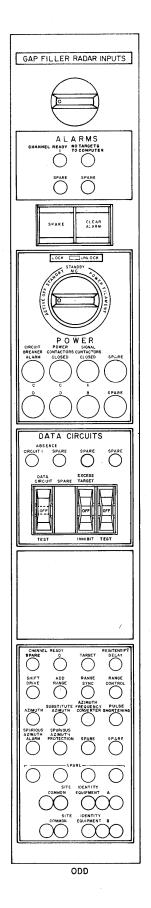

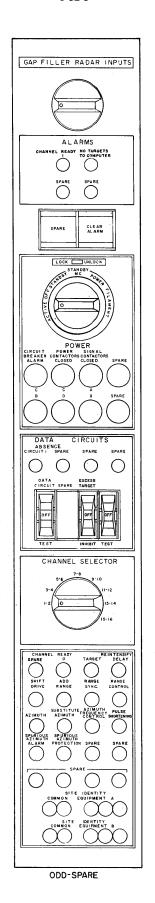

| 2-7    | LRI Control Panel, Odd and Odd-Spares                               | 24   |

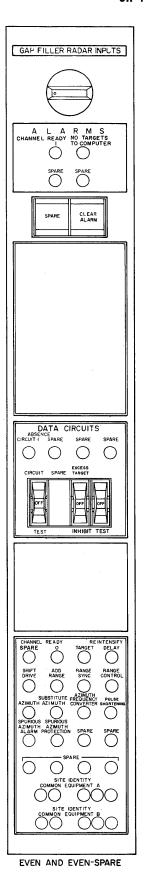

| 2-8    | LRI Control Panel, Even and Even-Spares                             | 24   |

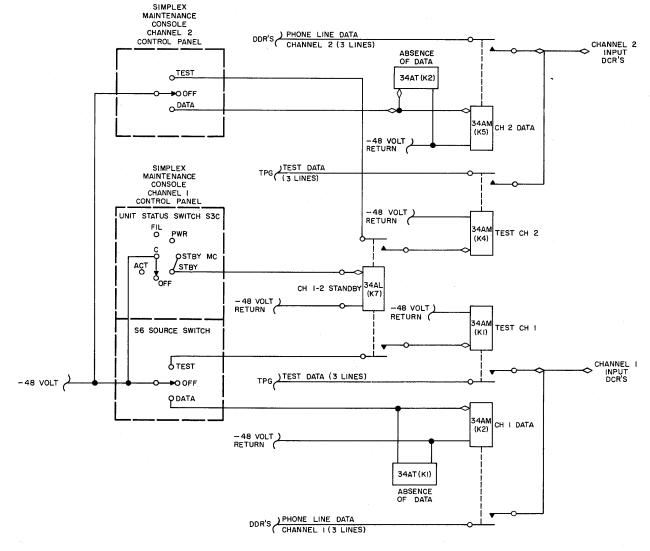

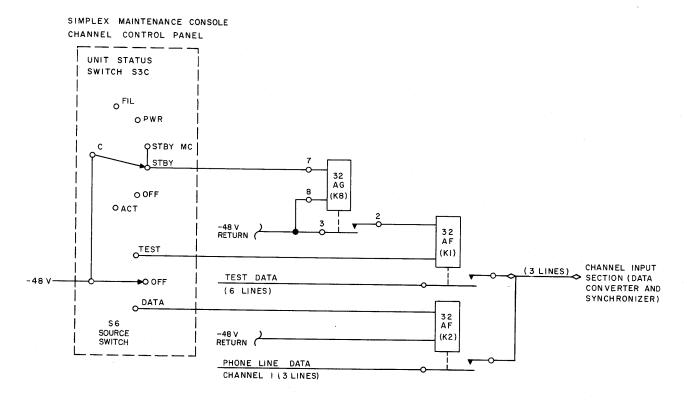

| 2-9    | Input-Data Switching, Channels 1 and 2                              | 28   |

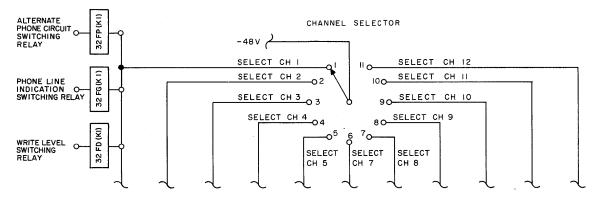

| 2-10   | Spare-Channel Switching                                             | 29   |

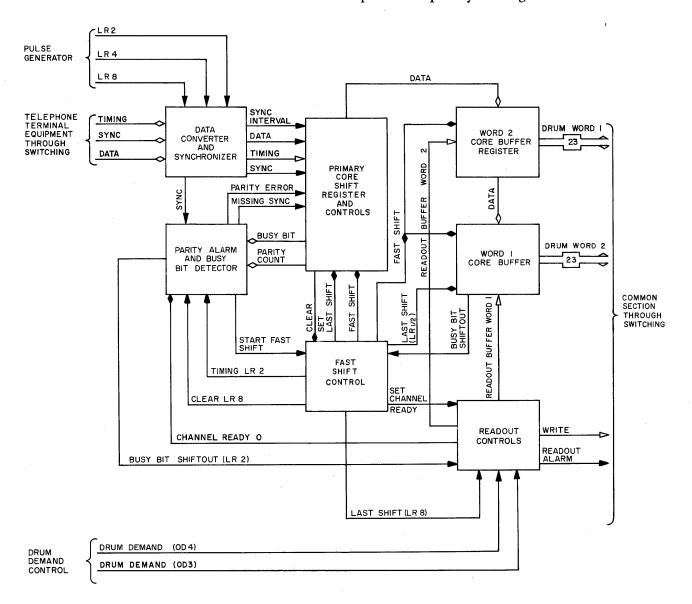

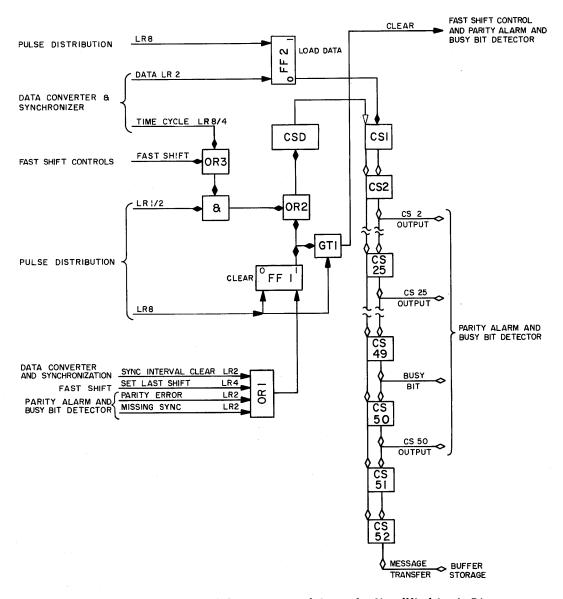

| 2-11   | LRI Channel Equipment, Simplified Logic Diagram                     | 32   |

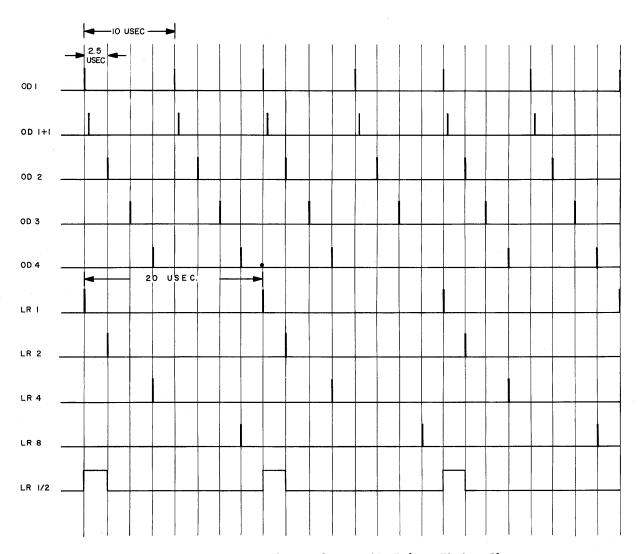

| 2-12   | Relation of LR Pulses to OD Pulses, Timing Chart                    | 33   |

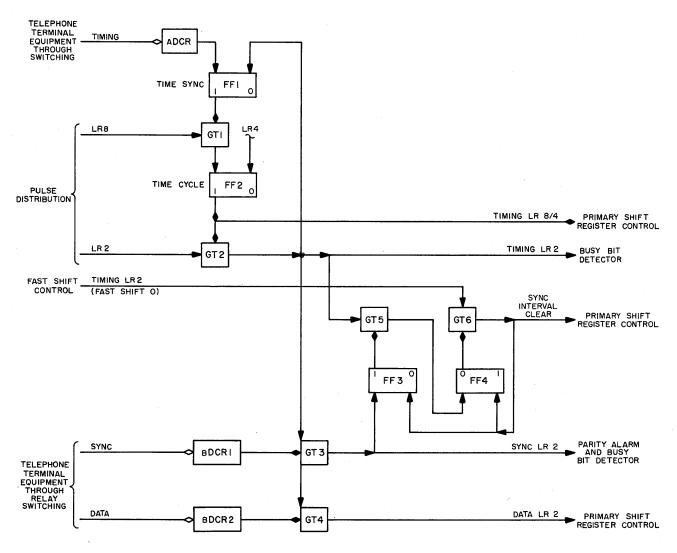

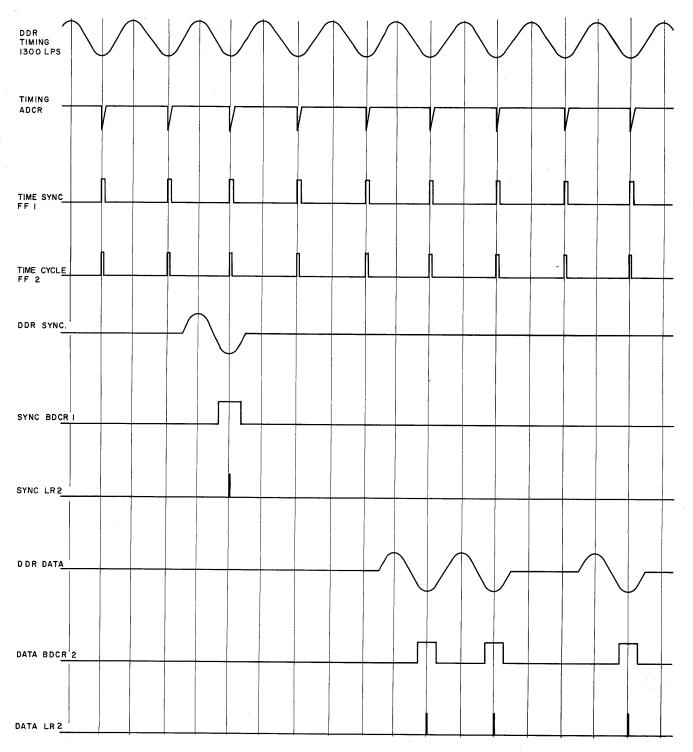

| 2-13   | Data Converter and Synchronizer, Simplified Logic Diagram           | 34   |

| 2-14   | Data Converter and Synchronizer, Timing Chart                       | 35   |

| 2-15   | Primary Core Shift Register and Controls, Simplified Logic Diagram  | 36   |

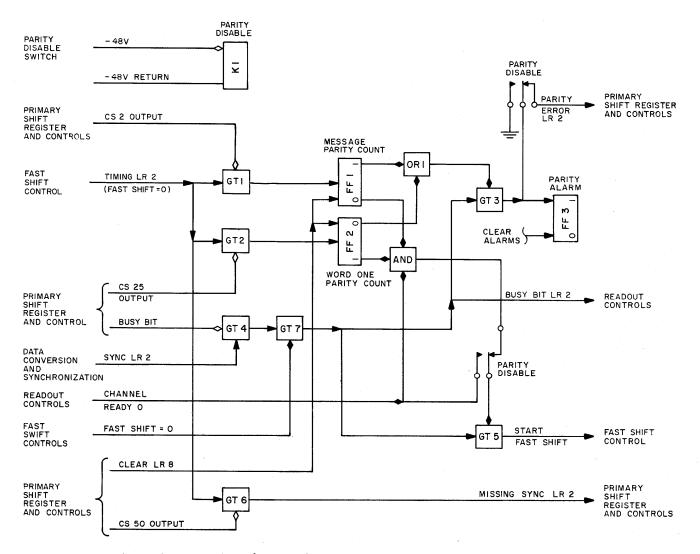

| 2–16   | Parity Alarm and Busy Bit Detector, Simplified Logic Diagram        | 37   |

| 2-17   | Fast-Shift Controls, Simplified Logic Diagram                       | 38   |

| 2-18   | Word 1 and 2 Core Buffer Registers, Simplified Logic Diagram        | 40   |

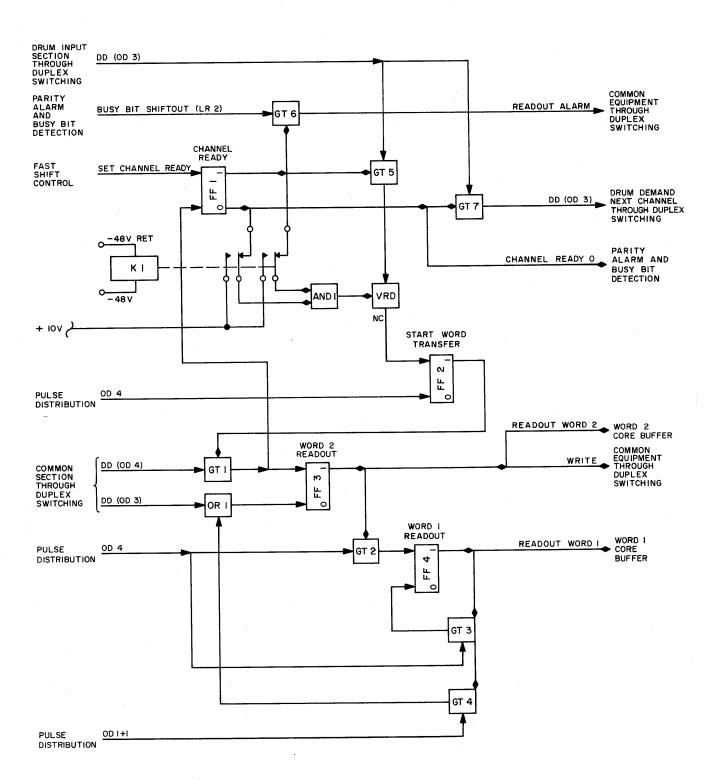

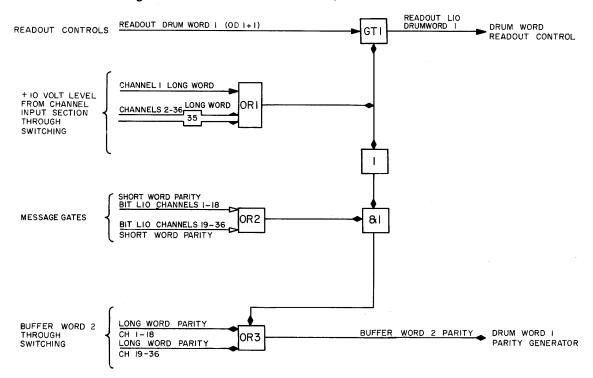

| 2-19   | Readout Controls, Simplified Logic Diagram                          | 42   |

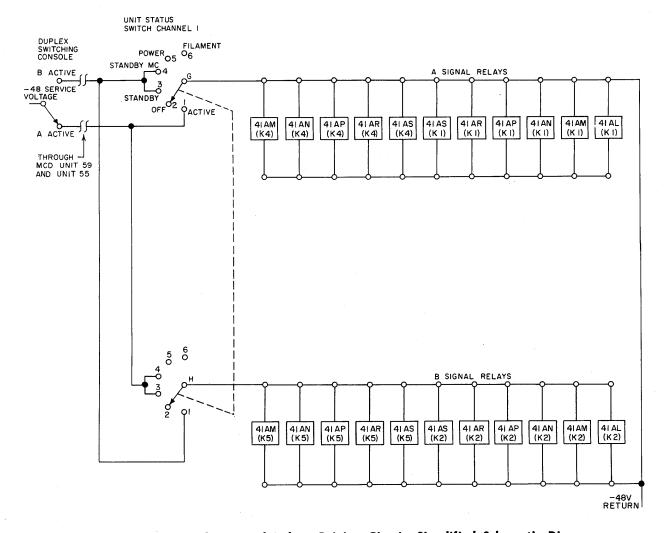

| 2-20   | A and B Signal Relays Driving Circuit, Simplified Schematic Diagram | 44   |

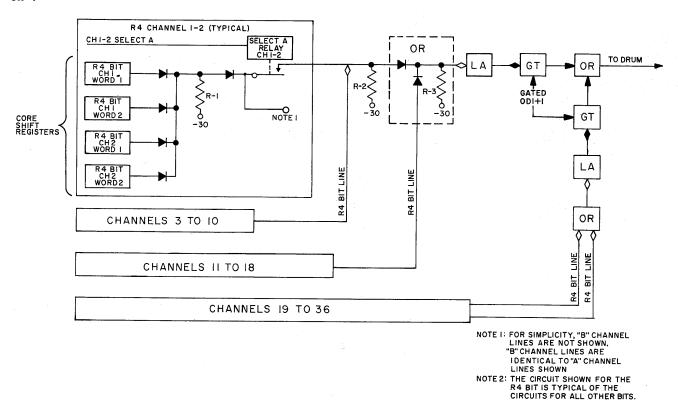

| 2-21   | Core-Data Switching                                                 | 45   |

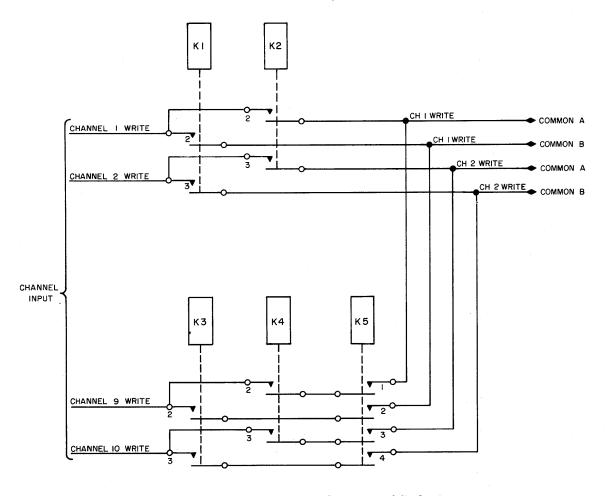

| 2-22   | Write Level Switching, Simplified Diagram                           | 47   |

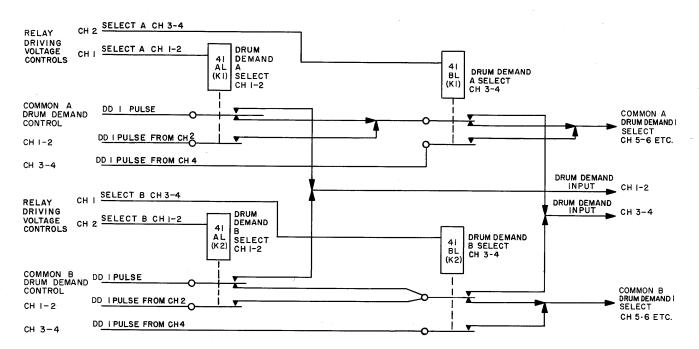

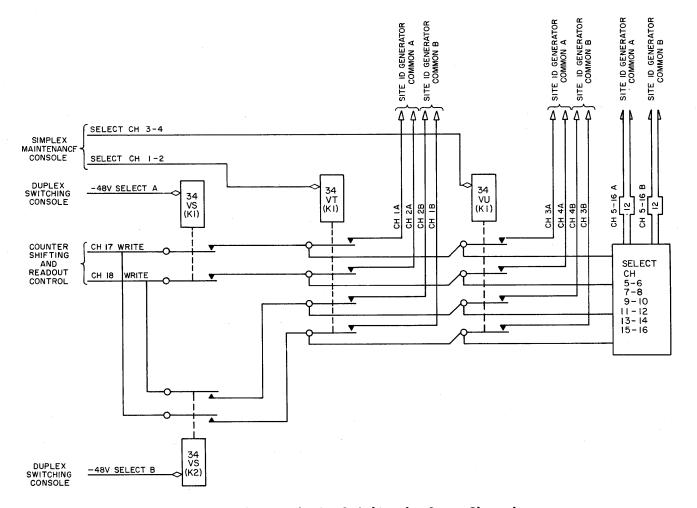

| 2-23   | Drum-Demand Switching (chan. 1 and 2; chan. 3 and 4)                | 48   |

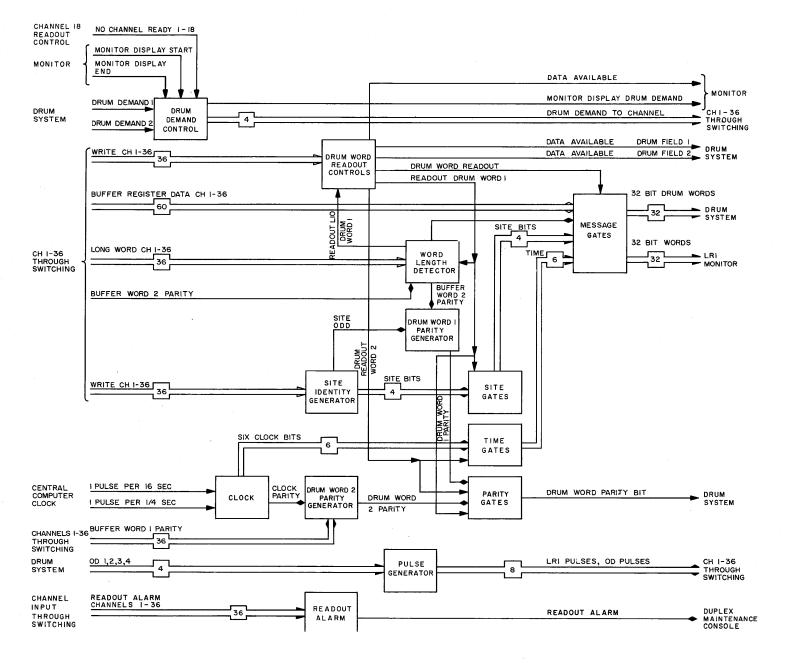

| 2-24   | LRI Common A, Simplified Block Diagram                              |      |

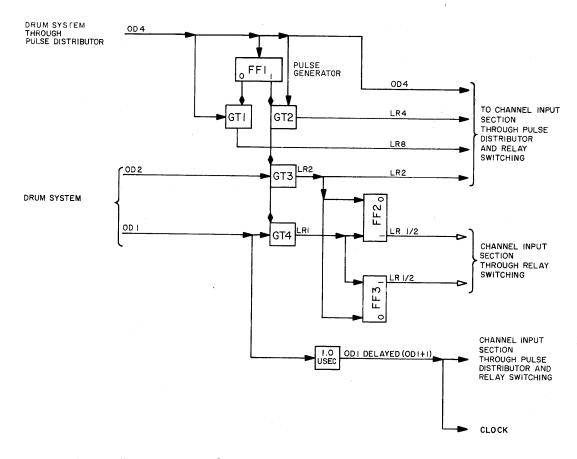

| 2-25   | Pulse Generator, Simplified Logic Diagram                           |      |

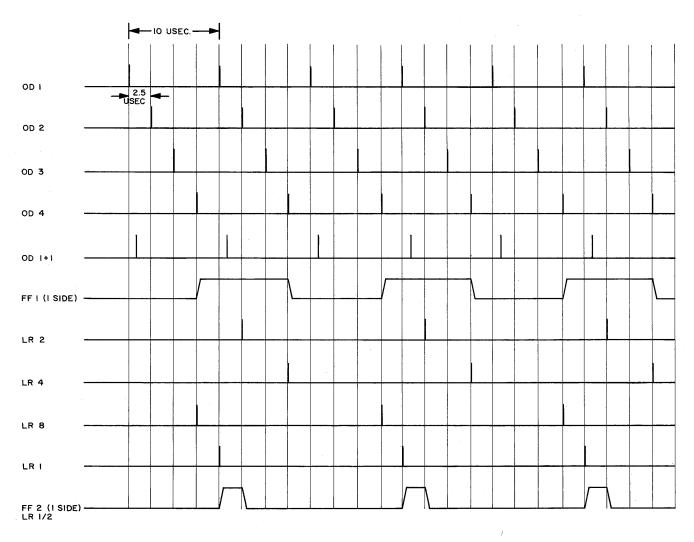

| 2-26   | Pulse Generator, Timing Chart                                       |      |

|        | ~                                                                   |      |

| Figure | Title                                                                         | Page       |

|--------|-------------------------------------------------------------------------------|------------|

| 2-27   | Drum-Demand Control, Simplified Logic Diagram                                 | 56         |

| 2-28   | Drum-Demand Control, Timing Chart                                             | <b>5</b> 7 |

| 2-29   | Site Identity Generator, Simplified Logic Diagram                             | 59         |

| 2-30   | Clock, Simplified Logic Diagram                                               | 61         |

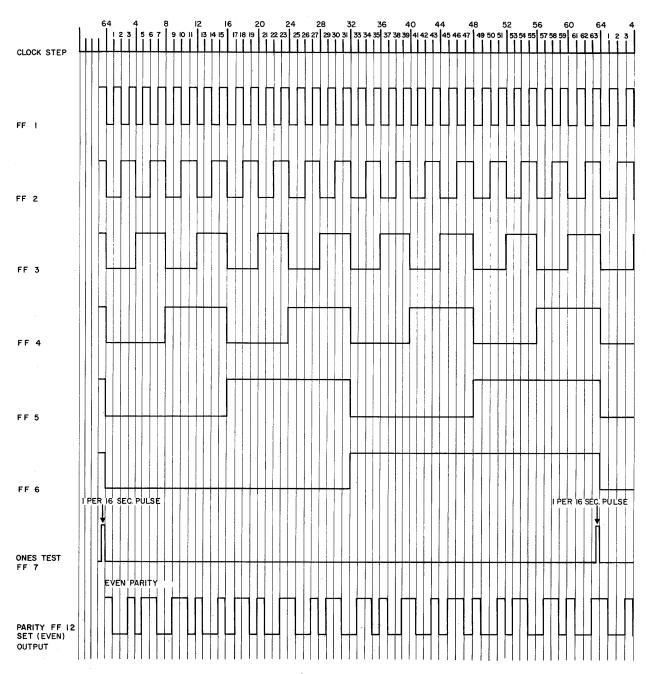

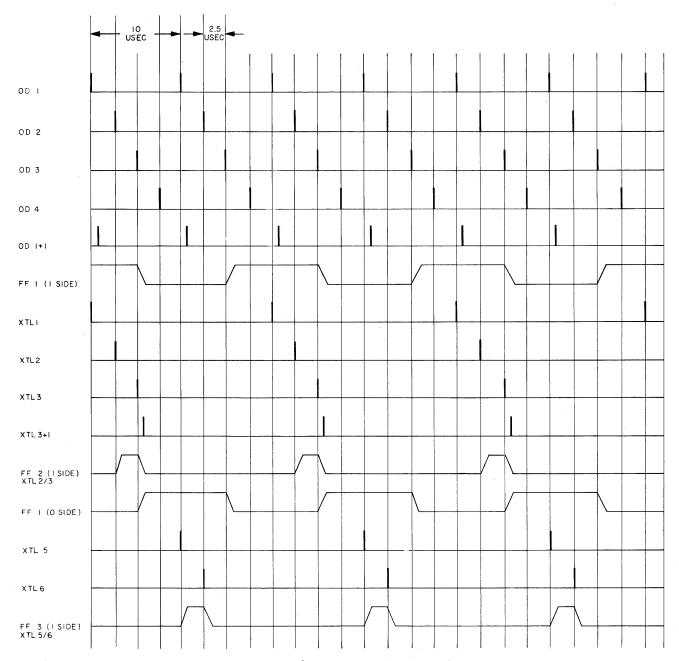

| 2-31   | Clock-Stepping and Synchronizing, Timing Chart                                | 62         |

| 2-32   | Clock Timing Chart, Binary Counter Output                                     | 63         |

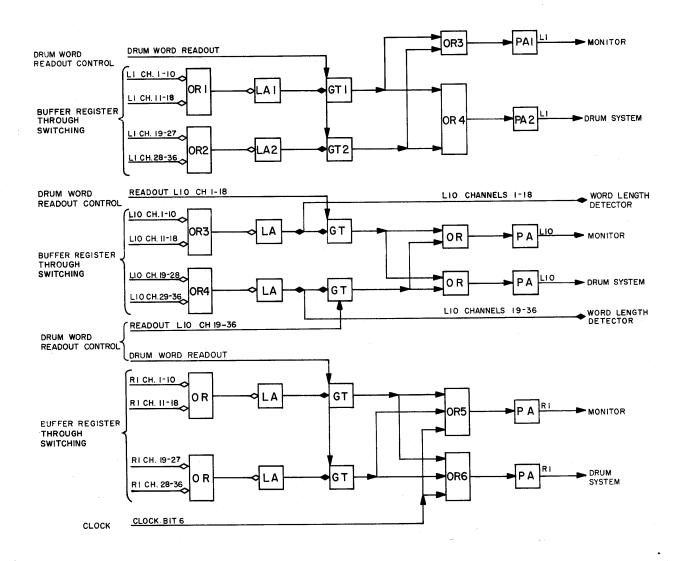

| 2-33   | Drum Word Readout Controls, Simplified Logic Diagram                          | 66         |

| 2-34   | Drum Word Readout Controls, Timing Chart                                      | <b>6</b> 7 |

| 2-35   | Drum Word 1 Parity Generator, Simplified Logic Diagram                        | 68         |

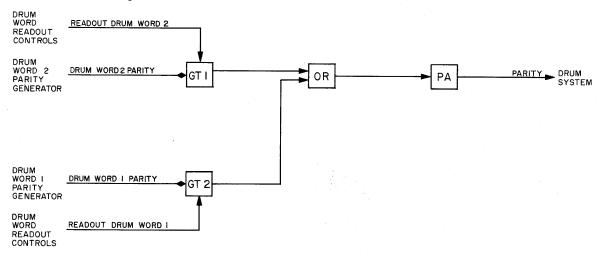

| 2-36   | Drum Word 2 Parity Generator, Simplified Logic Diagram                        | 69         |

| 2-37   | Site Gates, Simplified Logic Diagram                                          | 70         |

| 2-38   | Time Gates, Simplified Logic Diagram                                          | 70         |

| 2-39   | Parity Gates, Simplified Logic Diagram                                        | 71         |

| 2-40   | Message Gates, Simplified Logic Diagram                                       | 72         |

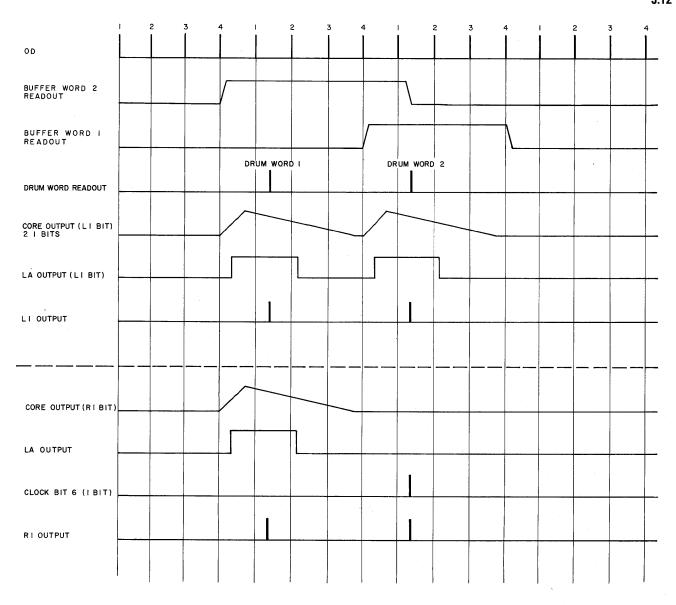

| 2-41   | Message Gates, Timing Chart                                                   | 73         |

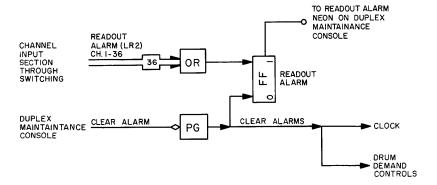

| 2-42   | Readout Alarm, Simplified Logic Diagram                                       | 74         |

| 2-43   | Word-Length Detector, Simplified Logic Diagram                                | 74         |

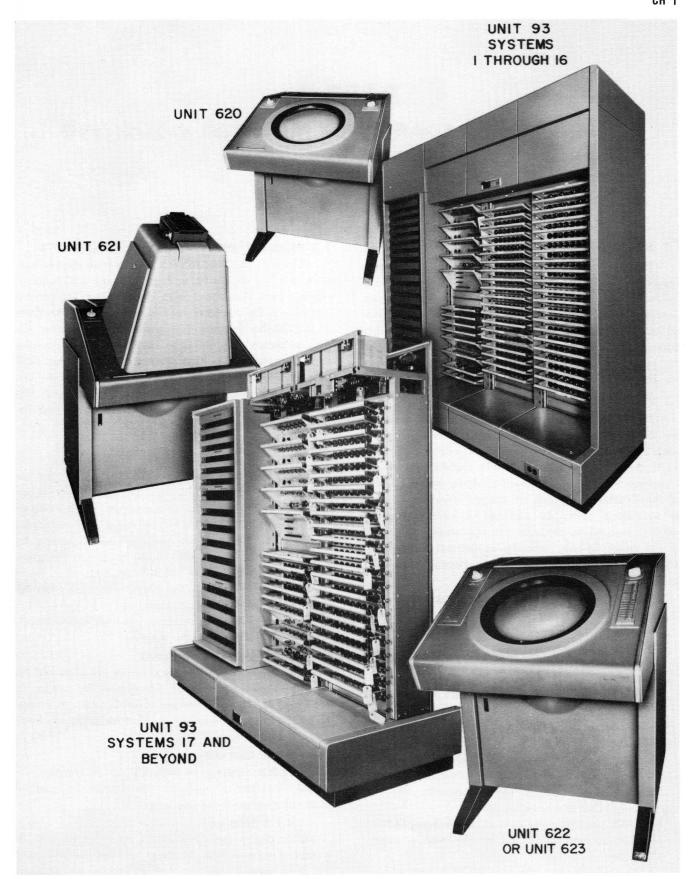

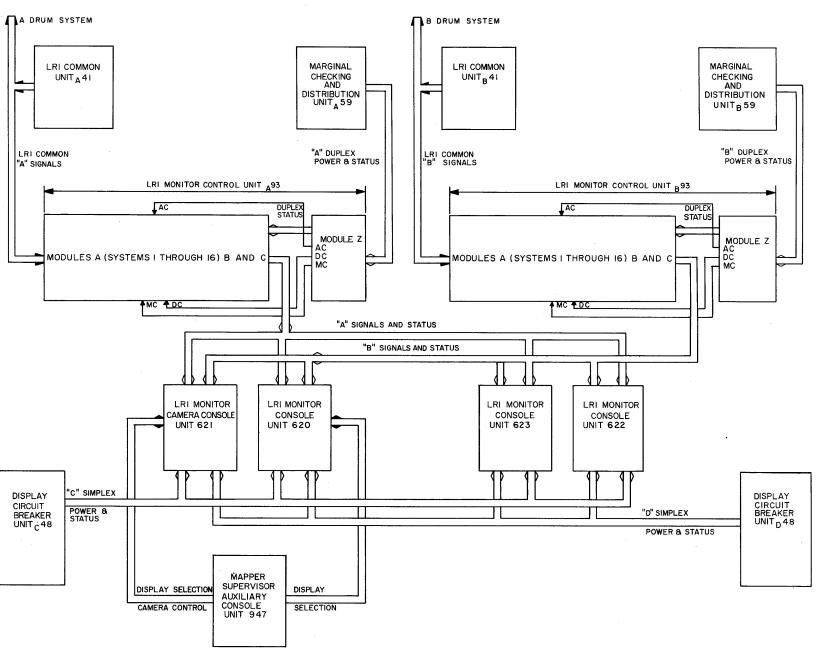

| 3-1    | LRI Monitor Equipment                                                         | 78         |

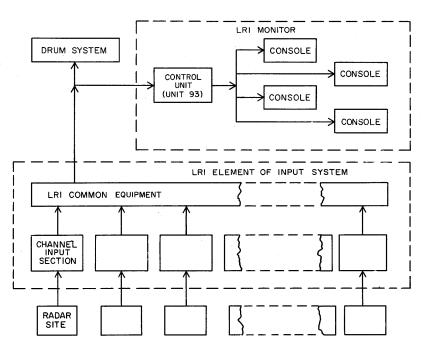

| 3-2    | Position of LRI Monitor in Input System                                       | 79         |

| 3-3    | Composition of LRI Message to LRI Monitor                                     | 80         |

| 3-4    | Relationship of LRI Monitor to Associated Equipment                           | 81         |

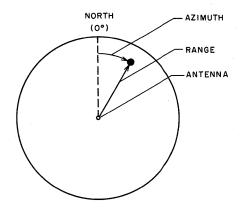

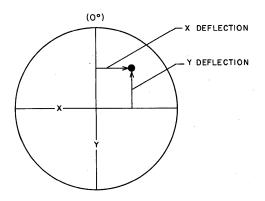

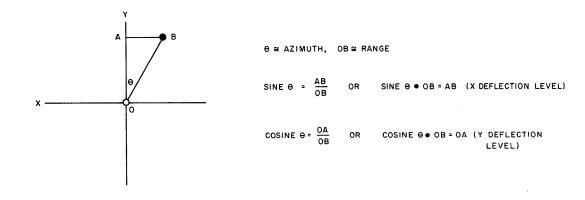

| 3-5    | Target Positioning by Polar and Cartesian Co-ordinates                        | 82         |

| 3-6    | Mathematical Basis for Development of Deflection Levels                       | 82         |

| 3-7    | Digital Equivalents of Approximations of Sine $\theta$ and Cosine $\theta$    | 82         |

| 3-8    | LRI Monitor Functional Diagram                                                | 84         |

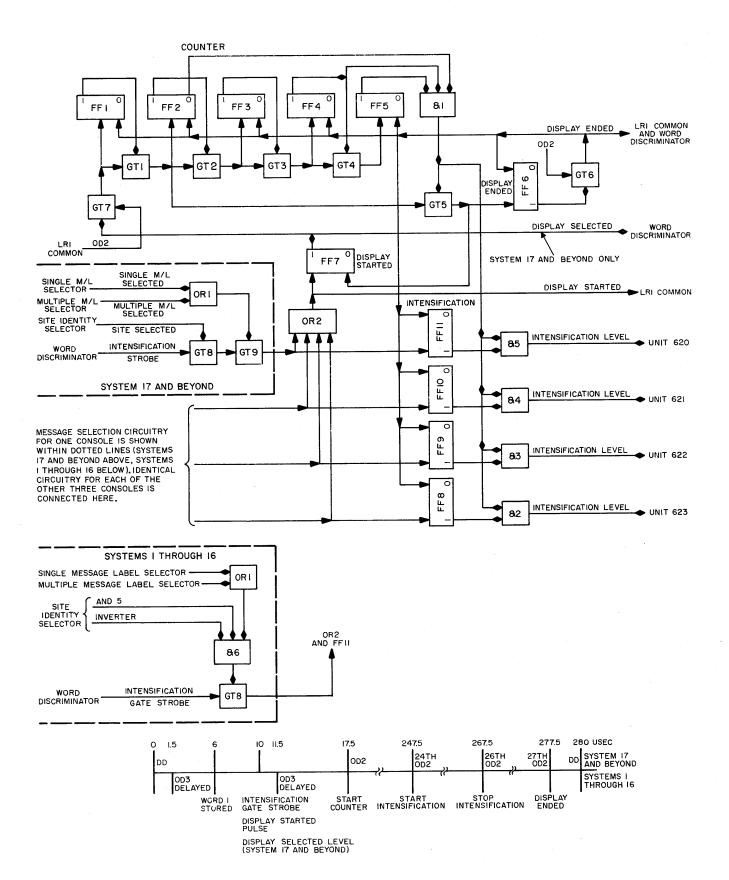

| 3-9    | LRI Monitor Digital Section, Overall Section Diagram                          | 88         |

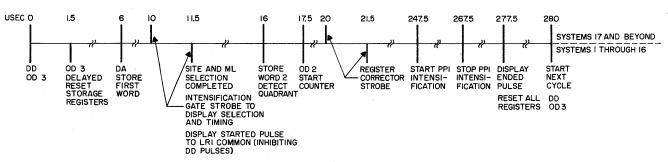

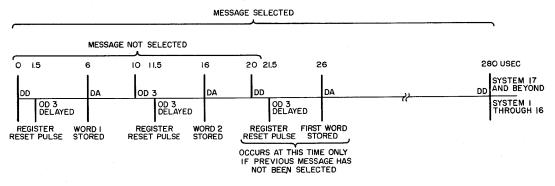

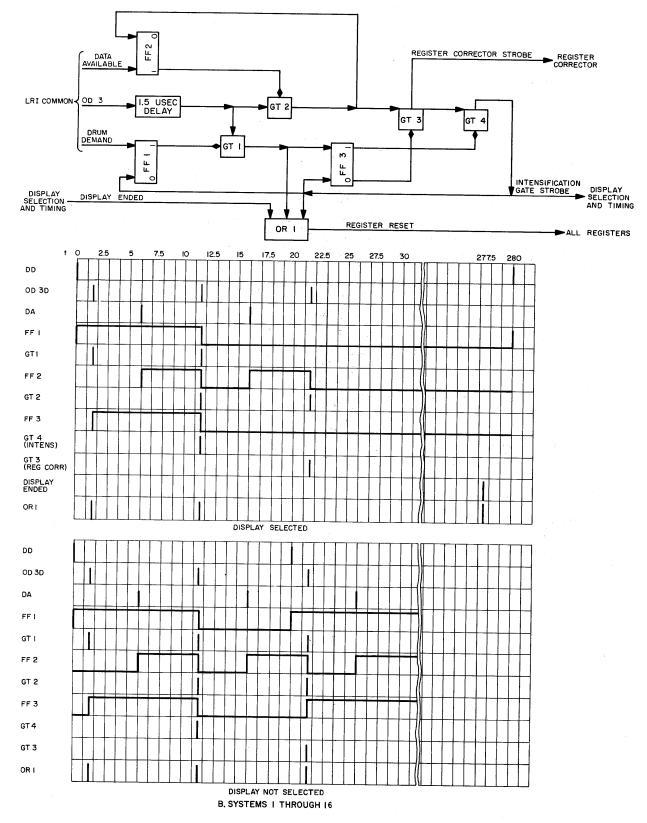

| 3-10   | LRI Monitor, Overall Timing Charts                                            | 89         |

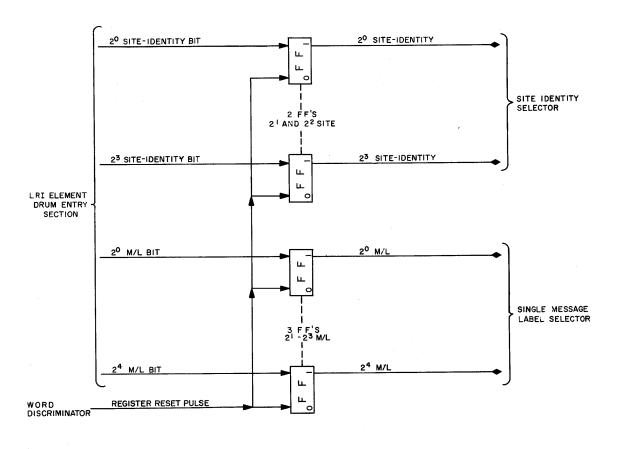

| 3-11   | Site and Message Label Storage Register, Simplified Logic and Timing Diagrams | 90         |

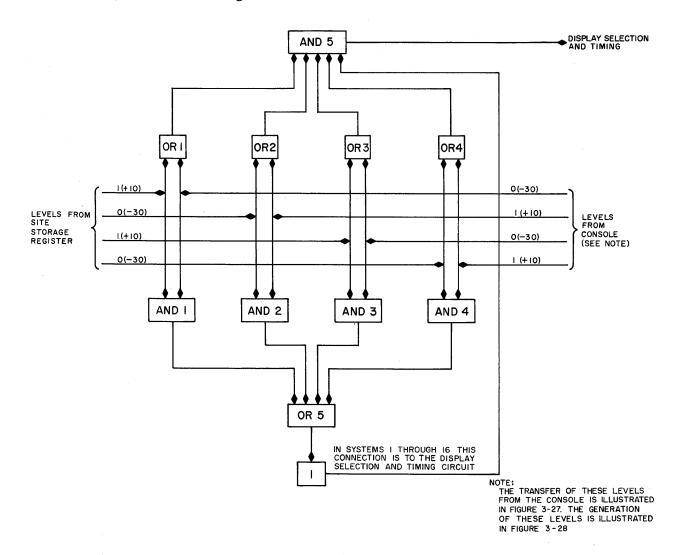

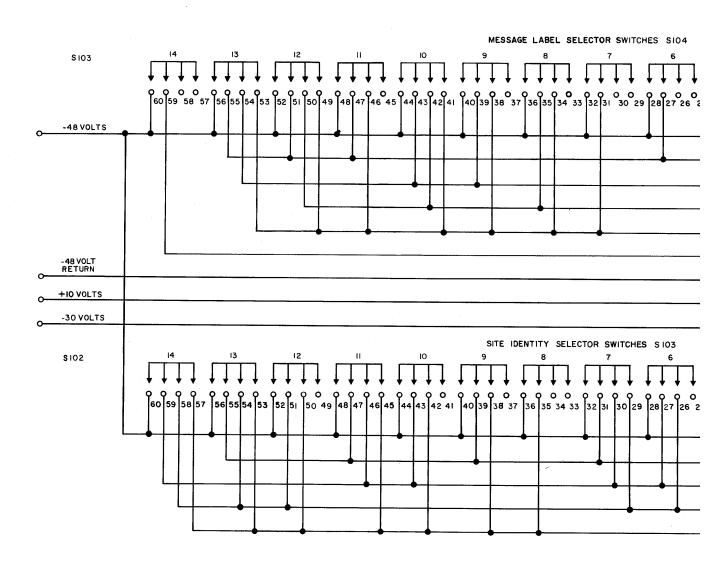

| 3-12   | Site Identity Selector, Simplified Logic Diagram                              | 92         |

| 3-13   | Single-Message Label Selector, Simplified Logic Diagram                       | 93         |

| 3-14   | Multiple-Message Label Selector, Simplified Logic Diagram                     | 94         |

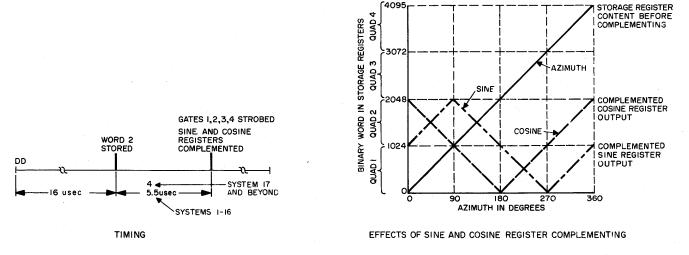

| 3-15   | Sine and Cosine Storage Registers, Simplified Logic and<br>Timing Diagrams    | 95         |

| Figure      | Title                                                                                           | Page      |

|-------------|-------------------------------------------------------------------------------------------------|-----------|

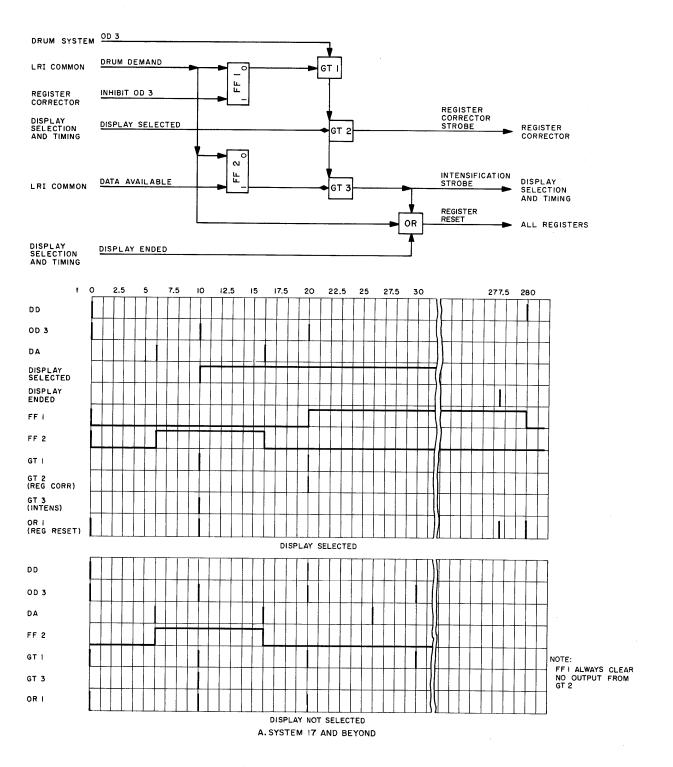

| 3–16        | Register Corrector, Logic and Timing Diagrams                                                   | 96        |

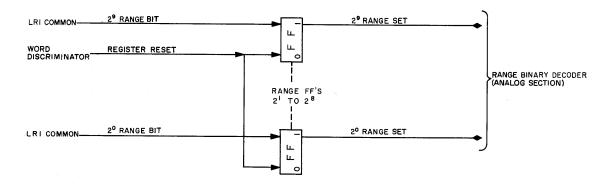

| 3—17        | Range Storage Register, Simplified Logic and Timing Diagrams                                    | 97        |

| 3-18        | Word Discriminator, Simplified Logic and Timing Diagrams                                        | . 267/268 |

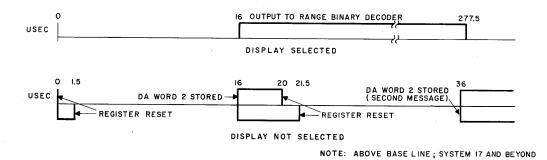

| 3—19        | Display Selection and Timing, Simplified Logic and Timing Diagrams                              | 98        |

| 3-20        | Simplified Logic Diagram of Analog Section                                                      | 101       |

| 3-21        | D-C Distribution and Voltage Regulation, Analog Section                                         | 103       |

| 3-22        | Block Diagram of CRT Circuitry                                                                  | 105       |

| 3-23        | Display Console Calibration Test Panel                                                          | 106       |

| 3-24        | Calibration Test Panel, Circuit Diagram                                                         | 107       |

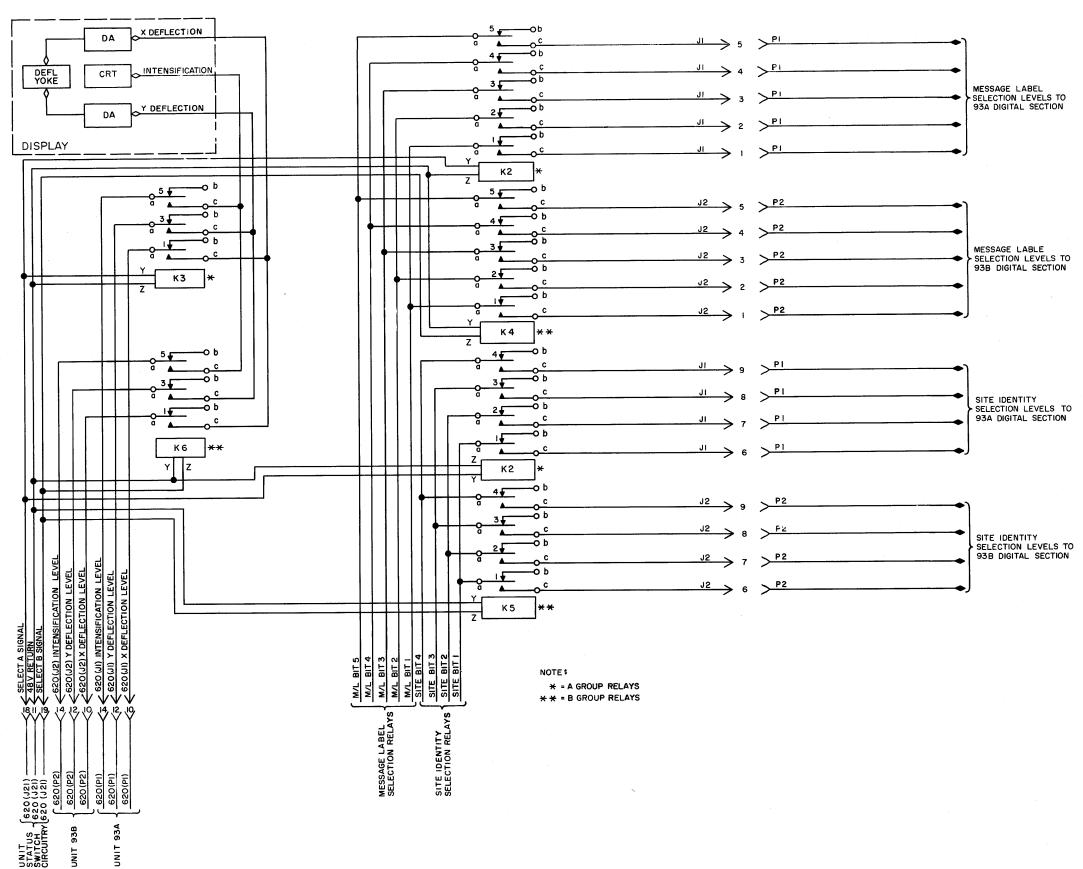

| 3-25        | Section Diagram of Switching Section                                                            | 110       |

| 3–26        | Unit Status Switching Diagram                                                                   | 112       |

| 3-27        | Signal Application Control Relay, Circuit Diagram                                               | . 269/270 |

| 3-28        | Site and Message Label Selector Switch and Relay,<br>Circuit Diagram                            | . 271/272 |

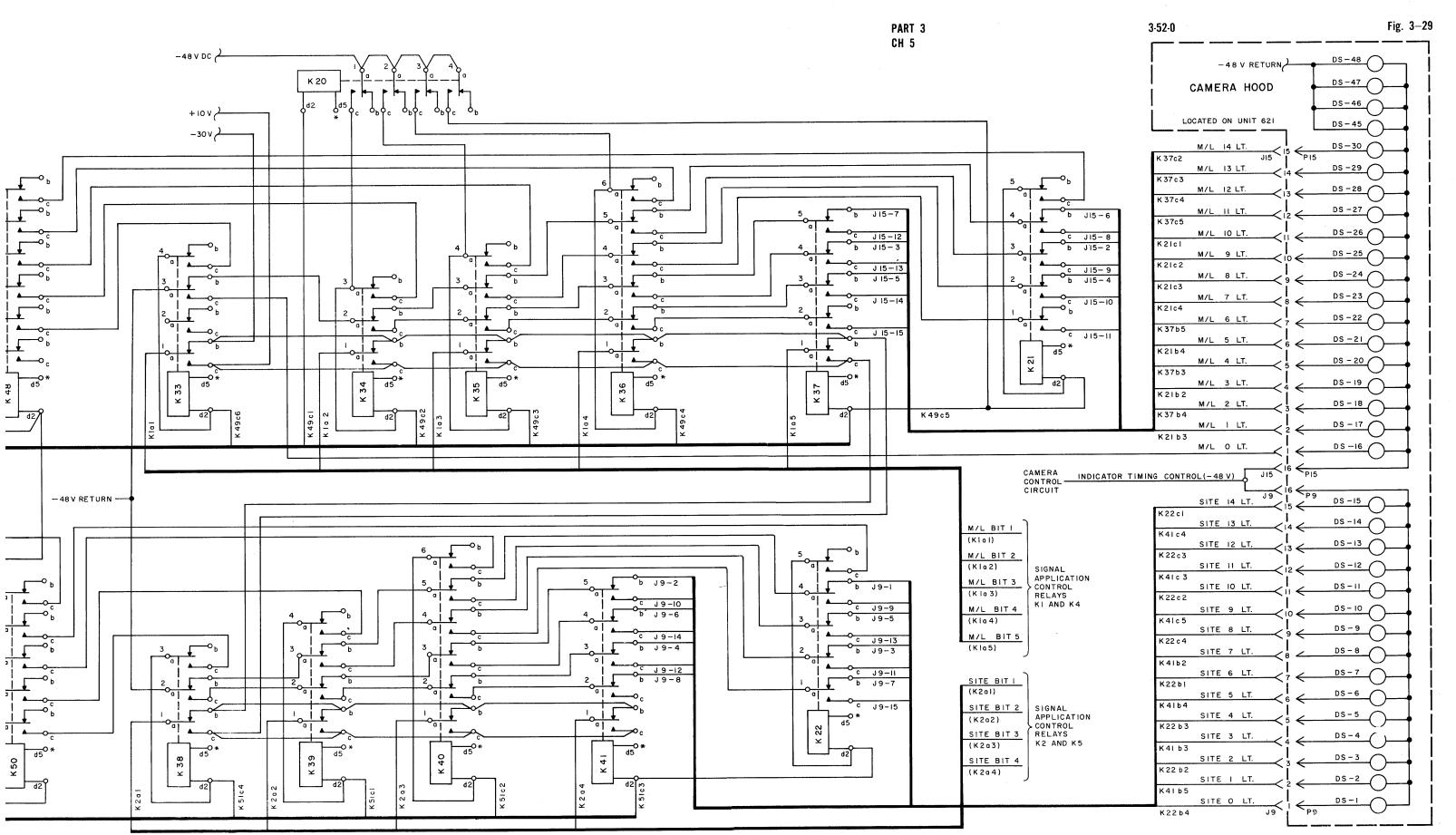

| 3-29        | Camera Console Unit, Site and Message Label Selection Relay and Indicator Lamp, Circuit Diagram | . 273/274 |

| 3-30        | Camera Control, Circuit Diagram                                                                 | . 275/276 |

| 4-1         | Transmission of GFI Information                                                                 | 117       |

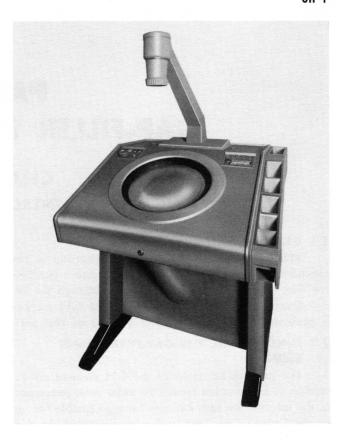

| 4-2         | GFI Unit 34                                                                                     | 118       |

| 4-3         | GFI Mapper Console                                                                              | 118       |

| 4-4         | GFI Drum Word Layout                                                                            | 119       |

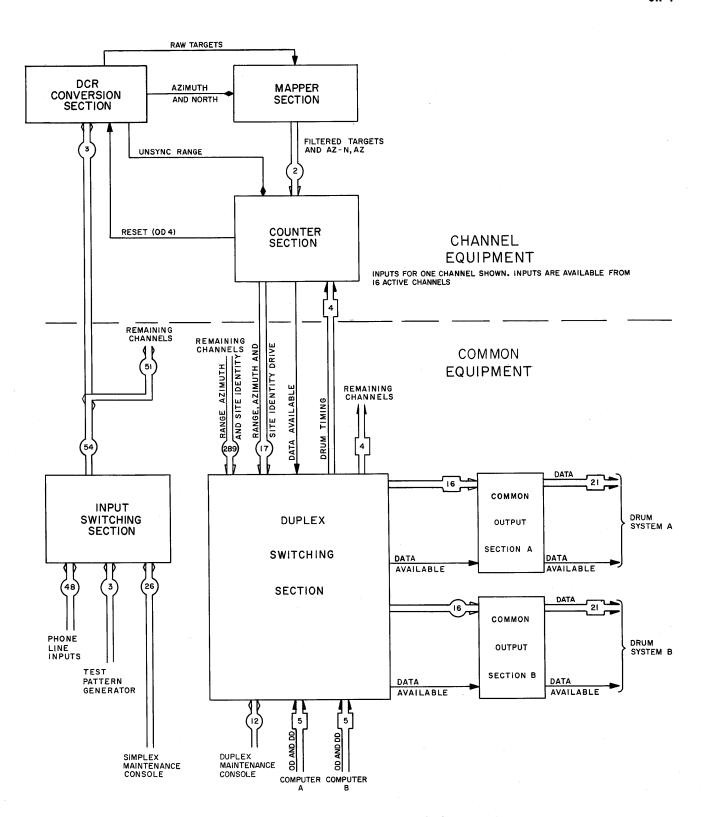

| 4-5         | GFI Element, Simplified Block Diagram                                                           | 120       |

| 4–6         | Gap-Filler Input Control Panels                                                                 | 122       |

| <b>4</b> —7 | Input Data Switching, Simplified Logic Diagram                                                  | 123       |

| 4-8         | Spare Channel Switching                                                                         | 124       |

| 4–9         | GFI Channel, Simplified Block Diagram                                                           | 127       |

| 4–10        | GFI Data Conversion Receiver Circuit, Simplified Logic Diagram                                  | 128       |

| 4-11        | GFI Data Conversion Receiver, Timing Chart                                                      | 129       |

| 4-12        | GFI Range Synchronizer, Simplified Logic Diagram                                                | 130       |

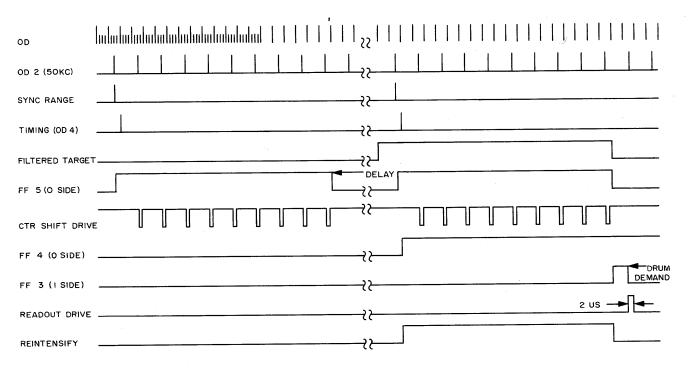

| 4–13        | Counter-Shifting and Readout Control, Simplified Logic Diagram                                  |           |

| 4-14        | Counter-Shifting and Readout Control, Timing Chart                                              |           |

| Figure      | Title                                                              | Page |

|-------------|--------------------------------------------------------------------|------|

| 4-15        | Core Counters and Registers, Simplified Logic Diagram              | 134  |

| 4–16        | Drum Demand and Data Available Switching Circuit                   |      |

| 4-17        | Site Identity Switching, Channels 1 and 2                          | 137  |

| 4-18        | Site Identity Switching for Spare Channels                         | 138  |

| 4-19        | Data Switching                                                     | 139  |

| 4-20        | GFI Common Section, Simplified Block Diagram                       | 141  |

| 4-21        | Common Timing and Pulse Distribution                               | 142  |

| 4-22        | Site Identity Generator, Simplified Logic Diagram                  | 143  |

| 4-23        | Common Output Circuit                                              | 144  |

| 4-24        | GFI Mapper, Simplified Block Diagram                               | 148  |

| 4–25        | Azimuth Synchronizer, Simplified Logic Diagram                     | 149  |

| 4–26        | North Synchronizer, Simplified Block Diagram                       | 150  |

| 4-27        | Yoke Drive Brake and Differential, Schematic Diagram               | 152  |

| 4-28        | Relative Drum Head Positions                                       | 153  |

| 4–29        | Azimuth Protection, Simplified Logic Diagram                       | 154  |

| 4-30        | North Azimuth Protection and Separation, Simplified  Logic Diagram | 156  |

| 4-31        | Sweep and Intensification Circuits, Simplified Logic Diagram       | 156  |

| 4-32        | Photo Pickup, Simplified Logic Diagram                             | 157  |

| 4-33        | Start and Alarm Circuit, Simplified Logic Diagram                  | 158  |

| 5-1         | Crosstelling Between Centrals                                      | 161  |

| 5-2         | XTL Element, Unit 32                                               | 162  |

| 5-3         | Crosstell Message in Drum System                                   | 164  |

| 5-4         | Crosstell Element, Block Diagram                                   | 165  |

| 5-5         | Crosstell Panels, Simplex Maintenance Console                      | 166  |

| 5-6         | Input Data Switching                                               | 168  |

| <b>5</b> —7 | Spare Channel Switching                                            | 169  |

| 5-8         | Constitution of                                                    | 171  |

| 5-9         | Constall Cl., 13, 10, 10, 10, 10, 10, 10, 10, 10, 10, 10           | 172  |

| 5-10        | Data Commenters and C. 1. C. 17. LT. 1. D.                         | 174  |

| 5-11        | Deta Comment 10 1 1 1 1 1 1 1 1                                    | 175  |

| 5-12        | Data Distributor, Simplified Logic Diagram                         |      |

| 5-13        | D. D. H. M. O.                                                     | 178  |

| Figure | Title                                                                            | Page |

|--------|----------------------------------------------------------------------------------|------|

| 5-14   | Buffer Storage Registers, Simplified Logic Diagram                               | 179  |

| 5-15   | Core Shift Pulse Generator and Fast Shift Generator,<br>Simplified Logic Diagram | 180  |

| 5–16   | Core Shift Pulse Generator and Fast Shift Generator, Timing Chart                | 181  |

| 5—17   | Twenty-Five Core Counter, Simplified Logic Diagram                               | 182  |

| 5-18   | Main Storage Registers, Simplified Logic Diagram                                 | 183  |

| 5-19   | Main Storage Register Word, Simplified Logic Diagram                             | 184  |

| 5-20   | Main Storage Register Shift Control, Simplified Logic Diagram                    | 185  |

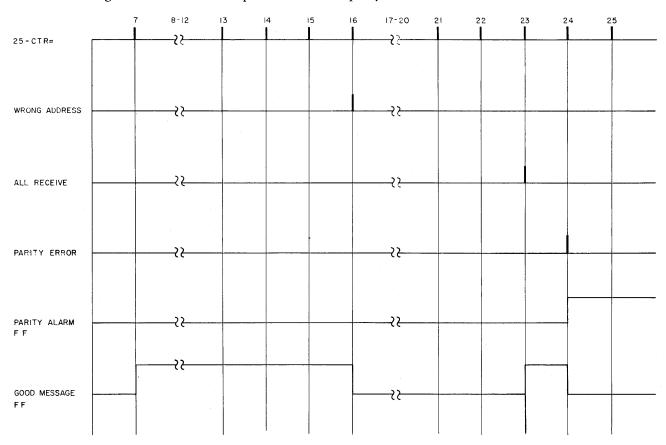

| 5-21   | Address Check, Simplified Logic Diagram                                          | 186  |

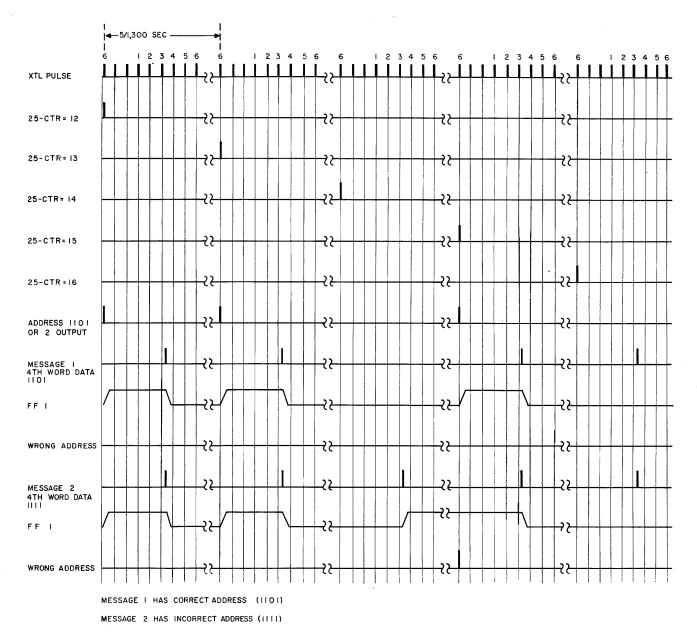

| 5-22   | Address Check, Timing Chart                                                      | 187  |

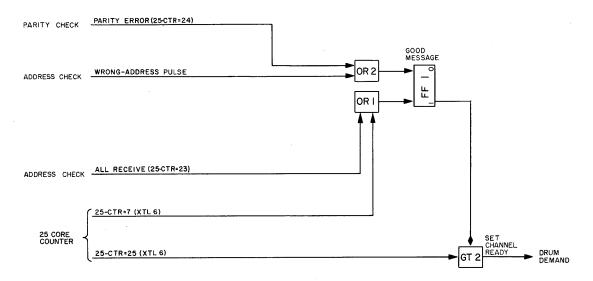

| 5-23   | Parity Check, Simplified Logic Diagram                                           | 188  |

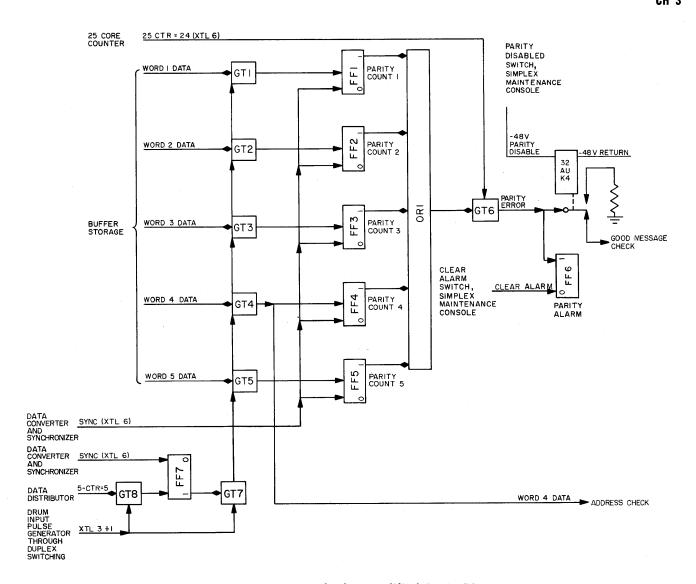

| 5-24   | Good Message Check, Simplified Logic Diagram                                     | 188  |

| 5-25   | Good Message Check, Timing Chart                                                 | 189  |

| 5-26   | Drum Demand Circuit, Simplified Logic Diagram                                    | 190  |

| 5-27   | Drum Demand Circuit, Timing Chart                                                | 191  |

| 5-28   | Main Storage Registers Readout Control, Simplified  Logic Diagram                | 192  |

| 5-29   | Main Storage Registers Readout Control, Timing Chart                             | 193  |

| 5-30   | Main Storage Readout Protection, Simplified Logic Diagram                        | 194  |

| 5-31   | Message Word Parity Transfer, Simplified Logic Diagram                           | 194  |

| 5-32   | A and B Signal Relays Driving Circuit, Simplified Logic Diagram                  | 196  |

| 5-33   | Core Data Transfer, Simplified Schematic Diagram                                 | 196  |

| 5-34   | Write Level Transfer, Spare Channel Switching,<br>Simplified Schematic Diagram   | 199  |

| 5-35   | Drum Demand Switching, Channels 1 and 2, Simplified Schematic Diagram            | 200  |

| 5-36   | Drum Input (Common) Section, Simplified Block Diagram                            | 204  |

| 5-37   | Consolidation of Message Bit Lines                                               | 206  |

| 5-38   | Clock Circuit, Simplified Logic Diagram                                          | 208  |

| 5-39   | Clock Stepping and Synchronizing, Timing Chart                                   | 209  |

| 5-40   | Clock Binary Counter, 1's Test and Parity Generator, Timing Chart                | 210  |

| 5-41   | Site Identity Generator, Simplified Logic Diagram                                | 212  |

| Figure | Title                                                                                                  | Page |

|--------|--------------------------------------------------------------------------------------------------------|------|

| 5-42   | Clock and Site Identity Parity Circuit, Simplified Logic Diagram                                       | 213  |

| 5-43   | Drum Parity Circuit, Simplified Logic Diagram                                                          | 214  |

| 5-44   | Drum Parity, Timing Chart                                                                              | 215  |

| 5-45   | Drum Write Circuit, Simplified Logic Diagram                                                           | 216  |

| 5-46   | Drum Write Circuit, Timing Chart                                                                       | 217  |

| 5-47   | Typical XTL Amplifies, Simplified Logic Diagram                                                        | 218  |

| 5-48   | Pulse Generator, Simplified Logic Diagram                                                              | 219  |

| 5-49   | Pulse Generator, Timing Chart                                                                          | 221  |

| 5-50   | Readout Alarm Circuit, Simplified Logic Diagram                                                        | 222  |

| 6–1    | Test Pattern Generator TS-923/FSQ                                                                      | 224  |

| 6–2    | LRI TPG Control Panel, Simplex Maintenance Console                                                     | 225  |

| 6-3    | LRI TPG Control Panel, Unit 92                                                                         | 225  |