# **DISTRIBUTED LOGIC CORPORATION**

# MODEL DU132 TAPE COUPLER INSTRUCTION MANUAL

\$4. XI.

# MODEL DU132 MAGNETIC TAPE COUPLER INSTRUCTION MANUAL

July 1987

DISTRIBUTED LOGIC CORPORATION 1555 S. Sinclair Street P.O. Box 6270 Anaheim. California 92806 Telephone: (714) 937-5700 Telex: 6836051 Copyright ©1984 by Distributed Logic Corporation

Printed in the United States of America

$\langle i \rangle$

# TABLE OF CONTENTS

# Section

| 1 | DESCRIPTION                                                    |

|---|----------------------------------------------------------------|

| - | INTRODUCTION 1-1                                               |

|   | GENERAL DESCRIPTION                                            |

|   | UNIBUS Interface                                               |

|   | Interrupt                                                      |

|   | Formatter Interface                                            |

|   |                                                                |

|   | Tape System General Specifications   1-6     Data Format   1-6 |

|   | Data Format                                                    |

|   | Media Characteristics                                          |

|   | Register Address                                               |

|   | Computer I/O Interface                                         |

|   | Coupler/Formatter Interface                                    |

|   | Packaging                                                      |

|   | Documentation                                                  |

|   | Power                                                          |

|   | Environment                                                    |

|   | Shipping Weight                                                |

|   |                                                                |

| 2 | INSTALLATION                                                   |

|   | Introduction                                                   |

|   | Installation                                                   |

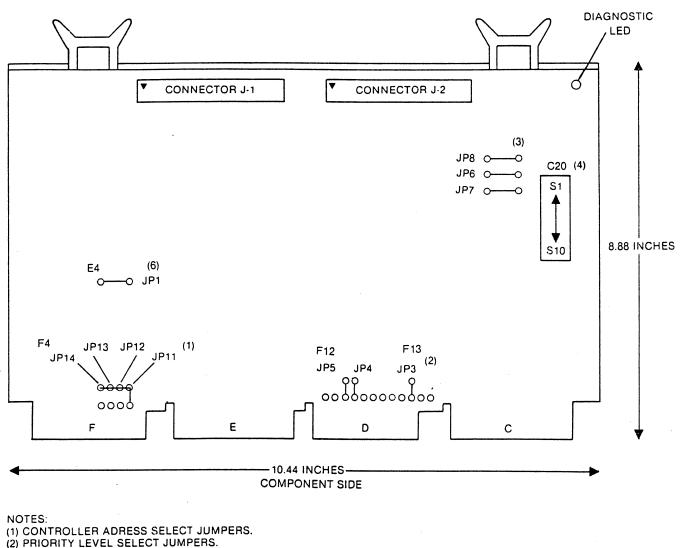

|   | Configuring the Coupler                                        |

|   | Controller Address Select Jumper                               |

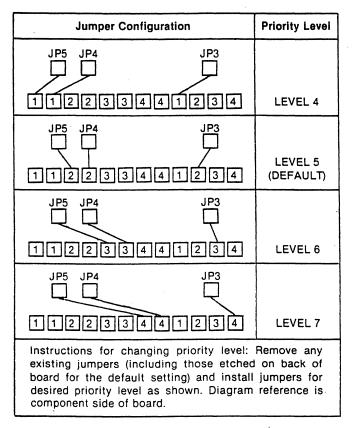

|   | Priority Level Select Jumpers                                  |

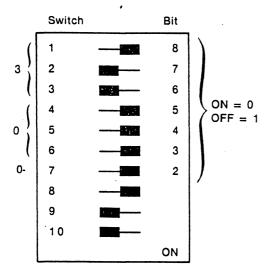

|   | Selection of Tape Drive Density or Speed                       |

|   | Interrupt Vector, DMA Burst Size, Drive Quantity Select        |

|   | Interrupt Vector Address                                       |

|   | DMA Burst Size                                                 |

|   | Number of Tape Drives                                          |

|   | Floating Vector Addresses                                      |

|   |                                                                |

| 3 | OPERATION                                                      |

|   | Introduction                                                   |

|   | Tape Format                                                    |

|   | Booting From Magnetic Tapes                                    |

|   |                                                                |

| 4 | PROGRAMMING 4-1                                                |

|   | Programming Definitions                                        |

|   | Program Sequences                                              |

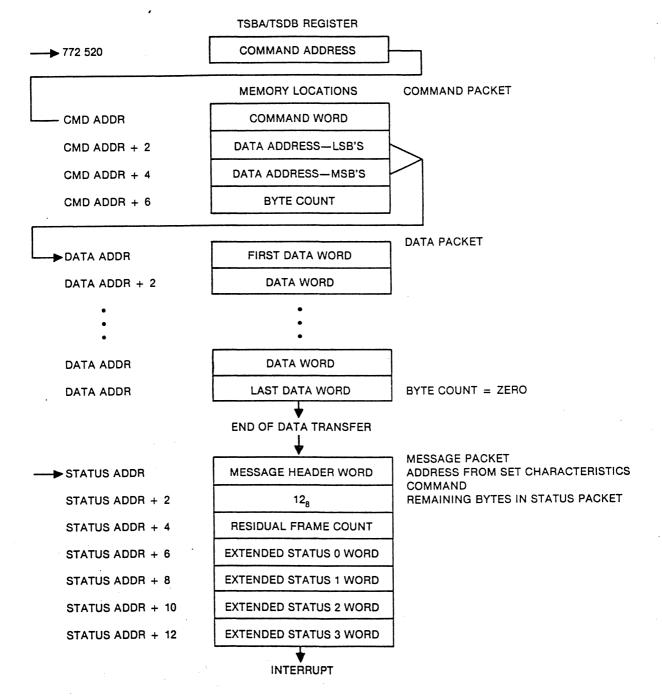

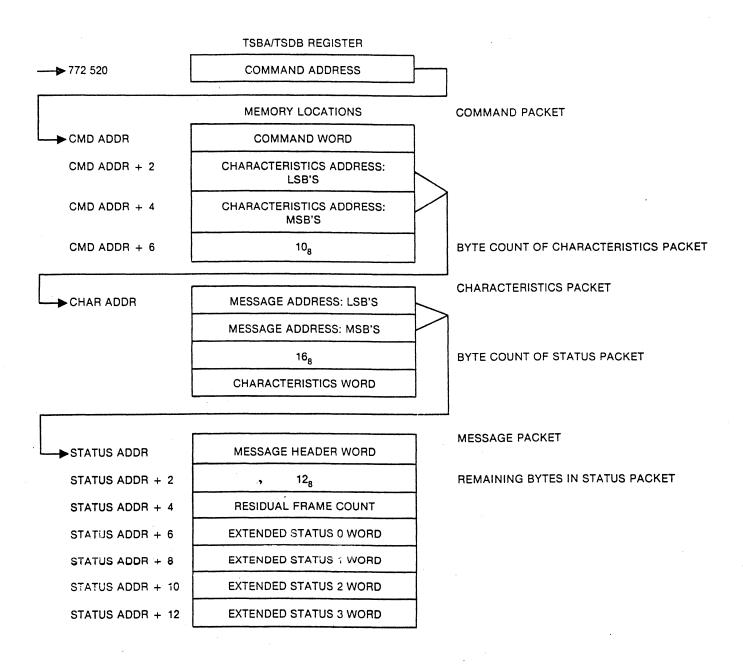

|   | Registers and Packets                                          |

|   | Bus Address Register (TSBA)                                    |

|   | Data Buffer Register (TSDB)                                    |

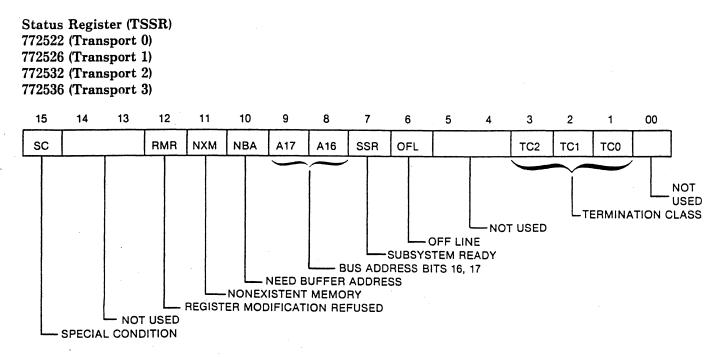

|   | Status Register (TSSR) 4-4                                     |

|   | Command Packet: Command Word Data Buffer Address, Byte Count   |

|   | Short Command Packet: Command Word and Count                   |

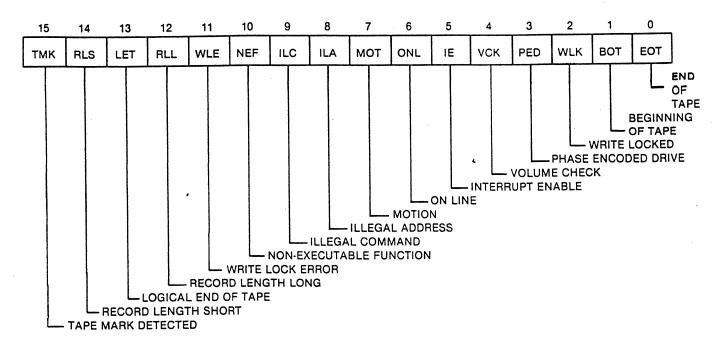

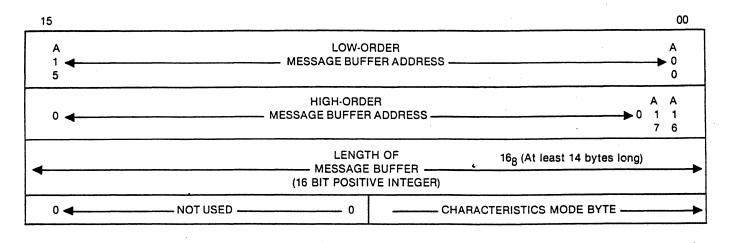

|   | Message Packet Header Word                                     |

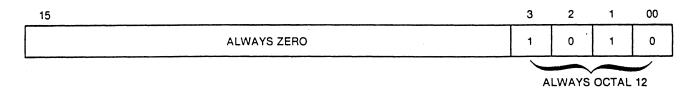

|   | Message Packet Word Count                                      |

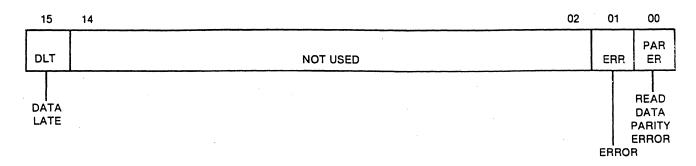

|   | Extended Status (XSTAT0) Word 4-10                             |

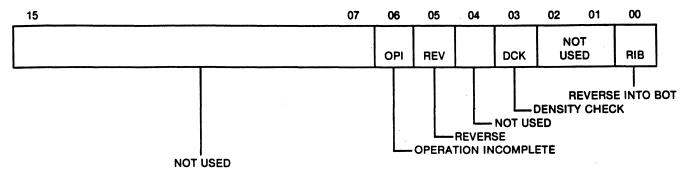

|   | Extended Status 1 (XSTAT1) Word                                |

|   |                                                                |

# TABLE OF CONTENTS (Continued)

| $\sim$ | . •  |             |

|--------|------|-------------|

| 50     | et 1 | on          |

| 20     |      | <b>U</b> 11 |

5

$\sqrt{1}$

•

| Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                              | System Troubleshooting<br>er Symptoms<br>cal Layout<br>Listing<br>y<br>ral Description<br>nputer Interface<br>rroprocessor<br>ipheral Interface<br>tional Description<br>nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 7)<br>IBUS Status and Control Logic (Sheet 5)<br>IBUS Status and Control Logic (Sheet 5)<br>IBUS Status and Control Logic (Sheet 2, 3, 4)<br>croprocessor<br>X 8 RAM (Sheet 13)<br>X 8-Bit ROM (Sheet 13)<br>ntroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUS (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>proce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | Characteristic Packet                        | • |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------------------------------|---|--|

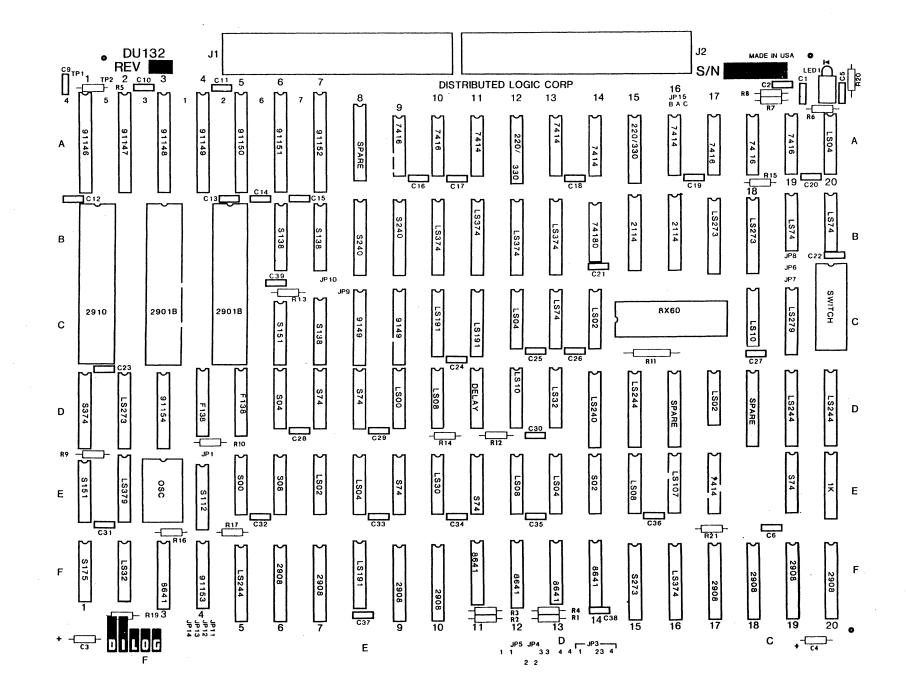

| Coupler Symptoms<br>Physical Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ler Symptoms<br>cal Layout<br>Listing<br>y<br>ral Description<br>mputer Interface<br>croprocessor<br>ipheral Interface<br>tional Description<br>mputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X 8 RAM (Sheet 13)<br>troller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>provector Address Register (Sheet 8)<br>provector Address Register (Sheet 8)<br>prove Logic (Sheet 12)<br>ipheral Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                              |   |  |

| Physical Layout<br>Term Listing<br>Theory<br>General Description<br>Computer Interface<br>Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheet 5)<br>UNIBUS Status and Control Logic (Sheet 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>201B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                  | cal Layout<br>Listing<br>y<br>ral Description<br>mputer Interface<br>irroprocessor<br>ipheral Interface<br>tional Description<br>mputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X 8 RAM (Sheet 13)<br>troller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>mrce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |                                              |   |  |

| Term Listing<br>Theory<br>General Description<br>Computer Interface<br>Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 7)<br>UNIBUS Status and Control Logic (Sheet 5)<br>UNIBUS Status and Control Logic (Sheet 5, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8 RAM (Sheet 13)<br>256 X 8 Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12) | Listing<br>y<br>ral Description<br>nputer Interface<br>roprocessor<br>ipheral Interface<br>tional Description<br>nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X & RAM (Sheet 13)<br>iX & Bit ROM (Sheet 13)<br>htroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>mrce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                              |   |  |

| Theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                              |   |  |

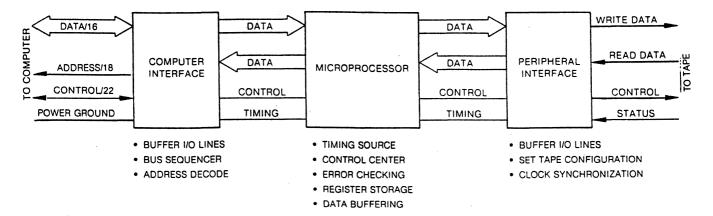

| General Description<br>Computer Interface<br>Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8 BAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                       | ral Description<br>mputer Interface<br>proprocessor<br>ipheral Interface<br>tional Description<br>mputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>proprocessor<br>X & RAM (Sheet 13)<br>X & BAM (Sheet 13)<br>At roller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>provector Address Register (Sheet 8)<br>proce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                              |   |  |

| Computer Interface<br>Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                          | nputer Interface<br>croprocessor<br>ipheral Interface<br>tional Description<br>nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheet 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X & RAM (Sheet 13)<br>X & BAM (Sheet 13)<br>X & BAM (Sheet 13)<br>htroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>htrol Processor (Sheet 9)<br>htrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>irce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                              |   |  |

| Microprocessor<br>Peripheral Interface<br>Functional Description<br>Computer Interface<br>Address Decode Logic (Sheet 2)<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                              | roprocessor<br>ipheral Interface<br>tional Description<br>nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X 8 RAM (Sheet 13)<br>X 8-Bit ROM (Sheet 13)<br>htroller Test Logic (Sheet 8)<br>B Microprocessor ALUs (Sheet 11)<br>htrol Processor (Sheet 9)<br>htrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>arce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | G |                                              |   |  |

| Peripheral Interface .<br>Functional Description .<br>Computer Interface .<br>Address Decode Logic (Sheet 2) .<br>UNIBUS Address Register Receiver/Drivers (Sheets 5, 6) .<br>UNIBUS Data Register Receiver/Drivers (Sheet 7) .<br>UNIBUS Control Receiver/Drivers (Sheet 5) .<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4) .<br>Microprocessor .<br>256 X 8 RAM (Sheet 13) .<br>256 X 8-Bit ROM (Sheet 13) .<br>256 X 8-Bit ROM (Sheet 13) .<br>2901B Microprocessor ALUs (Sheet 11) .<br>Control Processor (Sheet 9) .<br>Control Store (Sheet 10) .<br>Microvector Address Register (Sheet 8) .<br>Source, Destination, and Pulse Decode Logic (Sheet 12) .                                                                                                                                   | <pre>ipheral Interface<br/>tional Description<br/>mputer Interface<br/>dress Decode Logic (Sheet 2)<br/>IBUS Address Register Receiver/Drivers (Sheet 5, 6)<br/>IBUS Data Register Receiver/Drivers (Sheet 7)<br/>IBUS Control Receiver/Drivers (Sheet 5)<br/>IBUS Status and Control Logic (Sheet 2, 3, 4)<br/>croprocessor<br/>X 8 RAM (Sheet 13)<br/>X 8-Bit ROM (Sheet 13)<br/>throller Test Logic (Sheet 8)<br/>DIB Microprocessor ALUs (Sheet 11)<br/>throl Processor (Sheet 9)<br/>throl Store (Sheet 10)<br/>crovector Address Register (Sheet 8)<br/>Direc, Destination, and Pulse Decode Logic (Sheet 12)<br/>ipheral Interface<br/>pe Drive Configuration Switches (Sheet 13)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                              |   |  |

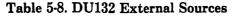

| Functional Description         Computer Interface         Address Decode Logic (Sheet 2)         UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)         UNIBUS Data Register Receiver/Drivers (Sheet 7)         UNIBUS Control Receiver/Drivers (Sheet 5)         UNIBUS Status and Control Logic (Sheets 2, 3, 4)         Microprocessor         256 X 8 RAM (Sheet 13)         256 X 8-Bit ROM (Sheet 13)         Controller Test Logic (Sheet 8)         2901B Microprocessor ALUs (Sheet 11)         Control Store (Sheet 10)         Microvector Address Register (Sheet 8)         Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                 | tional Description<br>nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X & RAM (Sheet 13)<br>X & BAI (Sheet 13)<br>X & Bit ROM (Sheet 13)<br>ntroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>nrce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                              |   |  |

| Computer InterfaceAddress Decode Logic (Sheet 2)UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)UNIBUS Data Register Receiver/Drivers (Sheet 7)UNIBUS Control Receiver/Drivers (Sheet 5)UNIBUS Status and Control Logic (Sheets 2, 3, 4)Microprocessor256 X 8 RAM (Sheet 13)256 X 8-Bit ROM (Sheet 13)Controller Test Logic (Sheet 8)2901B Microprocessor ALUs (Sheet 11)Control Store (Sheet 10)Microvector Address Register (Sheet 8)Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                     | nputer Interface<br>dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X & RAM (Sheet 13)<br>X & BAIM (Sheet 13)<br>A & Bit ROM (Sheet 13)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>arce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                              |   |  |

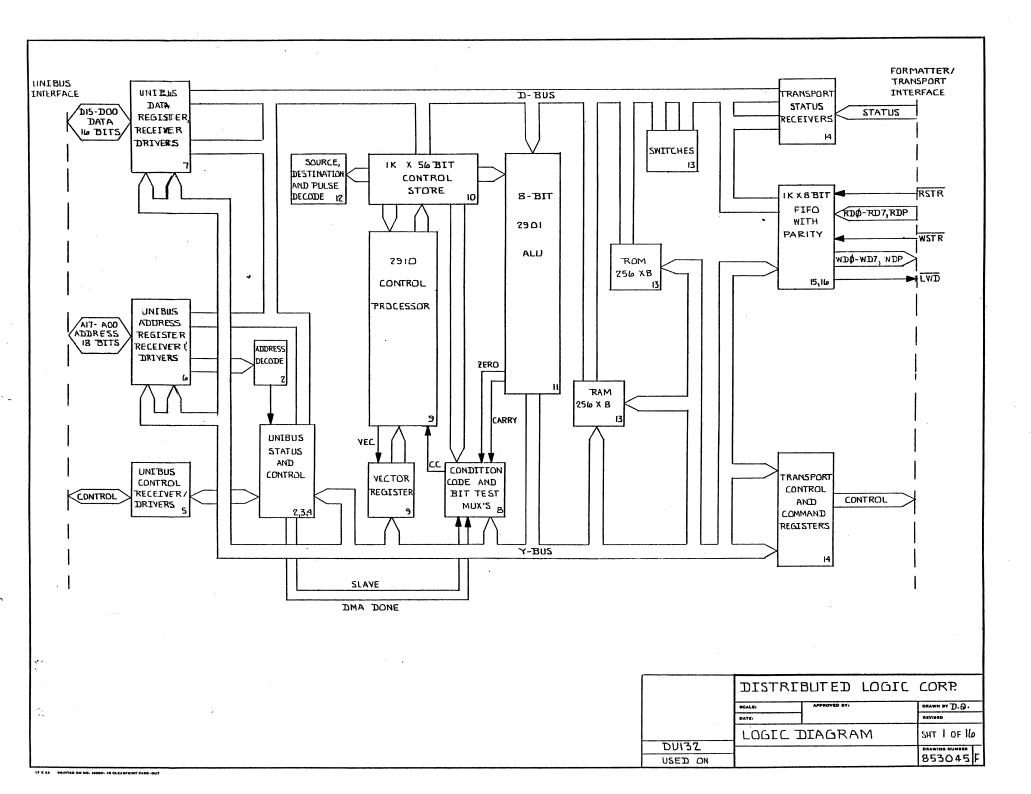

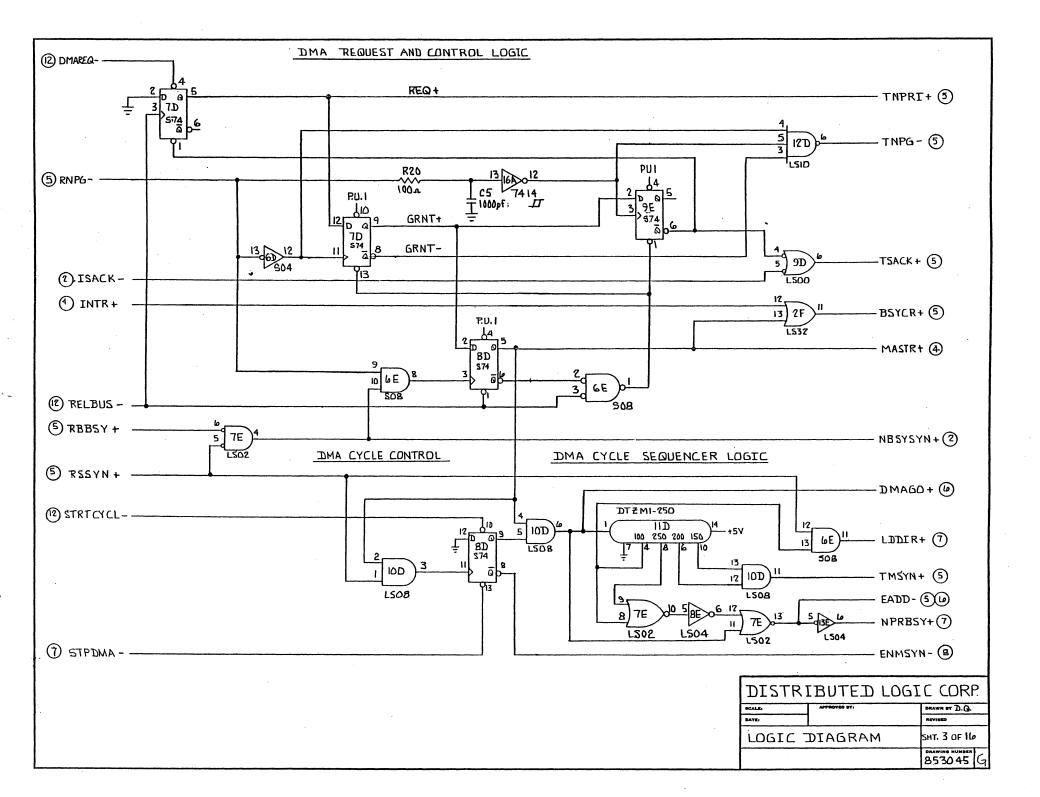

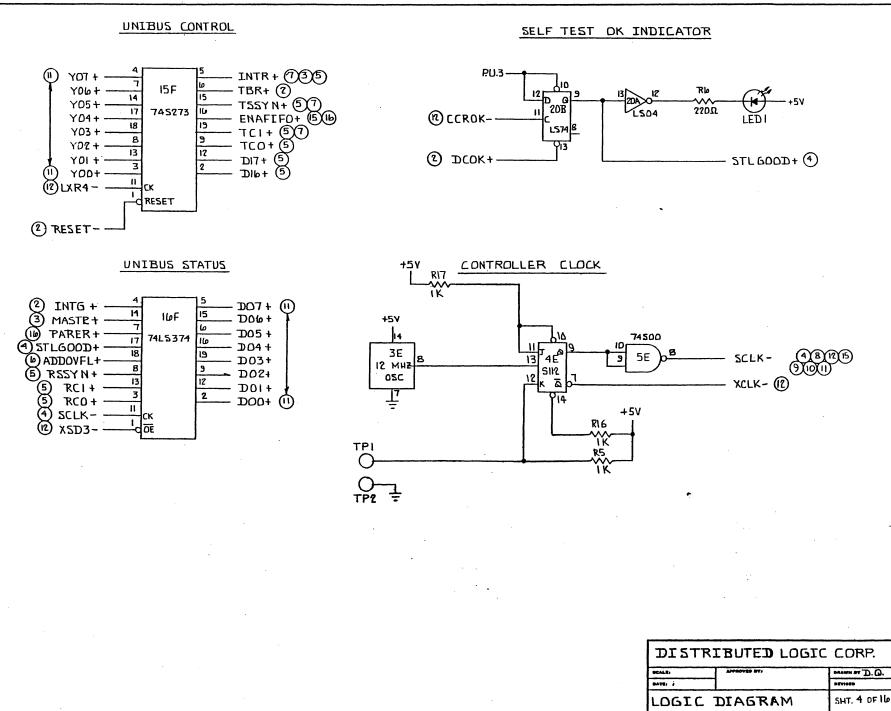

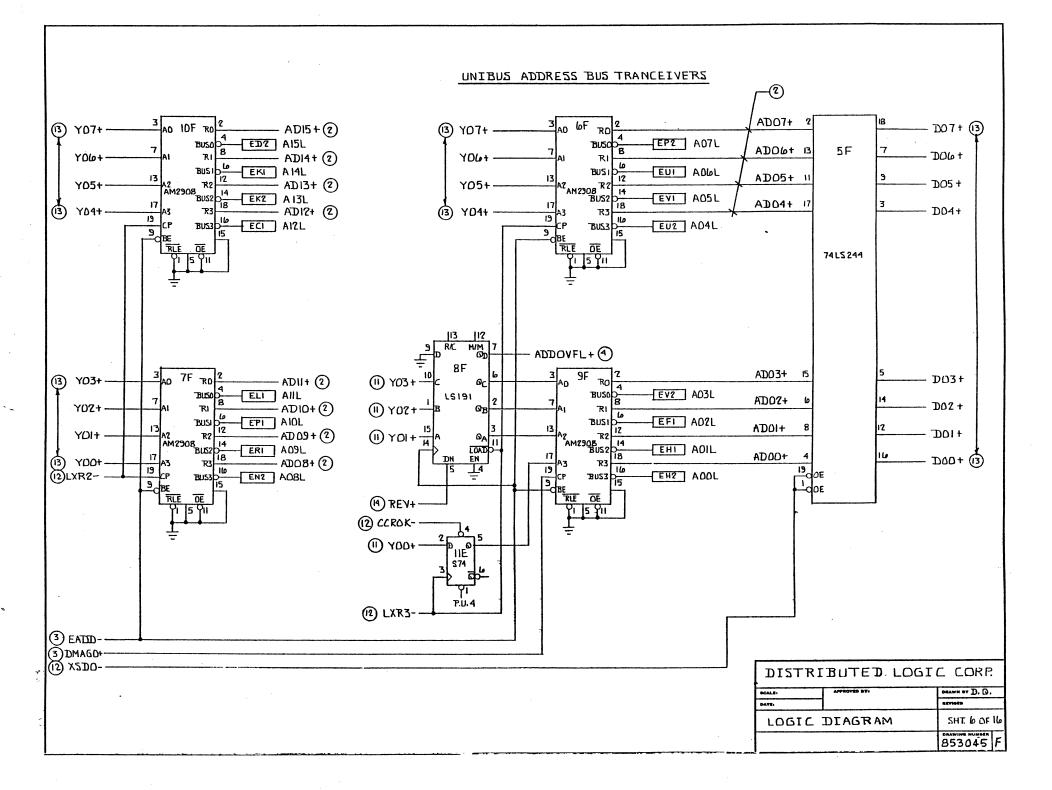

| Address Decode Logic (Sheet 2)UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)UNIBUS Data Register Receiver/Drivers (Sheet 7)UNIBUS Control Receiver/Drivers (Sheet 5)UNIBUS Status and Control Logic (Sheets 2, 3, 4)Microprocessor256 X 8 RAM (Sheet 13)256 X 8-Bit ROM (Sheet 13)256 X 8-Bit ROM (Sheet 13)Controller Test Logic (Sheet 8)2901B Microprocessor ALUs (Sheet 11)Control Store (Sheet 9)Control Store (Sheet 10)Microvector Address Register (Sheet 8)Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                      | dress Decode Logic (Sheet 2)<br>IBUS Address Register Receiver/Drivers (Sheets 5, 6)<br>IBUS Data Register Receiver/Drivers (Sheet 7)<br>IBUS Control Receiver/Drivers (Sheet 5)<br>IBUS Status and Control Logic (Sheets 2, 3, 4)<br>croprocessor<br>X 8 RAM (Sheet 13)<br>X 8-Bit ROM (Sheet 13)<br>htroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>htrol Processor (Sheet 9)<br>htrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>htroe Logic (Sheet 12)<br>pheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | F |                                              |   |  |

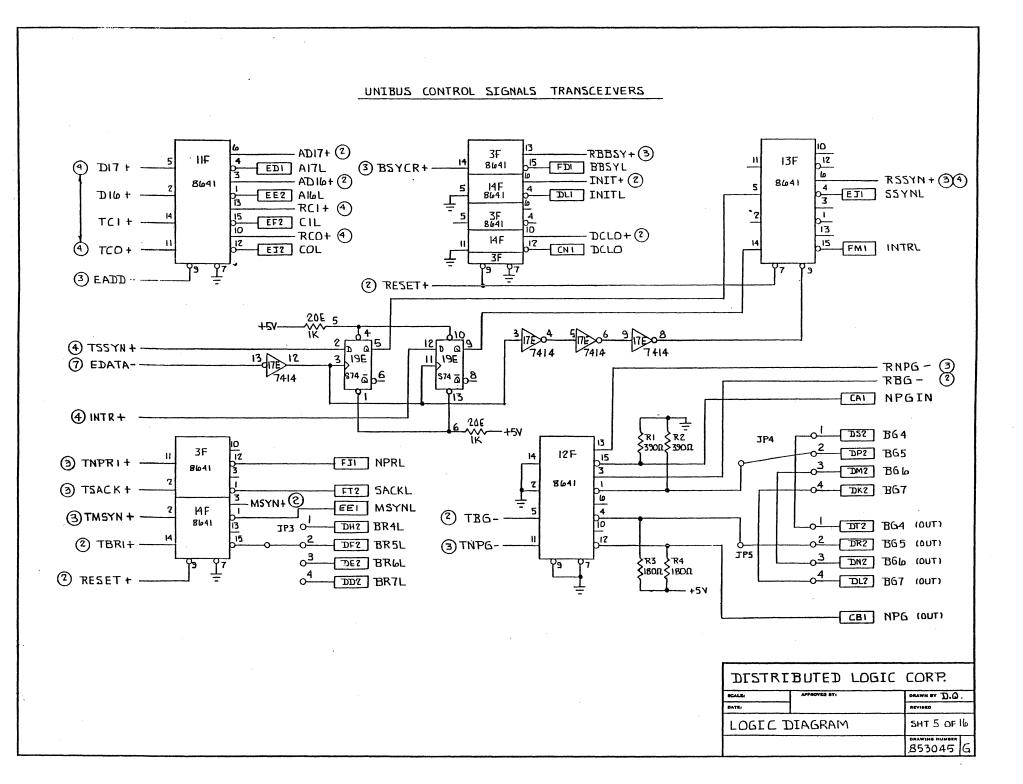

| UNIBUS Address Register Receiver/Drivers (Sheets 5, 6)UNIBUS Data Register Receiver/Drivers (Sheet 7)UNIBUS Control Receiver/Drivers (Sheet 5)UNIBUS Status and Control Logic (Sheets 2, 3, 4)Microprocessor256 X 8 RAM (Sheet 13)256 X 8-Bit ROM (Sheet 13)Controller Test Logic (Sheet 8)2901B Microprocessor ALUs (Sheet 11)Control Store (Sheet 10)Microvector Address Register (Sheet 8)Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                     | IBUS Address Register Receiver/Drivers (Sheet 5, 6)         IBUS Data Register Receiver/Drivers (Sheet 7)         IBUS Control Receiver/Drivers (Sheet 5)         IBUS Status and Control Logic (Sheet 5)         IBUS Status and Control Logic (Sheets 2, 3, 4)         croprocessor         X 8 RAM (Sheet 13)         at 8 Bit ROM (Sheet 13)         bt 7 Build Status (Sheet 13)         bt 8 Bit ROM (Sheet 13)         bt 9 B Microprocessor ALUs (Sheet 11)         bt 10 Processor (Sheet 9)         bt 10 Store (Sheet 10)         crovector Address Register (Sheet 8)         bt 11 pheral Interface         be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                              |   |  |

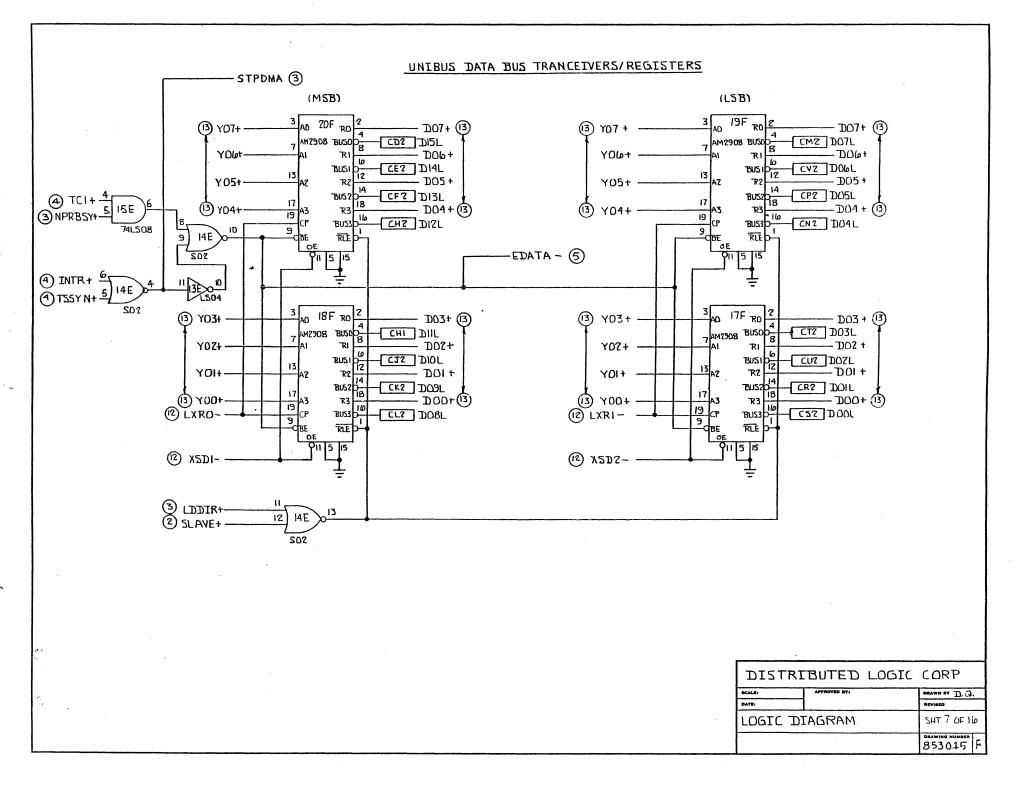

| UNIBUS Data Register Receiver/Drivers (Sheet 7)<br>UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                    | IBUS Data Register Receiver/Drivers (Sheet 7)         IBUS Control Receiver/Drivers (Sheet 5)         IBUS Status and Control Logic (Sheets 2, 3, 4)         croprocessor         X & RAM (Sheet 13)         X & 8-Bit ROM (Sheet 13)         htroller Test Logic (Sheet 8)         O1B Microprocessor ALUs (Sheet 11)         htrol Processor (Sheet 9)         htrol Store (Sheet 10)         crovector Address Register (Sheet 8)         irce, Destination, and Pulse Decode Logic (Sheet 12)         op Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                              |   |  |

| UNIBUS Control Receiver/Drivers (Sheet 5)<br>UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                       | IBUS Control Receiver/Drivers (Sheet 5)         IBUS Status and Control Logic (Sheets 2, 3, 4)         croprocessor         5 X 8 RAM (Sheet 13)         5 X 8-Bit ROM (Sheet 13)         attraction of the state of the stat                                                                                                                                                                                                                                                                                                          |   |                                              |   |  |

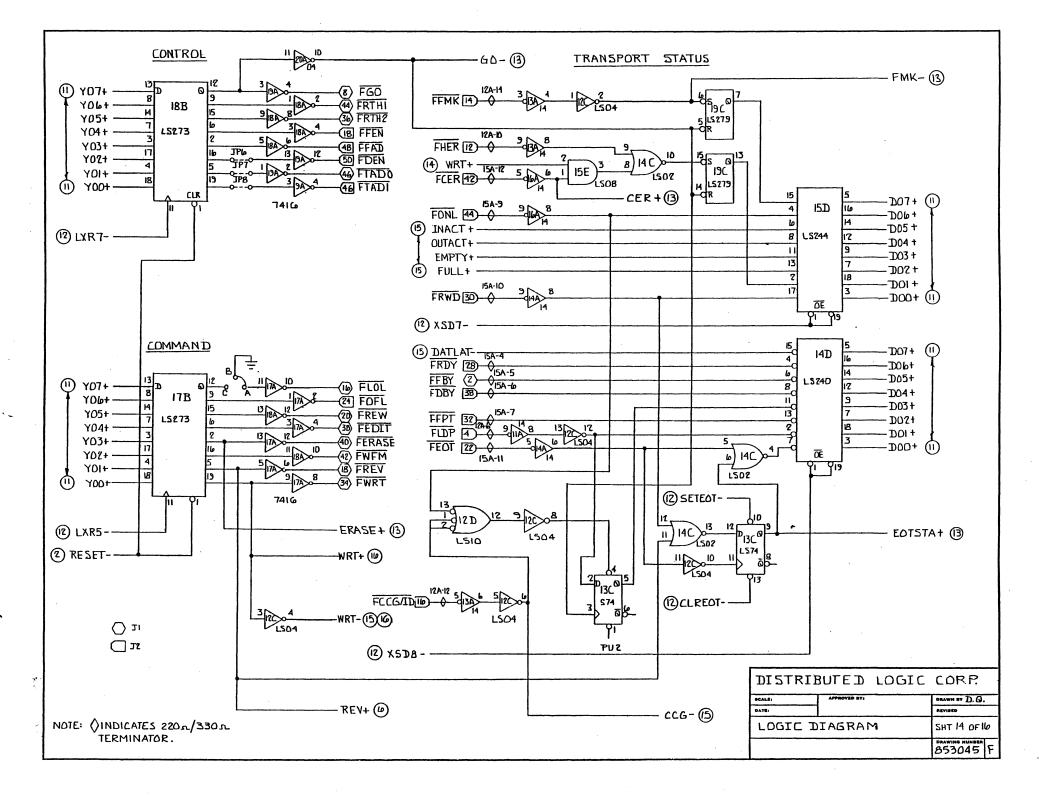

| UNIBUS Status and Control Logic (Sheets 2, 3, 4)<br>Microprocessor<br>256 X 8 RAM (Sheet 13)<br>256 X 8-Bit ROM (Sheet 13)<br>Controller Test Logic (Sheet 8)<br>2901B Microprocessor ALUs (Sheet 11)<br>Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                    | IBUS Status and Control Logic (Sheets 2, 3, 4)         croprocessor         5 X 8 RAM (Sheet 13)         5 X 8-Bit ROM (Sheet 13)         ntroller Test Logic (Sheet 8)         01B Microprocessor ALUs (Sheet 11)         ntrol Processor (Sheet 9)         ntrol Store (Sheet 10)         crovector Address Register (Sheet 8)         nrce, Destination, and Pulse Decode Logic (Sheet 12)         ripheral Interface         per Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                              |   |  |

| Microprocessor256 X 8 RAM (Sheet 13)256 X 8-Bit ROM (Sheet 13)256 X 8-Bit ROM (Sheet 13)Controller Test Logic (Sheet 8)2901B Microprocessor ALUs (Sheet 11)Control Processor (Sheet 9)Control Store (Sheet 10)Microvector Address Register (Sheet 8)Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Croprocessor<br>X 8 RAM (Sheet 13)<br>X 8 RAM (Sheet 13)<br>Troller Test Logic (Sheet 13)<br>D1B Microprocessor ALUs (Sheet 11)<br>D1B Microprocessor (Sheet 9)<br>D1B Microprocessor (Sheet 10)<br>D1B Microprocessor (Sheet 12)<br>D1B Microprocessor (Sheet 12)<br>D1B Microprocessor (Sheet 12)<br>D1B Microprocessor (Sheet 13)<br>D1B |   | UNIBUS Control Receiver/Drivers (Sheet 5)    |   |  |

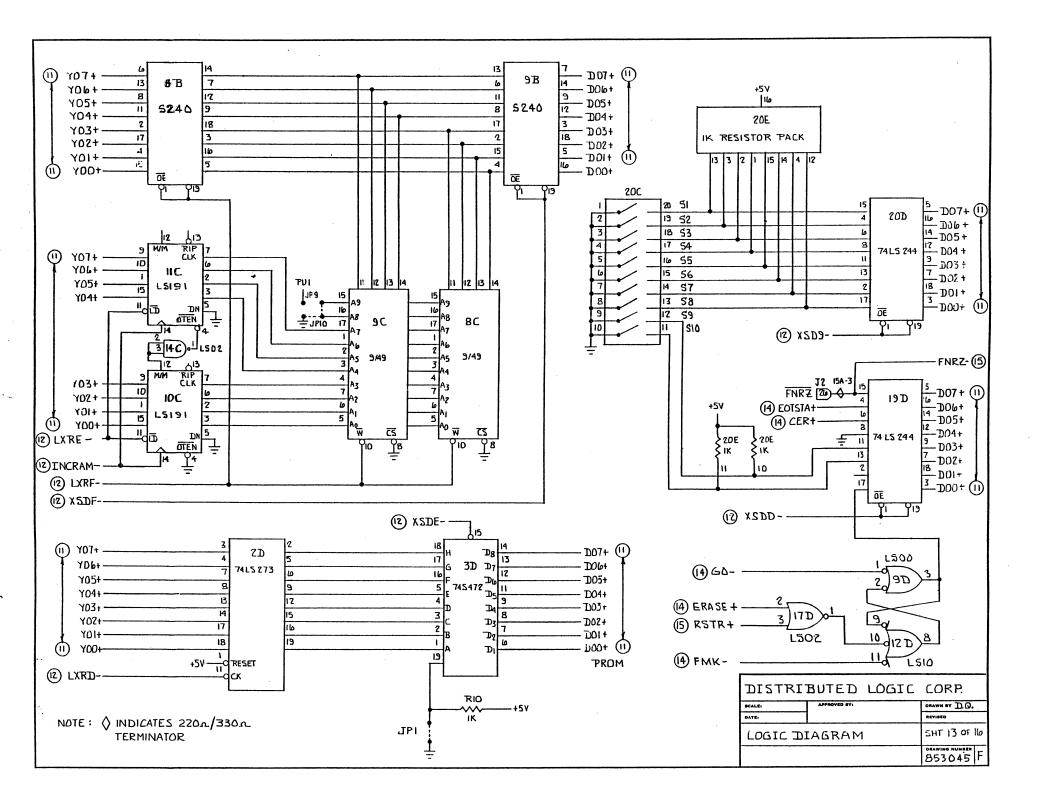

| 256 X 8 RAM (Sheet 13)         256 X 8-Bit ROM (Sheet 13)         Controller Test Logic (Sheet 8)         2901B Microprocessor ALUs (Sheet 11)         Control Processor (Sheet 9)         Control Store (Sheet 10)         Microvector Address Register (Sheet 8)         Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3 X 8 RAM (Sheet 13)         5 X 8-Bit ROM (Sheet 13)         htroller Test Logic (Sheet 8)         01B Microprocessor ALUs (Sheet 11)         htrol Processor (Sheet 9)         htrol Store (Sheet 10)         crovector Address Register (Sheet 8)         ince, Destination, and Pulse Decode Logic (Sheet 12)         ipheral Interface         be Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                              |   |  |

| 256 X 8-Bit ROM (Sheet 13)         Controller Test Logic (Sheet 8)         2901B Microprocessor ALUs (Sheet 11)         Control Processor (Sheet 9)         Control Store (Sheet 10)         Microvector Address Register (Sheet 8)         Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | X 8-Bit ROM (Sheet 13)<br>htroller Test Logic (Sheet 8)<br>DIB Microprocessor ALUs (Sheet 11)<br>htrol Processor (Sheet 9)<br>htrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>htroe Destination, and Pulse Decode Logic (Sheet 12)<br>pheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | •                                            |   |  |

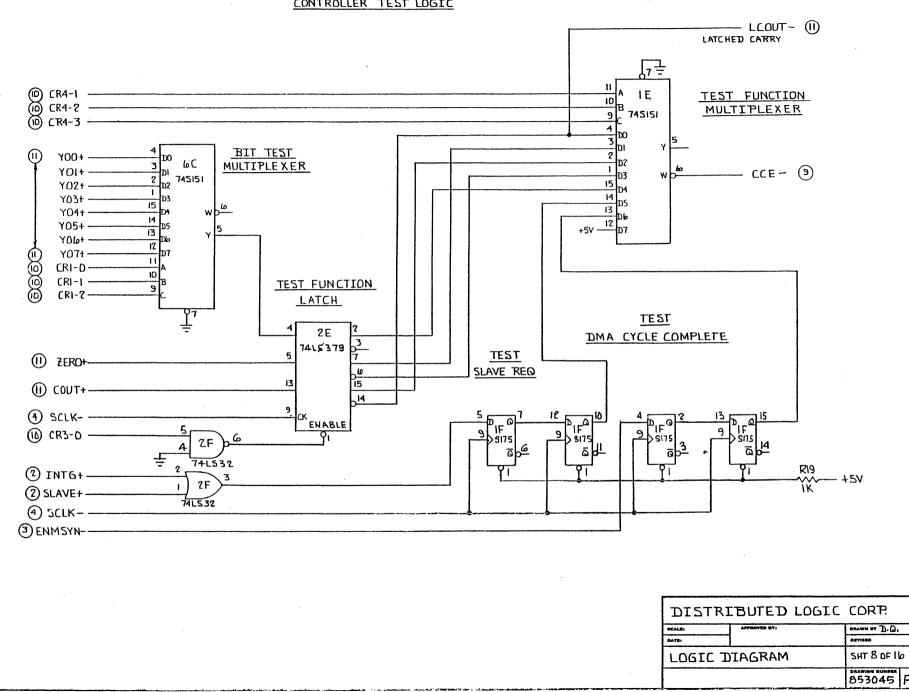

| Controller Test Logic (Sheet 8).<br>2901B Microprocessor ALUs (Sheet 11).<br>Control Processor (Sheet 9).<br>Control Store (Sheet 10).<br>Microvector Address Register (Sheet 8).<br>Source, Destination, and Pulse Decode Logic (Sheet 12).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | htroller Test Logic (Sheet 8)<br>1B Microprocessor ALUs (Sheet 11)<br>htrol Processor (Sheet 9)<br>htrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>htroe Destination, and Pulse Decode Logic (Sheet 12)<br>pheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                              |   |  |

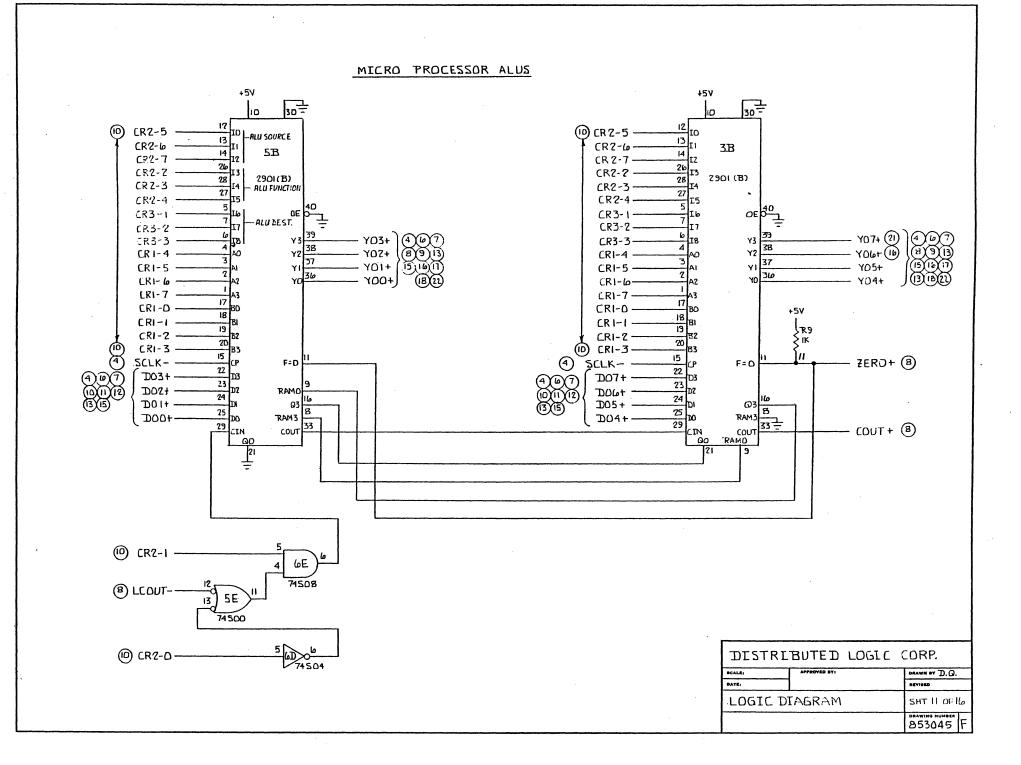

| 2901B Microprocessor ALUs (Sheet 11)         Control Processor (Sheet 9)         Control Store (Sheet 10)         Microvector Address Register (Sheet 8)         Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D1B Microprocessor ALUs (Sheet 11)         ntrol Processor (Sheet 9)         ntrol Store (Sheet 10)         crovector Address Register (Sheet 8)         urce, Destination, and Pulse Decode Logic (Sheet 12)         ripheral Interface         pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |                                              |   |  |

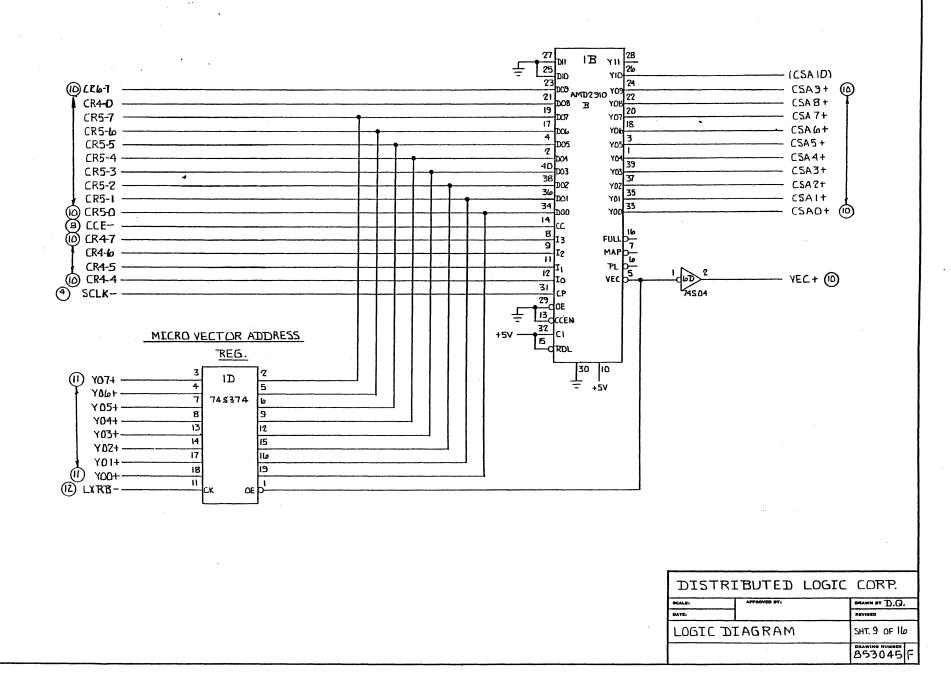

| Control Processor (Sheet 9)<br>Control Store (Sheet 10)<br>Microvector Address Register (Sheet 8)<br>Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ntrol Processor (Sheet 9)<br>ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>arce, Destination, and Pulse Decode Logic (Sheet 12)<br>ripheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                              |   |  |

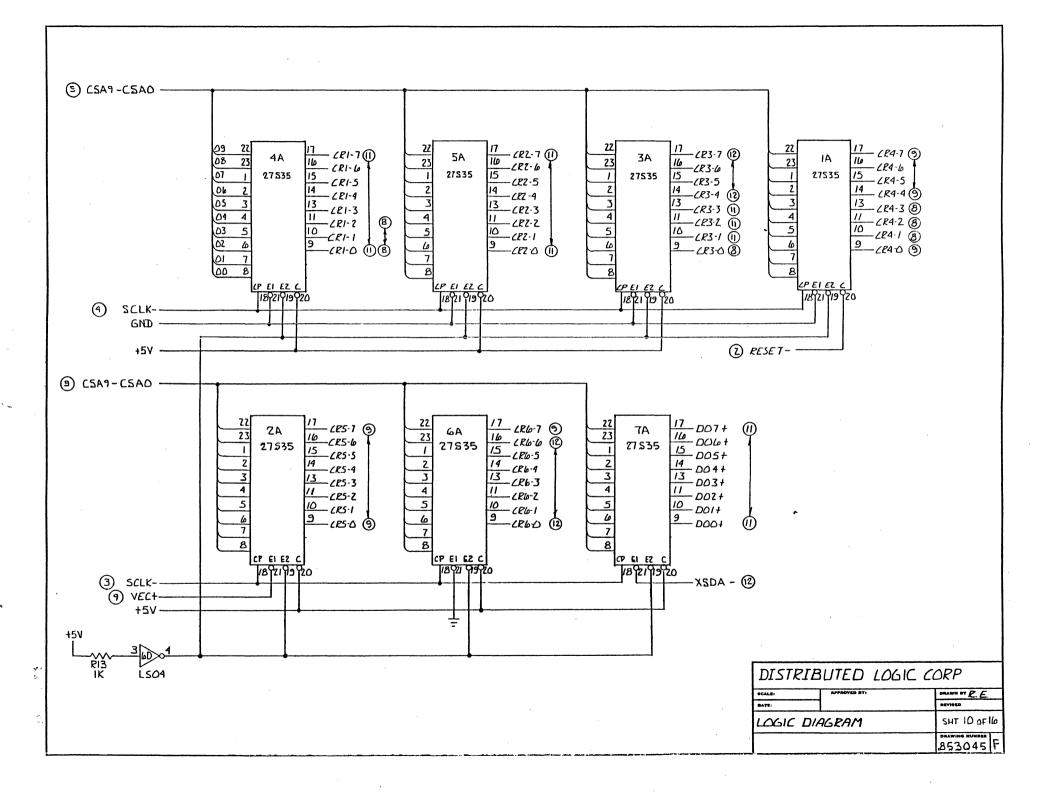

| Control Store (Sheet 10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ntrol Store (Sheet 10)<br>crovector Address Register (Sheet 8)<br>nrce, Destination, and Pulse Decode Logic (Sheet 12)<br>ipheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                              |   |  |

| Microvector Address Register (Sheet 8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | crovector Address Register (Sheet 8)<br>arce, Destination, and Pulse Decode Logic (Sheet 12)<br>pheral Interface<br>pe Drive Configuration Switches (Sheet 13)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                              |   |  |

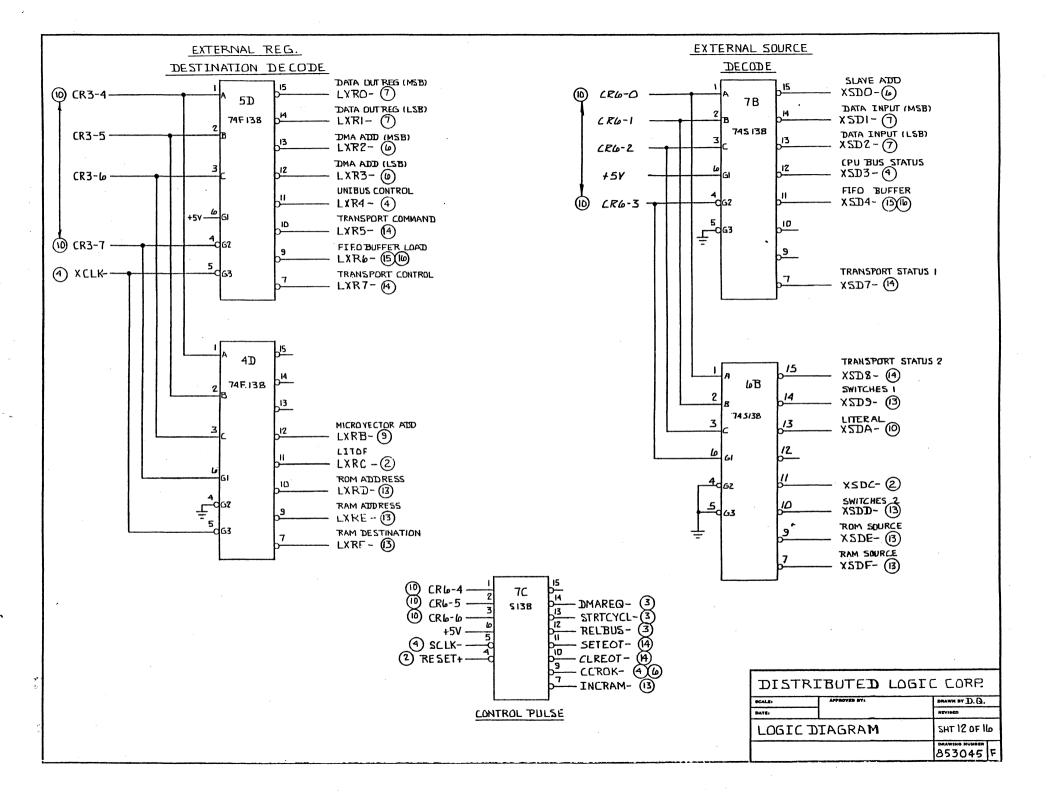

| Source, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | rrce, Destination, and Pulse Decode Logic (Sheet 12)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |                                              |   |  |