## AN/AYK-14(V)

# NAVY STANDARD AIRBORNE COMPUTER TECHNICAL DESCRIPTION

#### **RESTRICTIVE NOTICE**

This manual is intended to inform the reader regarding the general construction, operational characteristics, and capabilities of the AN/AYK-14 computer. It should not, however, be considered as an equipment specification, and Control Data in no way warrants the accuracy or completeness of the manual for procurement purposes. Products and services described herein are available for sale only to the federal government of the United States of America or its designees.

## **AN/AYK-14 (V)**

## TECHNICAL DESCRIPTION

#### TABLE OF CONTENTS

| SUMMARY                                                                                                                               | 1                    |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| BACKGROUND                                                                                                                            | 1                    |

| GENERAL CHARACTERISTICS                                                                                                               | 1                    |

| Processing Subsystem                                                                                                                  | 5                    |

| Intermodule Communication                                                                                                             | 5                    |

| Memory Subsystem                                                                                                                      | 8                    |

| I/O Subsystem.                                                                                                                        | 8                    |

| Power Subsystem                                                                                                                       | 8                    |

| Chassis Subsystem                                                                                                                     | 9                    |

| Environment                                                                                                                           | 9                    |

| Configuration Capability                                                                                                              | 9                    |

| PHYSICAL CHARACTERISTICS                                                                                                              | 14                   |

| RELIABILITY                                                                                                                           | 14                   |

| MAINTAINABILITY                                                                                                                       | 15                   |

| PERFORMANCE                                                                                                                           | 15                   |

| MODULE DESCRIPTIONS                                                                                                                   | 17                   |

| General Processor Module (GPM) Processor Support Module (PSM) Extended Arithmetic Unit (EAU) Input/Output Processor (IOP) I/O Modules | 17<br>17<br>18<br>18 |

|                                                                                                                                       | 18                   |

| Discrete Interface Module (DIM)                                                                                                       | 19                   |

| Serial Interface Module (SIM)                                                                                                         | 19                   |

| RS-232-C Serial Interface Module (RIM).                                                                                               | 20                   |

| PROTEUS Interface Module (PIM)                                                                                                        | 20                   |

| Bus Extender Module (BEM).                                                                                                            | 21                   |

| Memory Modules                                                                                                                        | 21                   |

| Memory Control Module (MCM)                                                                                                           | 21                   |

| Core Memory Module (CMM)                                                                                                              | 21                   |

| Semiconductor Memory Module (SMM)                                                                                                     | 21                   |

| Read/Write Expandable Module (RXM)                                                                                                    | 22                   |

| Power Converter Module (PCM)                                                                                                          | 23                   |

#### TABLE OF CONTENTS (CONT.)

| SUPPORT EQUIPMENT                                                                                                                                                                                | 23                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| Computer Control Unit (CCU)                                                                                                                                                                      |                                        |

| FUNCTIONAL ARCHITECTURE                                                                                                                                                                          | 26                                     |

| Memory Architecture                                                                                                                                                                              | 26                                     |

| Memory Interfaces Direct Memory Access (DMA) Capability Memory Addressing. Memory Parity Memory Protection Assigned Memory Addresses Non-Destructive Read-Only (NDRO) Memory                     | 26<br>26<br>26<br>26<br>26<br>27<br>27 |

| CPU Architecture                                                                                                                                                                                 | 27                                     |

| General Registers. Program Address Register Real-Time Clock (RTC) and Monitor (MON) Clock Features Power Failure Protection Feature Status Registers. Instructions.                              | 27<br>28<br>28<br>28<br>28<br>30       |

| Instruction Addressing                                                                                                                                                                           | 31<br>31                               |

| Floating Point Operands                                                                                                                                                                          | 38<br>39                               |

| Interrupt Processing                                                                                                                                                                             | 40                                     |

| I/O Channel Structure                                                                                                                                                                            | 41                                     |

| I/O Channel Programs and Chaining I/O Control Memory Serial I/O Module (1553A) Channel Operation Discrete Interface Channel Operation RS-232-C Channel Operation NTDS Parallel Channel Operation | 41<br>42<br>43<br>44<br>45<br>46       |

| NTDS Serial Channel Operation                                                                                                                                                                    | 47<br>48<br>49                         |

|                                                                                                                                                                                                  | JI                                     |

#### TABLE OF CONTENTS (CONT.)

| Operato                                                             | or Interface and Control                                                                                                                                                                                    | . 51                                                 |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| SOFTWARE                                                            | AND FIRMWARE                                                                                                                                                                                                | . 52                                                 |

| In-Fligh SRA Fa CCU Pro L/V Pro CCU an Microco Microco 480/14 MTASS | mware  It Performance Monitoring (IFPM).  It Isolation Diagnostic.  Ogram  Ogram  Id L/V Diagnostics  Ode Cross-Assembler  Ode Simulator.  Executive  TASS Host Computers  Id Real-Time Executive (SDEX/M). | . 52<br>. 53<br>. 53<br>. 53<br>. 53<br>. 54<br>. 54 |

|                                                                     | ONS                                                                                                                                                                                                         |                                                      |

|                                                                     | LIST OF TABLES                                                                                                                                                                                              |                                                      |

| Table No.                                                           | Title                                                                                                                                                                                                       | Page                                                 |

| 1<br>2<br>3                                                         | AN/AYK-14(V) Computer System Specifications and Features                                                                                                                                                    | . 6                                                  |

| 4                                                                   | AN/AYK-14 Performance on Instruction Mix                                                                                                                                                                    | 16                                                   |

| 5<br>6                                                              | PCM Capacities                                                                                                                                                                                              |                                                      |

| 7                                                                   | AN/AYK-14(V) Instruction Repertoire                                                                                                                                                                         |                                                      |

| 8                                                                   | Legend for Instruction Repertoire                                                                                                                                                                           | 37                                                   |

| 9                                                                   | Interrupt Priority                                                                                                                                                                                          |                                                      |

| 10                                                                  | AN/AYK-14 Clock Speed Selection                                                                                                                                                                             |                                                      |

| 11                                                                  | PROTEUS Channel Sequences                                                                                                                                                                                   |                                                      |

| 12                                                                  | CPU/IOP Functions.                                                                                                                                                                                          |                                                      |

| 13                                                                  | IFPM Modules                                                                                                                                                                                                |                                                      |

| 14                                                                  | Functions Checked by BIT Equipment                                                                                                                                                                          |                                                      |

| 15                                                                  | Module Requirements of Selected Computer Applications                                                                                                                                                       | 55                                                   |

#### LIST OF ILLUSTRATIONS

| Figure No. | Titles                                                 | Page |

|------------|--------------------------------------------------------|------|

| 1          | AN/AYK-14(V) Modules and Enclosure                     |      |

| 2          | AN/AYK-14(V) System Elements                           |      |

| 3          | AN/AYK-14(V) Configurator — XN-1 Layout                | . 10 |

| 3          | AN/AYK-14(V) Configurator — XN-5 Layout                |      |

| 3          | AN/AYK-14(V) Configurator — XN-3 Layout                | . 12 |

| 4          | Module Outlines                                        | . 13 |

| 5          | Minimum Configuration                                  | . 14 |

| 6          | Expanded Configuration                                 | . 14 |

| 7          | MIL-STD-1553A Word Formats                             | . 19 |

| 8          | MIL-STD-1553A Message Formats                          | . 19 |

| 9          | NTDS Slow, Fast, and ANEW Channel Interface            | . 20 |

| 10         | NTDS Serial Channel Interface and Message Format       | . 20 |

| 11         | RS-232-C Serial Channel Interface                      |      |

| 12         | PROTEUS Channel Pair                                   | . 21 |

| 13         | Interchangeable Core (Front) and Semiconductor (Rear)  |      |

|            | Memory Modules                                         | . 22 |

| 14         | Computer Control Unit (Front View)                     | . 24 |

| 15         | Computer Control Unit Block Diagram                    |      |

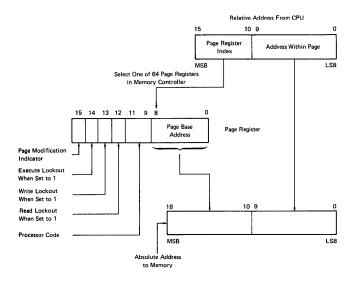

| 16         | Memory Address Generation                              | . 27 |

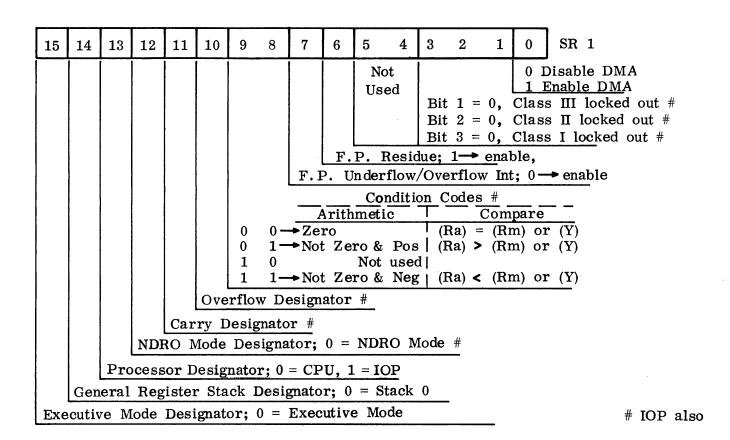

| 17         | Status Register Number 1 Format                        | . 29 |

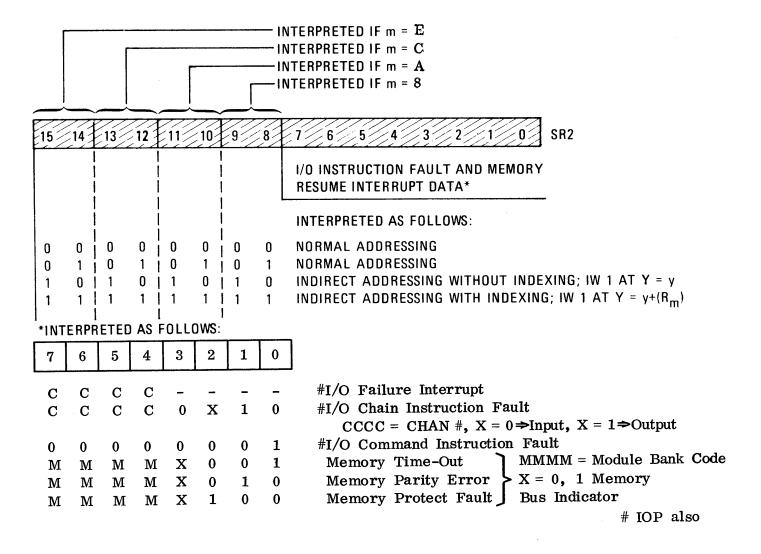

| 18         | Status Register Number 2 Format                        | . 30 |

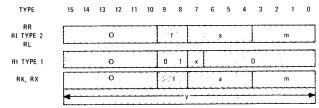

| 19         | Instruction Word Format                                | . 37 |

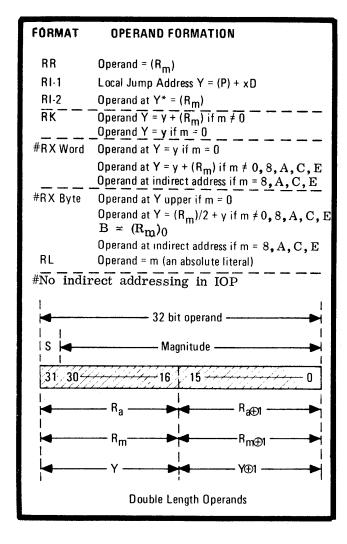

| 20         | Operand Formation                                      |      |

| 21         | Indirect Addressing                                    |      |

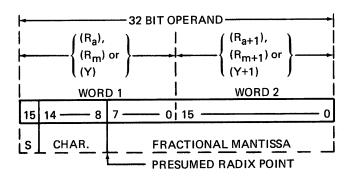

| 22         | Floating Point Format                                  | . 39 |

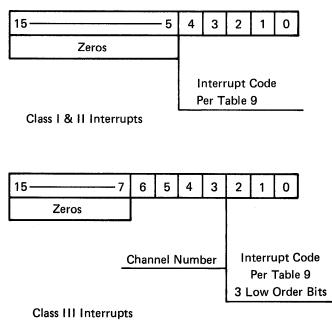

| 23         | Interrupt Entrance Address Index                       | . 40 |

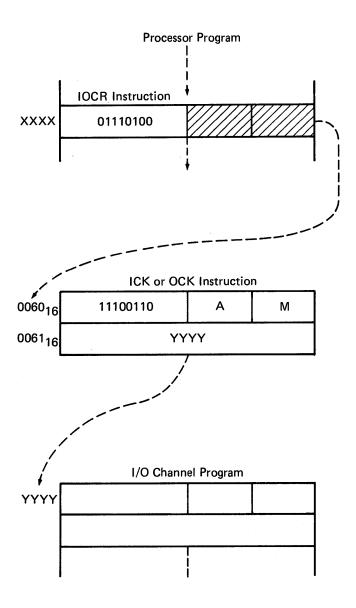

| 24         | I/O Channel Program Initiation                         | . 41 |

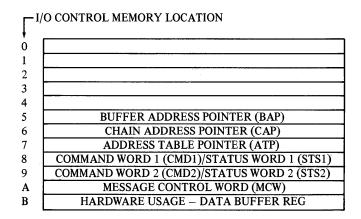

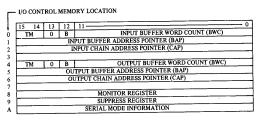

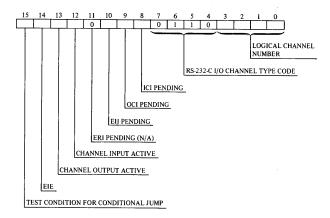

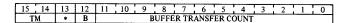

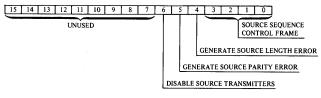

| 25         | SIM Control Memory Definition                          | . 42 |

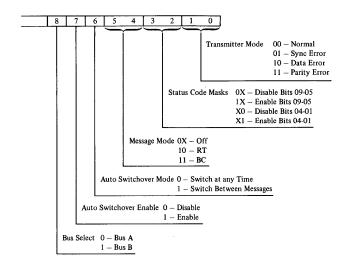

| 26         | SIM I/O Channel Message Control Word                   | . 43 |

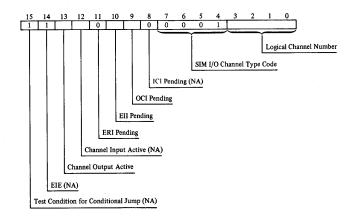

| 27         | SIM I/O Channel Status Word 0                          | . 43 |

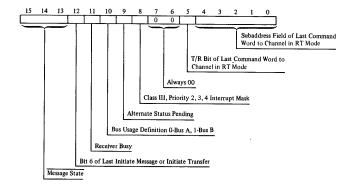

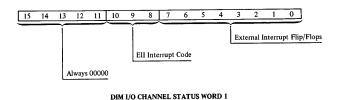

| 28         | SIM I/O Channel Status Word 1                          | . 44 |

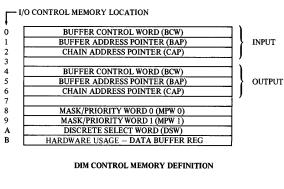

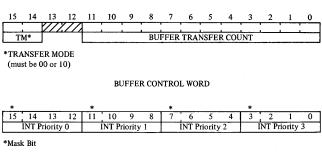

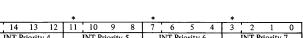

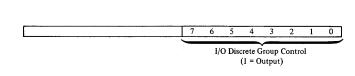

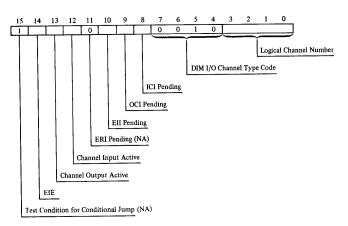

| 29         | DIM Control Memory Definition and Formats              | . 44 |

| 30         | DIM I/O Channel Status Words                           | . 45 |

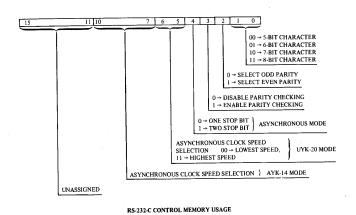

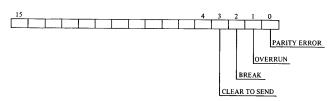

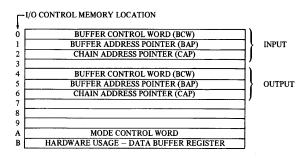

| 31         | RS-232-C Control Memory Usage                          | . 45 |

| 32         | RS-232-C I/O Channel Status and Interrupt Word Formats | . 46 |

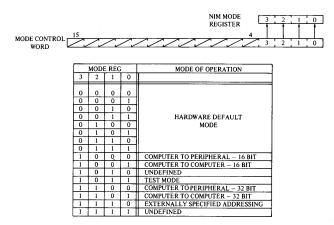

| 33         | NTDS Control Memory Usage                              | . 47 |

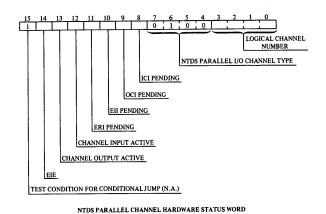

| 34         | NTDS Parallel I/O Status Words                         | . 48 |

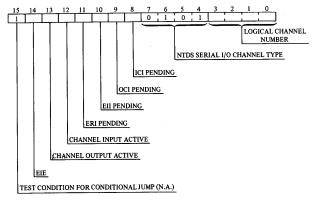

| 35         | NTDS Serial I/O Status Words                           |      |

| 36         | PROTEUS Message Formats                                |      |

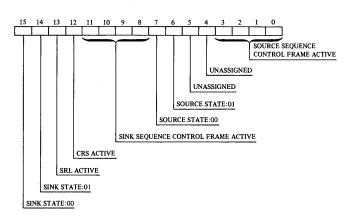

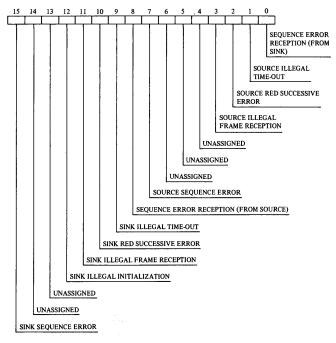

| 37         | PROTEUS Control Memory Usage                           |      |

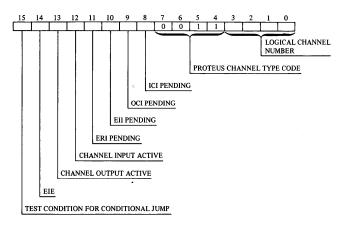

| 38         | PROTEUS Channel Status Words                           |      |

| 39         | Commonality of Avionics Processing Based on            |      |

|            | AN/AYK-14(V) Computer Family                           | . 56 |

### AN/AYK-14(V) TECHNICAL DESCRIPTION

#### SUMMARY

The AN/AYK-14(V) computer system is a family of microprogrammed computers designed to provide low-cost standard airborne computers applicable to a wide range of vehicles and missions. The AN/AYK-14(V) computers operate in MIL-E-5400 environments; however, the basic module design is also applicable to configurations for shipboard and land environments.

The AN/AYK-14(V) system architectural philosophy is based on the following key features:

- 1) The AN/AYK-14(V) architecture and instruction set is upward compatible with that of the AN/UYK-20, permitting the adaptation and use of existing AN/UYK-20 support software.

- 2) The hardware is functionally partitioned into pluggable modules. These modules are the standard building blocks used in configuring functionally large or small computers.

- 3) Intermodule communications are standardized via uniform internal bus structures to permit reconfiguration and new module addition without impact on the architecture.

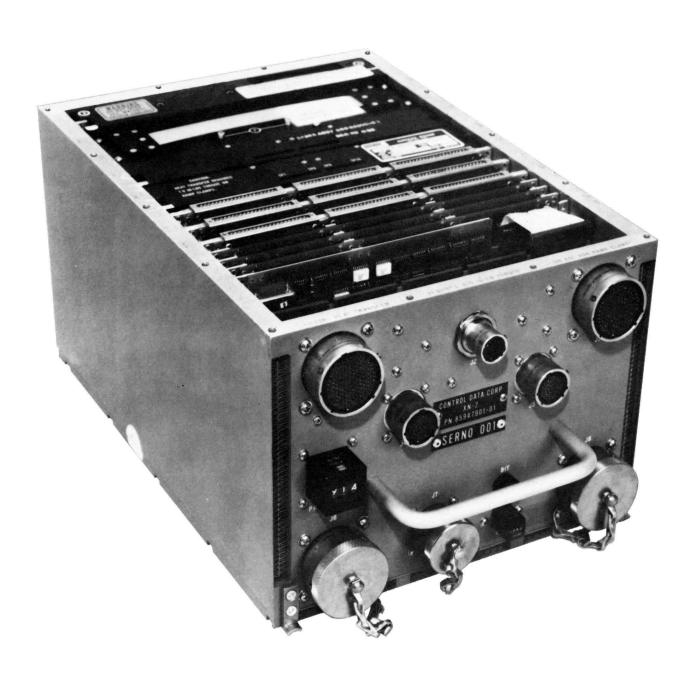

These combined features permit configuration of specific AN/AYK-14(V) computers to efficiently meet the processing requirements of a wide variety of military systems. Currently the AN/AYK-14(V) computer system provides 22 module types which can be configured in various combinations in three different chassis types. Configurations range from a two-module dedicated processor to multiple processor computers with up to 524,288 words of memory and with additional chassis, up to 16 I/O channels of various types. Figure 1 illustrates the hardware, including the functional modules and typical airborne type enclosure.

#### **BACKGROUND**

The AN/AYK-14(V) is designated as the U.S. Navy Standard Airborne Computer and is intended for broad applications to a wide range of airborne missions. The design selected by NAVAIR for the AN/AYK-14(V) is a subset of the recently developed CDC 480 computer family.

Initial applications under the AN/AYK-14(V) program include the two central computers on the F-18 fighter, the computer for the LAMPS MKIII, and eight other airborne applications. The AN/AYK-14(V) program provides for qualification, documentation, training, logistics support, and extensive software transferred from the AN/UYK-20 program.

#### GENERAL CHARACTERISTICS

The AN/AYK-14(V) is a variable configuration, general-purpose, 16-bit computer featuring a performance range of up to 675 KOPS (thousands of operations per second). The computer features a high degree of functional and mechanical modularity and is designed for flexible growth and extensive hardware commonality over a wide range of applications. The AN/AYK-14(V) architecture discernable to the user is not changed by modular hardware configuration changes, permitting common firmware and support software systems for all users. These design concepts are the key to providing a low-cost, versatile Navy standard airborne computer system. Table 1 summarizes the AN/AYK-14(V) specifications and features.

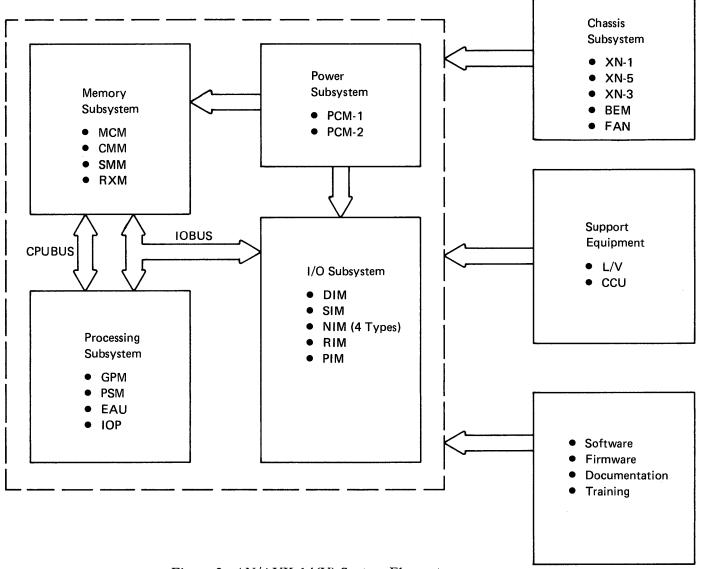

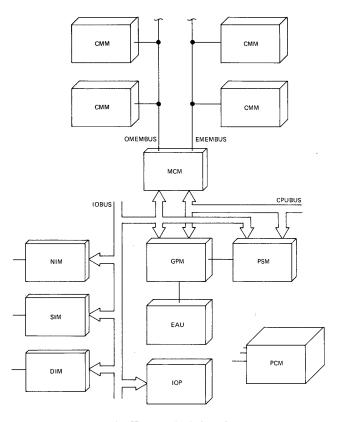

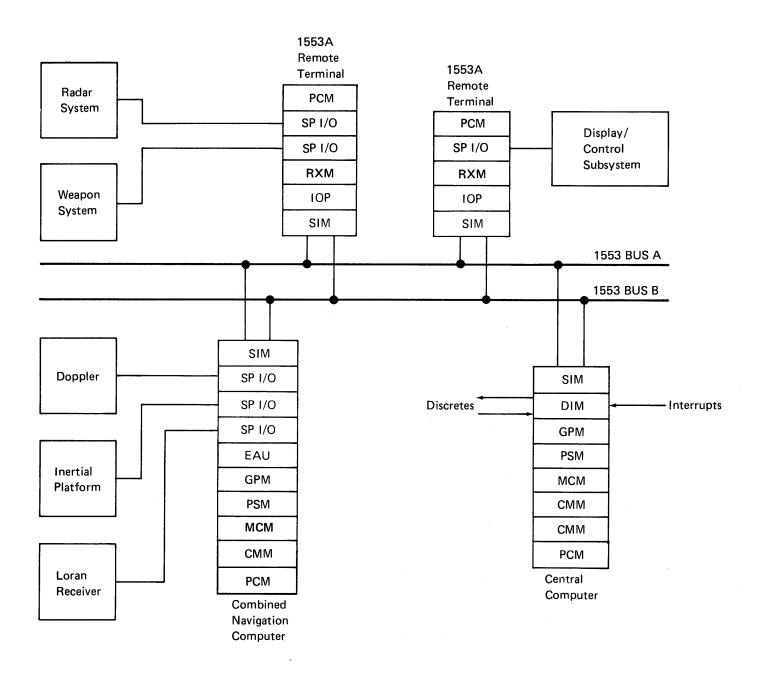

The AN/AYK-14(V) consists of a family of pluggable modules, chassis, interconnecting buses, support equipment, software, firmware, documentation, and training necessary to provide the user with a completely supported computer system. Figure 2 depicts the system elements by subsystem and shows the functional modules applicable to each subsystem. Table 2 briefly defines the AN/AYK-14(V) element nomenclature with each of the elements described more fully in the Module Description section.

Figure 1. AN/AYK-14(V) Modules and Enclosure

#### GENERAL FEATURES

GP, 16-bit digital computer

Physically and functionally modular

Expandable by plug-ins and additional enclosures

Microprogrammed, emulates extended AN/UYK-20

LSI components

ATR enclosures

Variable configurations

#### CENTRAL PROCESSOR

Microprogrammed

2's complement arithmetic

Executive and user states

Two sets of 16-word by 16-bit general registers

Two status registers

Three-level interrupt system

Addressing to 524,288 words

Fixed and floating point arithmetic

4-, 8-, 16-, and 32-bit operands

16- and 32-bit instructions

Direct, indirect, and indexed addressing

Optional hardware floating point module

Loadable/readable 32-bit RTC clock, 1-MHz rate;

16-bit monitor clock, 10-KHz rate

Built-in-test functions

Bootstrap PROM memory

Power failure shutdown/recovery

I/O controller capability:

Chaining capability

Control memory for each channel

Up to 16 channels in various combinations

Interface to support equipment

Sample instruction times:

Shift

1.5 usec

Add, subtract

0.8

Multiply

4.2

Divide

8.4

Basis: single GPM, core memory, overlapped

access, interleaved addresses

#### MEMORY CONTROL AND MEMORY

Core memory module (CMM), 32K words of 18

Semiconductor memory module (SMM), 32K words of 18 bits

Interchangeable core and semiconductor memory modules

CMM has 900-nanosecond cycle time and 350nanosecond access time

SMM has 400-nanosecond cycle time and 200 nanosecond access time

Interleaved or non-interleaved addressing

Read/write expandable memory (RXM), 4K x 18bit RAM with optional 4K PROM

Parity bit per byte

Protect features:

Write protect

Read protect

Execute protect

Block protect in paging system

Memory controller with paging to 524,288 words

#### I/O PROCESSOR (OPTIONAL)

I/O controller capability

Instruction subset compatible with central processor

Microprogrammed

Usable in conjunction with central processor or as stand-alone processor

Real-time and system clocks

16-word by 16-bit general register set

Addressing to 65,536-words

Fixed point 16-bit arithmetic

Interface to support equipment

#### DISCRETE INTERFACE

Eight program selectable external device interrupts

32 bidirectional input or output discretes

16 differential input discretes

16 "switch closure" input discretes

#### **SERIAL 1553A INTERFACE**

MIL-STD-1553A redundant multiplexed bus 1-MHz bit rate

32 terminals per bus and 1 bus controller Operation as bus controller or remote terminal

#### **NTDS CHANNELS**

MIL-STD-1397

Parallel channels:

NTDS slow (41,667 words/sec)

NTDS fast (125K words/sec)

ANEW (125K words/sec)

16-bit and 32-bit (dual channel) (125K words/sec) operation

Computer-to-peripheral and computer-to-computer modes

Externally specified addressing on dual channels Serial channels:

10-MHz bit rate

16- or 32-bit (dual channel) message formats

#### **RS-232-C SERIAL INTERFACE**

Asynchronous 75 to 9600 baud Synchronous to 9600 baud

#### PROTEUS INTERFACE

10-MHz bit rate

Serial transfer, 32-bit message format

#### **PHYSICAL**

| Chassis | Height | Width  | Depth* | Weight* |

|---------|--------|--------|--------|---------|

| XN-1    | 7.62"  | 10.12" | 19.56" | 45-55** |

| XN-5    | 7.62"  | 10.12" | 14.00" | 42      |

| XN-3    | 7.62"  | 10.12" | 12.75" | 35-45** |

NOTES: \*Does not include fan

\*\*Weight varies as functions of optional modules installed

Service conditions as specified in MIL-E-5400 for class 1, 1A, 1B, and 2X equipment

#### PRIMARY POWER

115-Vac, 400-cycle, three-phase, wye-connected as per MIL-STD-704B

400 to 600 watts for XN-1\*

250 to 450 watts for XN-5\*

150 to 350 watts for XN-3\*

NOTE: \*Power varies as function of optional modules installed.

## AVAILABLE OPTIONAL BOLT-ON FAN COOLING

|          |        |       | weight | Power     | Altitude |

|----------|--------|-------|--------|-----------|----------|

| Fan      | Length | Dia.  | (LB)   | (at S.L.) | (FT)     |

|          |        |       |        |           |          |

| IMC 5026 | 3.10"  | 2.75" | 2.00   | 100       | 30,000   |

#### **Processing Subsystem**

The general processing module (GPM) contains all the microprogrammed control, arithmetic unit, registers, and bus interfaces. The processor support module (PSM) contains the supporting elements such as micromemory, real-time clocks, bootstrap memory, bus interfaces, and event (interrupt) logic required to complete the function of the GPM. Together they form a 16-bit central processing unit (CPU) of a general-purpose computer. The extended arithmetic unit (EAU) provides high-speed, 32-bit, floating-point hardware and operates under the control of the GPM.

Figure 2. AN/AYK-14(V) System Elements

The incorporation of an IOP into an AN/AYK-14(V) system, operating in conjunction with the central processor, greatly enhances the processing throughput. The IOP combines the basic functions of the GPM and PSM on one module with a reduced instruction set and performance level. The IOP is microprogrammed to serve either as an IOC or as a single-module, 16-bit, general-purpose CPU without modification.

#### **Intermodule Communication**

The functional modules communicate via one or two identical internal buses: the CPUBUS and the IOBUS. These high-speed, 24-bit parallel buses are the principal data transfer paths between processing modules, memory, and the I/O channels. Additional control signals are transmitted via the EVENTBUS, which transfers interrupt and other event signals. Internal common module interfaces permit flexible module configuration and ensure that module modification or addition of new types will not result in existing module modification.

TABLE 2. HARDWARE IDENTIFICATION

|        | Typical<br>Power | Typical<br>Weight |                              |                                                                                             |

|--------|------------------|-------------------|------------------------------|---------------------------------------------------------------------------------------------|

| Module | (Watts)          | (Lb)              | Name                         | Function                                                                                    |

| GPM    | 46               | 2.1               | General processor            | 16-bit processor with control, registers, and arithmetic unit                               |

| PSM    | 39               | 2.1               | Processor support            | Micromemory, real-time clock, interrupt system                                              |

| EAU    | 44               | 2.1               | Extended arithmetic unit     | High-speed, floating point arithmetic                                                       |

| IOP    | 44               | 2.2               | I/O processor                | 16-bit computer with control, registers, arithmetic unit, micromemory, and interrupt system |

| MCM    | 35               | 1.9               | Memory control               | Memory controller with paging, protect, parity, and two ports                               |

| СММ    | 38               | 3.1               | Core memory                  | 32K words by 18-bit core memory                                                             |

| SMM    | 20               | 3.3               | Semiconductor memory         | 32K words by 18-bit semiconductor memory                                                    |

| RXM    | 12               | 1.0               | Read/write expandable memory | 4K words by 18-bit semiconductor RAM memory with optional addition of 4K PROM               |

| DIM    | 14               | 1.0               | Discrete I/O                 | 32-input discretes, 32-I/O programmable discretes, eight interrupts                         |

| SIM    | 17               | 1.1               | Serial I/O                   | 1553A serial multiplex channel,<br>1-MHz bit rate                                           |

| NIM    | 11               | 1.1               | NTDS fast I/O                | NTDS fast interface 125K words/second                                                       |

| NIM    | 13               | 1.1               | NTDS slow I/O                | NTDS slow interface, 41,667 words/second                                                    |

| NIM    | 10               | 1.0               | NTDS ANEW I/O                | NTDS ANEW interface 125K words/second                                                       |

| NIM    | 15               | 1.1               | NTDS serial I/O              | NTDS serial interface, 10 Mb/s                                                              |

TABLE 2. HARDWARE IDENTIFICATION (CONT.)

| Module                                                                                                                           | Typical<br>Power<br>(Watts) | Typical<br>Weight<br>(Lb) | Name                                               | Function                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| RIM                                                                                                                              | 8                           | 1.0                       | RS-232-C I/O                                       | One serial RS-232-C channel, 9600 bauds                                                                               |

| PIM                                                                                                                              | 13                          | 1.1                       | PROTEUS I/O                                        | I/O serial channel pair, 10-MHz bit rate                                                                              |

| ВЕМ                                                                                                                              | 24                          | 1.0                       | Bus extender                                       | Extends all AN/AYK-14(V) internal buses outside the enclosure                                                         |

| *PCM-1<br>PCM-2                                                                                                                  | Varies                      | 9.5<br>11.4               | Power converter                                    | Regulated power supply. MIL-STD-704 power input, status outputs                                                       |

| Chassis                                                                                                                          |                             |                           |                                                    |                                                                                                                       |

| XN-1                                                                                                                             | N/A                         | 16.3                      |                                                    | 19.56" by 10.125" by 7.625"<br>ATR enclosure and chassis                                                              |

| XN-5                                                                                                                             | N/A                         | 11.9                      |                                                    | 14" by 10.125" by 7.625" ATR enclosure and chassis                                                                    |

| XN-3                                                                                                                             | N/A                         | 12.3                      |                                                    | 12.75" by 10.125" by 7.625" ATR enclosure and chassis for computer extension                                          |

| Support                                                                                                                          | Equipment                   |                           |                                                    |                                                                                                                       |

| L/V                                                                                                                              | 80                          | 43                        | Loader/verifier                                    | Portable militarized tape loader and control panel                                                                    |

| CCU                                                                                                                              | 440                         | 383                       | Computer control unit with tape unit and formatter | Laboratory operator console for firmware and software debugging and maintenance. Interfaces to commercial peripherals |

| NOTE: *PCM-1 provides 410 watts of output power, $n \approx 71\%$ . PCM-2 provides 540 watts of output power, $n \approx 71\%$ . |                             |                           |                                                    |                                                                                                                       |

#### **Memory Subsystem**

The memory subsystem includes interchangeable 32K-word core memory modules (CMM) and 32K-word semiconductor memory modules (SMM) with 18-bit word length. The CMM cycle time is 900 nanoseconds and the SMM cycle time is 400 nanoseconds. The memory control module (MCM) interfaces between the GPM and the memory modules (CMM or SMM). The MCM has both CPUBUS and IOBUS interfaces which permit the GPM to use one bus for instruction access and the other for operands to enhance effective access time. The MCM also provides two channels to memory modules, the OMEMBUS and EMEMBUS, which can increase effective access time through interleaved addressing between two memory banks.

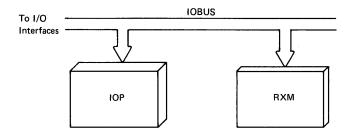

The read/write expandable memory module (RXM) is a 4K word by 18-bit semiconductor memory with 400-nanosecond cycle time which operates directly with the IOP via the IOBUS. An optional addition of 4K read-only memory (PROM) is also available. The primary application of the RXM is to provide memory for use with the IOP as a controller or as a small dedicated 2-card computer.

#### I/O Subsystem

The AN/AYK-14(V) system organization provides for up to 16 I/O channels, each on individual functional modules which communicate with the computer system via the IOBUS interface. The standardization of internal interfaces permits any I/O channel module type to be interchanged in the chassis I/O slots by simple plug-in replacement. Available chassis provide from four to six I/O channels, including the DIM. Expansion to more I/O channels requires the additional XN-3 type enclosures. A number of I/O module types are currently available to match standard I/O channel characteristics. These are:

- MIL-STD-1553A avionics serial multiplex

- NTDS (fast, slow, ANEW, and serial) MIL-STD-1397

- RS-232-C

- PROTEUS

The I/O controller (IOC) functions can be executed by either the central processor (GPM and PSM) or the optional I/O processor (IOP).

Special I/O channel types may be added as required without modification to backpanel wiring, internal interfaces, or microcode. This is an important feature of the AN/AYK-14(V), since a principal problem area in military system applications involves accommodating special equipment and sensor interfaces.

User-equipment interrupts can be brought into the system either through the associated I/O channel or via the discrete interface module (DIM), which also has provision for 32 input and 32 input or output discrete signals.

Expansion of the computer beyond a single enclosure or implementation of direct memory access (DMA) I/O is effected through the use of the bus extender module (BEM), which provides a buffered extension of all internal computer buses to another enclosure.

#### **Power Subsystem**

Power for all modules in an enclosure is supplied by a power converter module (PCM) with appropriate regulated voltage and current capabilities. Present designs operate on MIL-STD-704 power, 115-Vac, 400-cycle, three-phase, wye-connected.

#### **Chassis Subsystem**

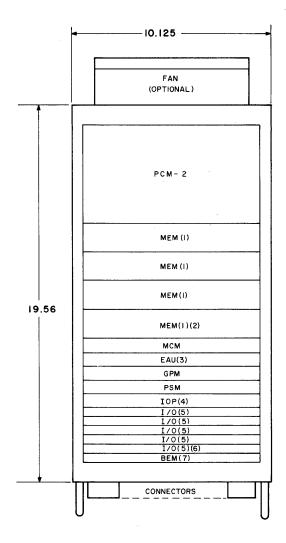

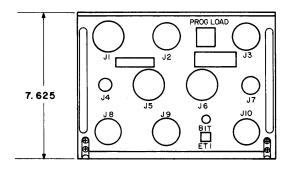

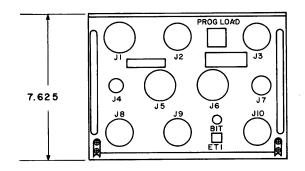

All modules plug into an ATR-type chassis equipped with slots to accommodate a combination of module types. Currently three standard chassis types designed for MIL-E-5400, Class II environments are available for 16-bit computers. Figure 3 shows the three standard chassis types along with the module configurations available for each. Connector location and basic dimensions are shown. It should be noted that the XN-3 is an extension unit to be used with the XN-1 chassis to provide additional memory, processing, and/or I/O capability. Multiple XN-3 chassis can be used to further expand the system.

#### **Environment**

The basic module of the AN/AYK-14(V) family is designed for use in MIL-E-5400 (airborne) when installed in a suitable enclosure. The total range of conditions includes temperatures of -54°C to 71°C, altitudes to 70,000 feet, and levels of shock, vibration, humidity, and EMI appropriate to these environments.

Qualification of the chassis types listed in Table 2, to MIL-E-5400, class 2 requirements will occur under the current AN/AYK-14 contract from the U.S. Navy.

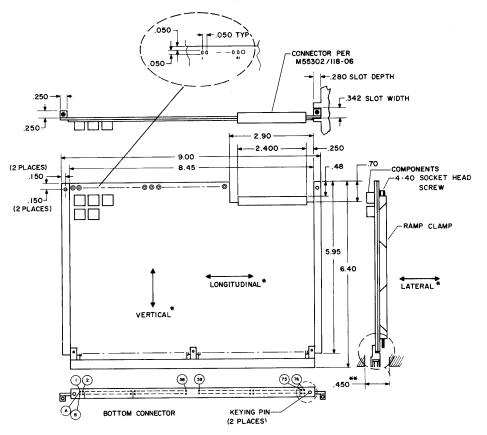

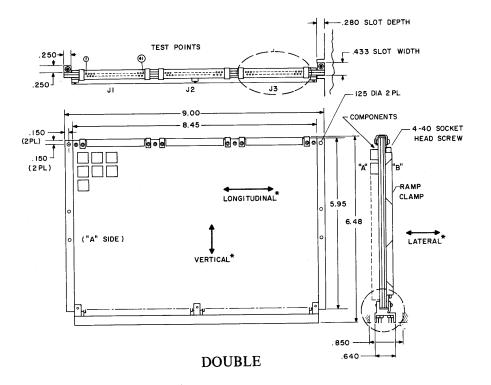

All modules are designed for conduction cooling via a heat sink backing the printed circuit boards. The modules have ramp clamps along both short edges to provide solid mechanical and thermal contact to the slots in the chassis. Heat is transferred from the chassis heat sink via an air plenum, which may be supplied by a vehicle cooling air system or optional bolt-on fan. No cooling air is needed over module components. Figure 4 illustrates a single and a double module.

The rigid module structure, stiffened by the heat sink, withstands severe shock and vibration environments.

All modules are conformal coated for moisture resistance. The module design permits great flexibility in chassis cooling provisions to meet multiple application requirements.

#### **Configuration Capability**

The functional partitioning of the modules and the internal bus structures provide for flexible configuration of a wide range of AN/AYK-14(V) computers. The AN/AYK-14(V) system allows the building up the system by addition of modules to meet the problem computing bandwidth and capacity requirements. Some examples are given to show how these building blocks can be used to balance computer size, weight, power, and cost against performance.

Figure 5 shows the minimum AN/AYK-14(V) computer configuration, which consists of an IOP as the 16-bit processor and an RXM 4K by 18-bit random access memory (RAM) semiconductor memory (with optional 4K PROM). This is a "bare" module configuration and assumes that the modules are incorporated as components into the user's equipment. The user's equipment power supply would provide regulated 5-Vdc power for the modules and the user would also provide the I/O adaptation to the IOBUS interface. IOP/RXM combinations can also be used effectively as computing elements in distributed processing systems.

An expanded configuration (Figure 6) yields a complete 16-bit, general-purpose processor with high-speed floating-point hardware, hardware I/O controller, 128K words of 18-bit core memory, and up to 16 I/O channels of various types. This example illustrates the role of the identical CPUBUS and IOBUS in organizing the modules into a powerful computer. Since the GPM has two bus interfaces to the MCM, it is possible to overlap instruction and operand fetches from memory. In addition, it should be noted that the two memory channels, OMEMBUS and EMEMBUS, permit interleaving of memory addresses between memory banks for high, effective access speed.

### AN/AYK-14(v) CONFIGURATOR

#### **XN-1 COMPUTER**

#### STANDARD

The XN-1 contains the following basic module set:

- Power Conversion Module (PCM-2)

- General Processor Module (GPM)

- Processor Support Module (PSM)

- Memory Control Module (MCM)

#### **OPTIONS**

- 1) Combinations of the following memory modules, up to four total:

- 32K x 18-word Core Memory Module (CMM-32)

- 32K x 18-word Semiconductor Memory Module (SMM)

- 2) 4K x 18-word Read/Write Memory (RXM) is used with the IOP (additional 4K PROM optional).

- 3) Extended Arithmetic Unit (EAU) for high speed floating point is optional.

- 4) Input/Output Processor (IOP) for independent I/O processing is optional.

- 5) Any combination of the following I/O modules, up to five total:

- 1553A Serial (SIM)

- NTDS Fast (NIM-B)

- NTDS Slow (NIM-A)

- NTDS ANEW (NIM-C)

- NTDS Serial (NIM-S)

- PROTEUS (PIM)

- RS-232 (RIM)

- Discrete I/O (DIM) with 32 discretes and 8 interrupts wired to the front panel.

- 6) Discrete I/O (DIM) with 64 discretes and 8 interrupts wired to the front panel.

- 7) Bus Extension Module is required if additional memory or I/O expansion is needed.

| Connector           | Туре          | Use         |

|---------------------|---------------|-------------|

| J1                  | MS27656T25-35 | I/O         |

| J2, J8, J9, J10, J3 | MS27656T23-35 | I/O         |

| J5, J6              | MS27656T25-35 | BSXTND      |

| J4                  | MS27468T11-35 | Power       |

| J7                  | MS27656T17-35 | Maintenance |

Figure 3. AN/AYK-14(V) Configurator — XN-1 Layout (Sheet 1 of 3)

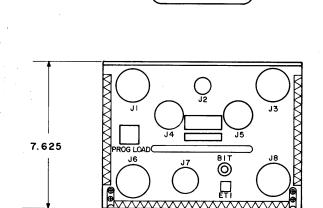

#### AN/AYK-14(v) CONFIGURATOR

#### **XN-5 COMPUTER**

#### STANDARD

The XN-5 contains the following basic module set:

- Power Conversion Module (PCM-1)

- General Processor Module (GPM)

- Processor Support Module (PSM)

- Memory Control Module (MCM)

#### **OPTIONS**

- 1) Combinations of the following memory modules, up to two total:

- 32K x 18-word Core Memory Module (CMM-32)

- 32K x 18-word Semiconductor Memory Module (SMM)

- 2) Input/Output Processor (IOP) for independent I/O Processing is optional.

- 3) Any of the following I/O modules

- 1553A Serial (SIM)

- PROTEUS (PIM)

- NTDS Serial (NIM-S)

- 4) Any of the following:

- SIM

- NIM-S

- NIM-A

- PIM

- NIM-B

- RIM

- NIM-C

- DIM

(Discrete I/O with 32 discretes and 8 interrupts wired to front panel)

5) Discrete I/O (DIM) with 64 discretes and 8 interrupts

| Connector | Туре          | Use         |

|-----------|---------------|-------------|

| J1, J3    | MS27656T25-35 | I/O         |

| J6, J8    | MS27656T25-35 | I/O         |

| J2        | MS27468T11-35 | Power       |

| J4, J5    | MS27656T15-35 | I/O         |

| J7        | MS27656T17-35 | Maintenance |

10.125 -

FAN (OPTIONAL)

PCM-I

MEM (1)

MEM (I)

MCM GPM

PSM IOP (2) I/O (3)

I/O (4)

1/0(4)(5)

CONNECTORS

14.00

Figure 3. AN/AYK-14(V) Configurator – XN-2 Layout (Sheet 2 of 3)

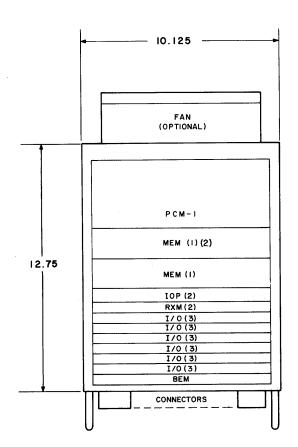

## AN/AYK-14(v) CONFIGURATOR XN-3 COMPUTER

#### STANDARD

The XN-3 contains a Power Conversion Module (PCM-1) and a Bus Extender Module (BEM) for interface to the XN-1 computer.

#### **OPTIONS**

- 1) Memory expansion with the following modules, up to two total:

- 32K x 18-word Core Memory Module (CMM-32)

- 32K x 18-word Semiconductor Memory Module (SMM)

System memory expandable to 512K words.

- 2) Input/Output Processor (IOP) is optional as a XN-3 stand-alone processing unit; a 4K x 18-word Read/Write Memory (RXM) and/or one additional memory is used with the IOP (additional 4K PROM optional).

- 3) Any combination of the following I/O modules, up to six total:

- 1553A Serial (SIM)

- PROTEUS (PIM)

- RS-232 (RIM)

- NTDS Fast (NIM-B)

- NTDS Slow (NIM-A)

- NTDS ANEW (NIM-C)

- NTDS Serial (NIM-S)

- Discrete I/O (DIM) with 32 discretes and 8 interrupts wired to the front panel.

NOTE: System I/O expandable to 16 I/O channels.

| Connector       | Туре           | Use         |

|-----------------|----------------|-------------|

| J1, J3          | MS27656 T25-35 | I/O         |

| J5, J6          | MS27656 T25-35 | BSXTND      |

| J2, J8, J9, J10 | MS27656 T23-35 | I/O         |

| J4              | MS27468 T11-35 | Power       |

| J7              | MS27656 T17-35 | Maintenance |

Figure 3. AN/AYK-14(V) Configurator – MEU Layout (Sheet 3 of 3)

**SINGLE**

Figure 4. Module Outlines

Figure 5. Minimum Configuration

Figure 6. Expanded Configuration

#### PHYSICAL CHARACTERISTICS

The physical characteristics of an AN/AYK-14(V) computer depend on the module complement and chassis type required to meet the processing and environmental requirements.

All processor modules, except the PCM, are 6 by 9 inches. The GPM, PSM, BEM, MCM, and IOP modules are mountable on 0.85-inch centers

and weigh about 2 pounds each. All I/O modules are mountable on 0.45-inch centers and weigh about 1.1 pound each. Memory modules are mountable on 1.45-inch centers and weigh about 3.1 pounds each. Modules and chassis have a provision for keying to prevent improper module insertion into the chassis.

#### RELIABILITY

To ensure a high degree of reliability, a reliability plan was implemented during the design phase. This plan was prepared in accordance with MIL-STD-785A and paragraph 3, 1, 1, 4 of RM-533D2, 1.

This plan provides for certain proven reliability concepts to achieve AN/AYK-14(V) reliability requirements. These concepts are as follows:

- Reliability disciplines were integrated into the design process.

- All junction temperatures are less than 110°C.

- Management reviews enforced engineering disciplines.

- A rigorous parts quality program was implemented.

- Stringent subassembly screening programs were established.

- Test programs apply profiles for operation and environmental stress.

- A comprehensive failure reporting program was implemented.

Various reliability analyses were conducted to ensure reliability requirement compliance. These analyses are:

- 1) Failure mode and effects

- 2) Fault tree

- 3) Worst case

- 4) Sneak circuit

- 5) Thermal

- 6) Dynamic

Table 3 illustrates the results of these reliability efforts by showing predicted MTBF for two configurations in a MIL-E-5400 class 2 environment. MTBF for other configurations will depend upon the environment and module assortment used.

TABLE 3. RELIABILITY

| Module       | No. of    | Modules   |

|--------------|-----------|-----------|

| Type         | Config. 1 | Config. 2 |

| GPM          | 1         | 1         |

| PSM          | .1        | 1         |

| MCM          | 1         | 1         |

| CMM          | 3         | 1         |

| PCM-1        |           | 1         |

| PCM-2        | 1         |           |

| SIM          | 2         | 1         |

| DIM          | 1         | 1         |

| IOP          |           | 1         |

| PROTEUS      | 1         |           |

| XN-1 Chassis | 1         |           |

| XN-5 Chassis |           | 1         |

| MTBF (Hours) | 1700      | 2200      |

#### MAINTAINABILITY

Upon a malfunction in the AN/AYK-14(V) while installed in an aircraft, the resident diagnostic program detects the fault and identifies its occurrence on the bit fault indicator on the front of the computer. After the malfunction, the computer is removed and replaced with a properly performing computer.

The faulty computer is sent to the shop level maintenance facility where the loader/verifier (L/V) is used to isolate the malfunctioning shop replaceable assembly (SRA) through a fault isolation diagnostic.

Upon module isolation by the isolation diagnostic the computer cover is removed and the failed module is removed by the release of the ramp clamp fasteners. The module is replaced with a spare and the program diagnostic is performed to verify proper operation. The computer is now ready for return to the organizational level.

The faulty SRA is forwarded to the repair facility at the depot level for isolation and repair of the faulty components through use of automatic test equipment (ATE). Test points are also available to allow isolation to lower levels in a functional sequence, so that repairs can be made efficiently. After repair and verification checks, the SRA is returned to the shop level maintenance facility stores for reissue as required.

Predictions and analysis concerning maintainability of the AN/AYK-14(V) are in accordance with AR-10A. The MTTR at the shop level is predicted to be less than 20 minutes. This time includes the following:

- 1) Installation of unit for test

- 2) Verification of fault

- 3) Isolation of faulty SRA

- 4) Removal/replacement of faulty SRA

- 5) Verification of proper operation

- 6) Removal of unit from test

#### **PERFORMANCE**

The processing throughput of a specific AN/AYK-14(V) computer depends on the configuration of processor and memory modules used. In addition, the measured throughput depends on the mix of instruction types involved in the problem and the rate of interrupt and I/O processing required.

Processing throughputs can be characterized by performance on an instruction mix typifying usual applications. For the AN/AYK-14(V) computer, the performance on a mix containing 80-percent fixed point addition and 20-percent fixed point multiply instructions is given in Table 4 for various memory types and configurations and as a function of instruction and operand type. These preliminary performance figures are given for a single 16-bit

CPU in Table 4 (a) and for a stand-alone IOP in Table 4 (b). Table 4 (c) gives the floating point arithmetic performance of the CPU when configured with the optional EAU. The performance is given in thousands of operations (instructions) per second (KOPS).

Additional performance data is provided in the Instruction Repertoire section, which lists individual instruction execution times for a specific AN/AYK-14(V) core memory configuration using

overlap and interchanging features.

Techniques for performance enhancement include:

- Use of memory overlap by using CPUBUS and IOBUS for independent access for instructions and operands

- Use of interleaved addresses between two memory banks

- Use of SMMs

- Use of the EAU for high-speed floating point (4-microsecond add, 5-microsecond multiply)

TABLE 4. AN/AYK-14 PERFORMANCE ON INSTRUCTION MIX

#### (a) CPU (GPM and PSM)

80% Fixed Point Add, 20% Multiply

| Instruction Type | Data<br>Length | KOPS* Interleaved Core/Semicond. | KOPS Non-Interleaved Core/Semicond. |  |  |  |

|------------------|----------------|----------------------------------|-------------------------------------|--|--|--|

| 16-bit, RR       | 16             | 650/675                          | 630/675                             |  |  |  |

| 16-bit, RI       | 16             | 520/575                          | 405/560                             |  |  |  |

| 16-bit, RR**     | 32             | 395                              | 395                                 |  |  |  |

| 16-bit, RI **    | 32             | 295/300                          | 250/295                             |  |  |  |

| 32-bit, RX       | 16             | 390/430                          | 300/380                             |  |  |  |

| 32-bit, RX       | 32             | 265/290                          | 210/280                             |  |  |  |

#### (b) IOP

80% Fixed Point Add, 20% Multiply

| Instruction Type | Data<br>Length | KOPS |

|------------------|----------------|------|

| 16-bit, RR       | 16             | 430  |

| 16-bit, RI       | 16             | 290  |

| 32-bit, RX       | 16             | 250  |

#### (c) EAU (with GPM and PSM)

80% Floating Point Add, 10% Floating Multiply, 10% Floating Divide

Typical performance is 200 KOPS but exact performance is data dependent.

NOTE: \*KOPS is defined as thousands of operations per second.

\*\*The 32-bit data instruction reflects a 32 x 32 multiply yielding a 64-bit product.

- Use of the IOP to share I/O and instruction processing functions

- Incorporation of frequently used algorithms into direct microcode

Overlap is standard in the AN/AYK-14(V) whenever a GPM is used. Interleaving is standard in all configurations using an MCM and an even number of identical memory modules. Interleaving can be inhibited, if desired, by the use of a jumper wire on a front panel connector.

The combined use of the CPU and IOP is a plugin enhancement available in the XN-1 and XN-5 chassis and requires no microcode changes to implement.

Use of microcoded algorithms can frequently attain a five to 10 times speedup in algorithm processing over the conventional software subroutine approach. The GPM microcommand processing time is generally 180 nanoseconds (some microcommands, particularly those involving arithmetic logic units [ALU] shifting, require 210 nanoseconds) and the IOP microcommand time is 250 nanoseconds. These times include both microcommand execution and reading the next microcommand.

Control Data is prepared to assist users in configuring suitable AN/AYK-14(V) computers to match specific application requirements and to estimate expected performance.

#### MODULE DESCRIPTIONS

The modules described in this section represent the current AN/AYK-14(V) module designs. It is expected that new module types will be added to meet future applications requirements. New or special modules will be designed to interface with standard AN/AYK-14(V) internal buses to preserve system integrity.

#### **General Processor Module (GPM)**

The GPM is a 16-bit microprogrammable processor based on the AMD 2900 series microprocessor

slice LSI devices. The architecture is augmented for high-speed performance with additional registers, internal data, and control transfer paths. The GPM features which contribute to its performance include:

- 48-bit microcommand control

- Microprogram address sequencing to 4K words

- 180-nanosecond microcommand cycle

- 256 by 16-bit word register file

- 256 by 16-bit word multiport CFILE

- Dual identical parallel bus interfaces (CPUBUS and IOBUS)

- Event interface

- Interface to micromemory on PSM

- Serial interface to support equipment

- Interface to EAU

The GPM operates from microcommands stored on the PSM module (up to 4K words of micromemory).

#### **Processor Support Module (PSM)**

The PSM augments GPM functions to form a complete 16-bit computer in two modules. The partitioning of the functions between GPM and PSM was designed to allocate those functions to the PSM that might require modification as applications change. The PSM features include:

- Up to 4K by 48 bits of PROM micromemory for the GPM.

- 1K by 16 bits of PROM bootstrap memory for computer system initiation via the 1553A I/O channel,

- Two parallel bus interfaces (CPUBUS and IOBUS).

- Event interface.

- Event monitor logic, which forms the basic hardware portion of the event (interrupt) processing.

- Four loadable/readable clocks for monitoring and timing functions (1-microsecond resolution).

- 32-bit high-speed multiply logic.

- BIT timer with 2.097-second increment, 4-bit count.

The AN/AYK(V) computer micromemory may contain commands for processing a variety of functions including:

- 1) AN/AYK-14(V) instruction set interpretation and maintenance of the computer status.

- 2) Built-in-test (BIT) functions.

- 3) Diagnostic and fault isolation functions.

- 4) Special macroinstruction or algorithm processing.

#### Extended Arithmetic Unit (EAU)

The EAU utilizes the AN/UYK-20 floating-point format which consists of an 8-bit exponent and a 24-bit mantissa. Typical execution times, including GPM control, are 5 microseconds for add and 7.7 microseconds for multiply. All AN/AYK-14(V) computers configured with a GPM and PSM execute all AYK-14(V) floating point arithmetic instructions. When configured without the EAU, the instructions are implemented via firmware. The incorporation of the EAU automatically increases floating point execution speed without firmware changes.

In addition the EAU also performs the following instructions

Square Root Sine Arcosine

Exponent Cosine Arcsine

Log base e Tangent Arctangent

Arguments and results are expressed in floating

point values.

#### Input/Output Processor (IOP)

The IOP is a complete 16-bit processor combining the basic functions of the GPM and PSM on one module. The instruction set is a subset of the total AN/AYK-14(V) instruction set. To accomplish a one-module processor, the performance and features are reduced from the GPM/PSM capability. The IOP is intended for use in three general applications types:

- 1) As a small scale, stand-alone, general-purpose processor with emulation capabilities.

- 2) As an I/O controller (IOC) in conjunction with a GPM/PSM as instruction processor.

- 3) As a combination IOC and instruction processor in conjunction with a GPM/PSM.

#### Features of the IOP include:

- 48-bit microcommand control

- Up to 2K micromemory on the module

- 250-nanosecond microcommand cycle

- 256 by 16-bit word register file

- Single parallel bus interface (IOBUS)

- Event interface

- Serial interface to support equipment

- Real-time clock with 1-microsecond resolution

- BIT timer, 2.097-second increment, 3-bit count

- Event monitor logic

- Microcommand format identical to GPM

#### I/O Modules

All I/O channel modules are physically the same size and are interchangeable in any I/O module chassis slot. Each I/O channel module implements a single I/O channel of a designated type and has a common set of intermodule interfaces including the IOBUS and event interface. Each I/O module type contains the logic to implement the specific channel type characteristics and operate with a standardized IOBUS communication procedure. All I/O modules have provision for a module test operation in which test data is looped through the module and returned to the processor. The standard I/O channel module set can be augmented with special channel modules to meet system requirements. The special channels will use the same IOBUS and event interface as the standard I/O modules.

#### Discrete Interface Module (DIM)

The DIM is used to provide a convenient interface for communicating single-bit status, event, or control information between user devices and the computer.

The DIM provides the following interface capabilities:

• Eight external device interrupts. These can have program selectable priority and can be individually masked.

- 32 bidirectional input or output discretes. These use differential TTL interface signals. They are program selectable as inputs or outputs in groups of four.

- 16 differential input discretes. These use differential lines, ac terminated.

- 16 "switch closure" input discretes.

- The 32 bidirectional discretes have a loop test capability.

#### Serial Interface Module (SIM)

The SIM implements a serial multiplex data channel meeting the channel control and format characteristics of MIL-STD-1553A. This channel type is the standard intersystem communication facility on board modern military aircraft. The module interfaces to two 1553 buses for redundant operation.

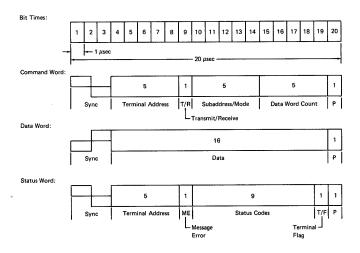

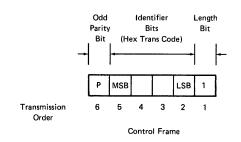

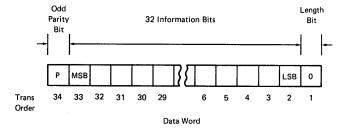

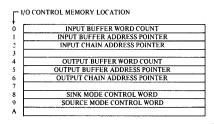

The module can operate with any MIL-STD-1553A protocol and can function as either a bus controller or remote terminal unit. Information is transferred on a single shielded twisted pair line at a 1-MHz bit rate. Data is transferred in 20-microsecond frames, each divided into 17-bit times of 1 microsecond and one 3-microsecond sync interval. All messages are addressed and use three types of words, as shown in Figure 7:

• <u>Command word</u> — sent by bus controller to address appropriate terminal, specify message type, and set data word count for subsequent transfer.

Figure 7. MIL-STD-1553A Word Formats

- <u>Status word</u> set by a terminal in response to command word. Identifies terminal and reports status.

- <u>Data word</u> containing 16 bits of message data, sync pattern, and a parity bit.

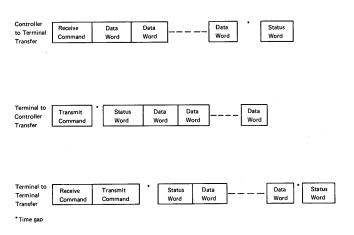

Up to 32 terminals and 1 bus controller can interface on a single bus. All transmissions and receptions are initiated and controlled by the bus controller using message formats as shown in Figure 8.

The SIM contains interfaces to two 1553A buses and has the capability of data transfer on one and monitoring the other at any time.

Figure 8. MIL-STD-1553A Message Formats

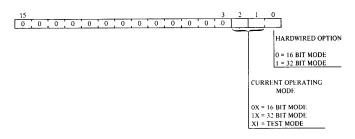

#### NTDS Interface Modules (NIM)

There are four types of NIMs, each capable of operation according to MIL-STD-1397:

- 1) NTDS slow 16-bit parallel transfer up to 41,667 words per second. Binary voltage levels of 0 Vdc (logical 1) and -15 Vdc (logical 0).

- 2) NTDS fast 16-bit parallel transfer of up to 125,000 words per second. Binary voltage of 0 Vdc (logical 1) and -3 Vdc (logical 0).

- 3) ANEW 16-bit parallel transfer of up to 125,000 words per second. Binary voltage levels of 0 Vdc (logical 1) and 3.5 Vdc (logical 0).

- 4) <u>Serial</u> serial data transfer of up to 10 megabits per second on one cable. Bipolar ±3.25V signals.

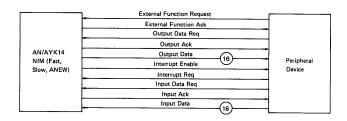

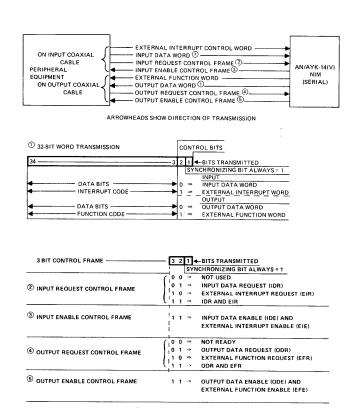

Channel interface lines for NTDS fast, slow, and ANEW are shown in Figure 9, and for serial in Figure 10. Two NIM parallel channels can be operated together to form a 32-bit wide parallel channel. Transfer operations on the serial channel involve the use of 3-bit control frames and 34-bit data frames (32-bit message data, function, or interrupt code, and 1-bit word ID, 1-bit sync), according to procedures defined in MIL-STD-1397. The modules support operation in computer-to-computer, computer-to-peripheral, externally specified addressing modes as described in MIL-STD-1397.

#### RS-232-C Serial Interface Module (RIM)

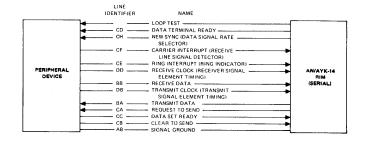

The RIM provides a full-duplex RS-232-C serial channel operable at selectable baud rates from 75 to 9600 baud for the asynchronous mode and in synchronous mode to 9600 baud. See Figure 11 for cable configuration.

The module can be converted to operate to MIL-STD-188C with some component changes, but without circuit board modifications.

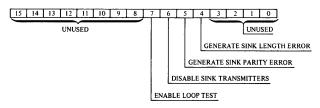

#### PROTEUS Interface Module (PIM)

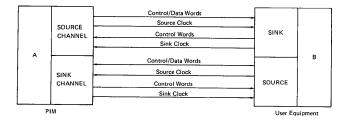

The PIM contains the logic to implement a PRO-TEUS digital channel pair capable of full-duplex data transmission at a nominal 10-MHz bit rate. The channel is designed to NADC Specification No. A30-15590.

Transmission on the PROTEUS channel is between a source and a sink, with initiation and control by the source. A source transmits 6-bit control words and 34-bit data words (32 message bits, one parity bit, and one word-type bit). The sink responds to each source word with an appropriate 6-bit control word to accomplish a positive handshaking procedure on a word-by-word basis.

Figure 9. NTDS Slow, Fast, and ANEW Channel Interface

Figure 10. NTDS Serial Channel Interface and Message Format

Figure 11. RS-232-C Serial Channel Interface

Parity is provided on both control and data words for error detection, and retransmission is used for error correction.

The channel pair uses a total of eight differential NRZ signals as depicted in Figure 12.

Figure 12. PROTEUS Channel Pair

#### Bus Extender Module (BEM)

The BEM provides an extension of the internal AN/AYK-14(V) buses and interfaces outside the enclosure to permit extension of memory, processor, and/or I/O subsystems to additional enclosures up to 15 feet (total cable length) from the computer. All voltage levels are TTL compatible and employ differential line drivers/receivers for all I/O lines. The electrical and logical design permits BEM-to-BEM communication. The BEM does not have a channel address as do other I/O modules, but instead appears transparent to bus operation. Any communication via the BEM results in a slight interface delay of approximately 75 nanoseconds in each direction, relative to direct module intercommunication. The BEM can be used to interface a DMA channel.

#### **Memory Modules**

#### Memory Control Module (MCM)

The MCM provides a two-port paged interface to two independent, interleaved memory channels, and thus allows simultaneous access by two users. The MCM contains the control, interface, and paging logic to operate core and SMMs with the AN/AYK-14(V) processor system. The MCM features include:

- Interfaces to CPUBUS and IOBUS

- Dual memory bus interfaces to memory modules OMEMBUS and EMEMBUS

- 16-bit address to 19-bit address paging system

- Phasing of memory modules between memory buses

- Parity bit logic, one parity bit per byte

- Block protect in paging system

- Read protect

- Write protect

- Execute protect

#### Core Memory Module (CMM)

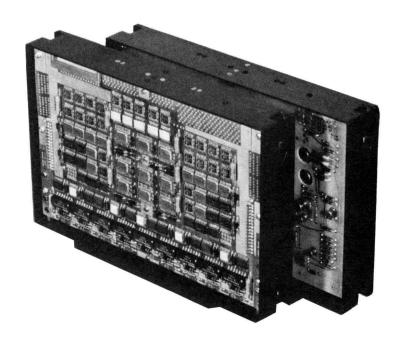

The CMM is available as a 32K by 18-bit word module. The CMM is a plug-in unit containing all of the specified core storage, associated drive and and sense electronics, timing and control logic, and interface circuitry. The form-factor and electrical interface of the 32K CMM is identical to the SMM which provides for complete interchangeability as shown in Figure 13.

#### The CMM features are:

- 900-nanosecond read/write cycle time

- 350-nanosecond access time

- Low power, average 38 watts for 32K words (based on half 1's, 50-percent standby), maximum 70 watts

- Byte operation

- Interface to OMEMBUS or EMEMBUS

- Mountable on 1.45-inch centers

- Read/modify/write capability

- Data guard, indicates power supply out of tolerance (optional)

#### Semiconductor Memory Module (SMM)

The SMM provides 32K by 18-bit words in a module which is compatible to and interchangeable with the CMM.

Figure 13. Interchangeable Core (Front) and Semiconductor (Rear) Memory Modules

#### The SMM features are:

- 200-nanosecond read access time

- Low power, 20 watts average for 32K words

- Interface to OMEMBUS or EMEMBUS

- Mountable on 1.45-inch centers

#### Read/Write Expandable Module (RXM)

The RXM contains 4K words by 18 bits of read/write static semiconductor memory and an optional additional 4K words of read-only memory (PROM). Features include:

- 400-nanosecond cycle time

- 275-nanosecond access time

- Interface to IOBUS or CPUBUS

- Mountable on 0.45-inch centers

- Parity logic, one bit per byte

- If the PROM option is desired, memory contents must be specified at time of order

#### **NOTE**

This memory is unpaged and does not interface with the MCM. It is intended to operate directly with a processor via the IOBUS interface. Multiple RXMs can be used in a system up to a total of 65,536 words; however, the present AN/AYK-14(V) chassis (XN-1 and XN-3) provides space for only one RXM each. The primary application of RXMs is to provide memory functions for small AN/AYK-14(V) configurations using the IOP as a standalone processor. An RXM can also be used as a private program memory for the IOP when used in configurations employing both the IOP and CPU in combination. In the latter case the CPU will not have access to the RXM. When installed in the XN-1 or XN-3 chassis, the RXM is assigned address ranges F000 to FFFF (Hex) for the RAM portion and E000 to EFFF (Hex) for the optional PROM portion.

#### **Power Converter Module (PCM)**

The PCM provides regulated dc power required to operate AN/AYK-14(V) modules from military aircraft power sources. Two sizes of PCMs are currently available to power various computer configurations. The PCMs are themselves modular and new capacities can be developed to meet other power source or computer configuration requirements.

The PCMs operate from 115-Vac, three-phase, 400-Hz, wye-connected input power. The design is compatible with MIL-STD-704B and MIL-STD-461A per requirements of AS-4197.

PCM-1 and PCM-2 supply thermal protection and power failure signals as well as sequencing for power-up and power-down operations. Approximately 280 microseconds are available for saving machine state and registers upon input power loss detection. PCM capacities are given in Table 5 below.

TABLE 5. PCM CAPACITIES

| Module | N           | <b>M</b> aximun | 1 Output | t                     |                  | m int |

|--------|-------------|-----------------|----------|-----------------------|------------------|-------|

| Type   | 1 1 1 1     |                 | Size     | Typical<br>Efficiency |                  |       |

| PCM-1  | 51A         | 3.3A            | 8.3A     | 1A                    | 7" by 9" by 3.5" | 71%   |

| PCM-2  | 78 <b>A</b> | 3.3A            | 8.3A     | 1A                    | 7" by 9" by 4.9" | 71%   |

#### SUPPORT EQUIPMENT

Application and maintenance of the AN/AYK-14(V) computer family is aided by the availability of several pieces of support equipment.

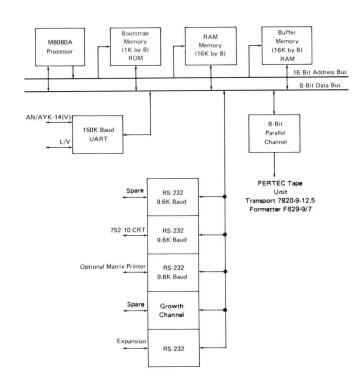

#### Computer Control Unit (CCU)

The CCU is standard lab support equipment for use with AN/AYK-14(V) computers. It interfaces with the computer through the support

equipment channel and provides operator console functions as well as peripheral equipment interfaces. It is intended for use as ground support equipment and is useful in application software debugging and maintenance operations. The CCU consists of the following elements mounted in and on an operator stand as shown in Figure 14 and the block diagram, Figure 15.

- CRT display and keyboard

- Magnetic tape unit and formatter

- CCU electronics package including an 8080A microprocessor and memory

- RS-232-C interfaces for optional printer and other peripherals

- Interface to the AN/AYK-14(V) computer via the computer support channel

The CCU and its peripheral equipment operate on 115V, 60 Hz, single-phase power. An external, three-phase, 115-Vac, 400-Hz supply is also required for operating the AN/AYK-14(V) computer.

The magnetic tape unit included with the CCU is a Pertec Model 7820-9-12.5 and its associated Pertec Model F829-9/7 Formatter Unit. This tape is IBM compatible, NRZI format, nine-track, and permits transfer of programs and data from a commercial computer to the AN/AYK-14(V).

The CRT and keyboard make up a Control Data Model 752-10 conversational display terminal and include a 12-inch CRT, 67-key keyboard, with the capacity to display 24 lines of up to 80 characters per line, and a self-contained character refresh memory.

A recommended useful option is an impact line printer for use in listing memory contents. This printer is a desk-top unit which uses a 7 by 7 dot matrix print head and prints at a 173-character-per-second rate. It should be noted that the CCU peripherals are controlled by the 8080A processor and do not require interface channels in the AN/AYK-14(V). This is important, since the I/O channels in the AN/AYK-14(V) can remain connected to the military system devices while the CCU is in use.

Figure 14. Computer Control Unit (Front View)

Since the CCU logic is based on an 8080A microprocessor, the CCU functions are readily modified or expanded to provide very flexible operation and adaptability to a wide range of computer support procedures.

The CCU contains all controls and displays necessary for computer hardware and software operation, monitoring, and servicing, thus ensuring simplified operation.

Switches are provided to perform the following:

- Reset the computer and maintenance/ control panel circuits to initial operating conditions.

- Stop execution of the program at the completion of either the current instruction or pending I/O.

- Start execution at an address selected on the keyboard.

- Stop after completion of the previous instruction and before execution of an instruction located at a preselected address.

Figure 15. Computer Control Unit Block Diagram

- Read and write the contents of any memory location or programmable register.

- Verify and/or modify parity bits in memory.

- Release or modify memory protection.

Execute the program one instruction at at time under manual control.

- Execute the program one microcommand cycle at a time under manual control.

- Inhibit all external interrupts.

- Separately inhibit RTC and timer interrupts from operating.

- Selectively dump memory contents to the L/V, a bulk storage device, or a line printer. Dumps begin at any selected memory address with no restriction on block size.

- Load and verify memory with selected blocks of data taken from the bulk storage media.

- Execute an instruction entered from the CCU without modification of the computer program counter or stored program.

- Stop at the completion of an instruction which references a preselected address.

- Load and verify computer memory from the L/V.

- Monitor and display computer diagnostic results.

Display formats can be programmed and stored into the CCU memory. Upon power up, the 8080 microprocessor will output the display format to the CRT/keyboard unit, where it is retained until power is shut down or until it is changed by the 8080 microprocessor. All of the digital information is displayed in either hexadecimal or octal notation at the operator's option. The contents of the computer registers or any memory location or block of memory locations, along with the corresponding memory address, can be selected for display on the CRT. Blocks of memory being displayed can be sequenced without preselecting a new memory location for each block.

The status of various indicators can be selected for display on the CRT. These indicators show the following switch status:

- Computer running or stopped

- I/O busy

- Machine fault

- Parity error

- Power ON/OFF

- Power fault

- Over temperature warning for computer

- Microcommand step mode